ел

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска свободных зон памяти | 1990 |

|

SU1829046A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1762320A1 |

| Устройство для поиска свободных зон памяти | 1987 |

|

SU1481851A1 |

| Устройство для управления регенерацией динамической памяти со свободными зонами | 1990 |

|

SU1739388A1 |

| Устройство для формирования адресов регенерации динамической памяти | 1989 |

|

SU1709394A1 |

| Устройство для выборки блоков памяти | 1990 |

|

SU1737457A1 |

| Модульная многоуровневая система коммутации процессоров | 1984 |

|

SU1249524A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1986 |

|

SU1388945A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Цель изобретения - повышение быстродействия устройств. Устройство содержит преобразователь кода адреса, регистр, приоритетный шифратор, коммутатор, группу элементов ИЛИ, адресные вход и выход, синхронизирующий и управляющие входы, управляющий выход и вход признаков. Адреса загружаемых и освобождаемых зон памяти фиксируются признаками, запоминаемыми в регистре. По состоянию регистра приоритетный шифратор формирует коды адресов свободных зон. Наличие группы элементов ИЛИ позволяет вести не только последовательную, но и параллельную фиксацию в регистре признаков загружаемых и освобождаемых зон. 1 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств.

Цель изобретения - повышение быстродействия устройства.

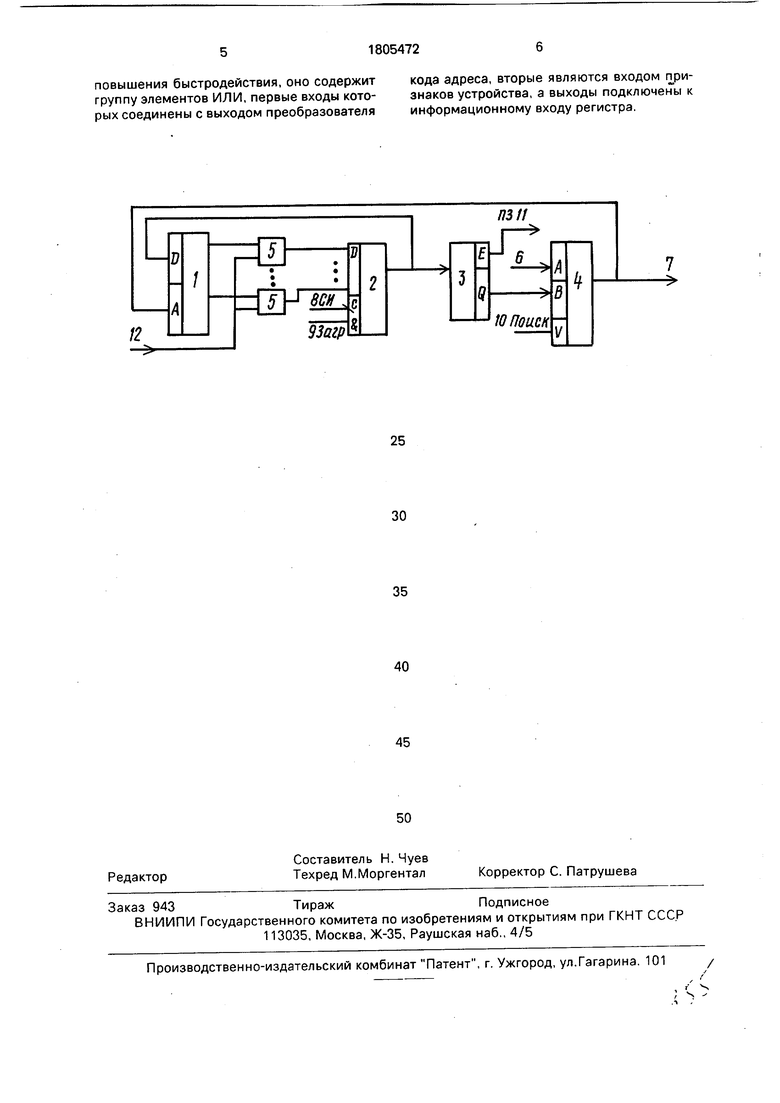

На фиг, 1 приведена функциональная схема устройства,

Устройство содержит (фиг, 1) преобразователь 1 кода адреса, регистр 2, приоритетный шифратор 3, коммутатор 4, группу элементов ИЛИ 5, адресные вход 6 и выход 7, синхровход 8, первый 9 и второй 10 управляющие входы, управляющий выход 11 и вход 12 признаков,

Вход признаков преобразователя 1 кода адреса соединен с выходом регистра 2 и входом приоритета шифратора 3, вход кода - с выходом коммутатора 4 и адресным выходом 7 устройства, а выход - с первыми входами элементов ИЛИ 5 группы, вторые

входы которых подключены по входу 12 признаков устройства, а выходы - к информационному входу регистра 2, синхровход и вход разрешения записи которого подключены, соответственно, к синхровходу 8 и первому управляющему входу 9 устройства. Выход запроса шифратора 3 подключен к управляющему выходу 11 устройства, а информационный выход - к первому информационному входу коммутатора 4, второй информационный вход которого соединен с адресным входом 6 устройства, а управляющий вход - со вторым управляющим входом 10 устройства.

Реализованный вариант заявляемого устройства предназначен для адресации зон памяти в соответствии с четырехразрядными кодами их адресов и выполнен на основе серии К555, в частности, преобразователь 1 - на К155ИДЗ и К555ПП5. регистр

2 - на К555ТМ8, шифратор 3 - на К555ИВ1, коммутатор 4 - на К555КП11.

Устройство работает следующим образом.

Совокупность управляющих сигналов на входах устройства задает различные режимы его работы.

Режим загрузки задается установкой в 1 сигнала ЗАГР на входе 9 и в О сигнала ПОИСК на входе 10. Коммутатор 4 подключен вход 6 к выходу 7. При параллельной загрузке на вход 12 поступает код признаков занятости, который устанавливается на выходах элементов ИЛИ 5 и по отрицательному фронту, сигнала СИ на входе 8 в тех разрядах регистра 2, которые соответствуют занятым зонам, устанавливается 1. При последовательной загрузке код загружаемой зоны поступает по входу 6. В преобразователе 1 из этого двоичного кода формируется унитарный код, в котором разряд, соответствующий поступившему двоичному коду, фиксируется уровнем О, а прочие разряды - уровнем 1. Этот код сравнивается в кодом признаков на выходе регистра 2. При совпадении уровня О соответствующего разряда унитарного кода, сформированного из двоичного кода на входе кода преобразователя 1 с признаками свободной зоны соответствующего разряда кода на входе признаков преобразователя 1 в этом разряде на выходе преобразователя 1 формируется признак занятости 1, в прочих же разрядах подтверждаются предыдущие состояния. Модифицированный код, поступив с выхода преобразователя 1 через элементы ИЛИ 5 по СИ устанавливается в регистре 2. При установке признака занятости в последнем из разрядов регистра 2 шифратор 3 вырабатывает сигнал запроса и на выход 11 поступает сигнал полной занятости памяти ПЗ.

В режиме обмена на выходах 9,10 установлен О. Адреса зон передаются со входа 6 через коммутатор 4 на выход 7. Изменение кода признаков в регистре 2 блокируется.

Режим очистки задается повторной установкой 1 на входе 9 и О на входе 10. При последовательной очистке на вход 6 поступает код адреса подлежащей очистке зоны, который в преобразователе 1 сравнивается с кодом признаков регистра 2. При совпадении уровня О в том разряде унитарного кода, который соответствует коду адреса очищаемой зоны, с уровнем 1 признака занятости соответствующего разряда регистра, в этом разряде на выходе преобразователя 1 устанавливается О, а в прочих разрядах на выходе преобразователя 1 подтверждаются предыдущие

состояния регистра 2. По СИ модифицированный код заносится через элементы ИЛИ 5 регистр 2 и в его соответствующем разряде признак занятости снимается. При нормальной очистке модифицированный код признаков поступает на информационный вход регистра 2 через элементы ИЛИ 5 со входа 12.

режим поиска свободной зоны задается

уровнями О на входе 9 и 1 на входе 10. Коммутатор 4 подключает ко входу кода преобразователя 1 и выходу 7 устройства информационный выход дешифратора 3. Код адреса первой из свободных зон определяется шифратором 3 по состоянию регистра 2.

В режиме поиска свободных зон с их последующей загрузкой сигнал ПОИСК дополняется сигналом ЗАГР. Признаки занятости устанавливаются в регистре 2 в соответствии с кодом на информационном выходе шифратора 3 аналогично работе в режиме загрузки. По СИ в регистр 2 заносится новое состояние на выходе преобразователя 1 и шифратор 3 формирует код очередной свободной зоны.

Таким образом, устройство фиксирует адреса свободных зон и осуществляет их приоритетный поиск. При этом, если в устройстве-прототипе осуществляются лишь последовательные загрузка и очистка зон памяти, то в предлагаемом устройстве возможна и параллельная фиксация зон, что при адресации шестнадцати зон в реализованном варианте предлагаемого устройства составит выигрыш в быстродействии максимум в 16 раз при работе в указанных режимах.

Формул а изобретения

Устройство для адресации памяти, содержащее преобразователь кода адреса, регистр, приоритетный шифратор и коммутатор, выход которого является адресным

выходом устройства и подключен к входу кода преобразователя кода, вход признаков которого соединен с входом приоритетного шифратора и выходом регистра, синхров- ход которого является соответствующим

входом устройства, а вход разрешения записи - первым управляющим входом устройства, выход запроса шифратора является управляющим выходом устройства, а информационный выход шифратора

подключен к первому информационному входу коммутатора, второй информационный вход которого является адресным входом устройства, а управляющий вход - вторым управляющим входом устройства, отличающееся тем. что, с целью

повышения быстродействия, оно содержит группу элементов ИЛИ, первые входы которых соединены с выходом преобразователя

кода адреса, вторые являются входом признаков устройства, а выходы подключены к информационному входу регистра.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для выбора свободных зон в памяти | 1981 |

|

SU980159A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для поиска свободных зон памяти | 1987 |

|

SU1481851A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1993-03-30—Публикация

1990-10-31—Подача