Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств.

Целью изобретения является повышение быстродействия устройства.

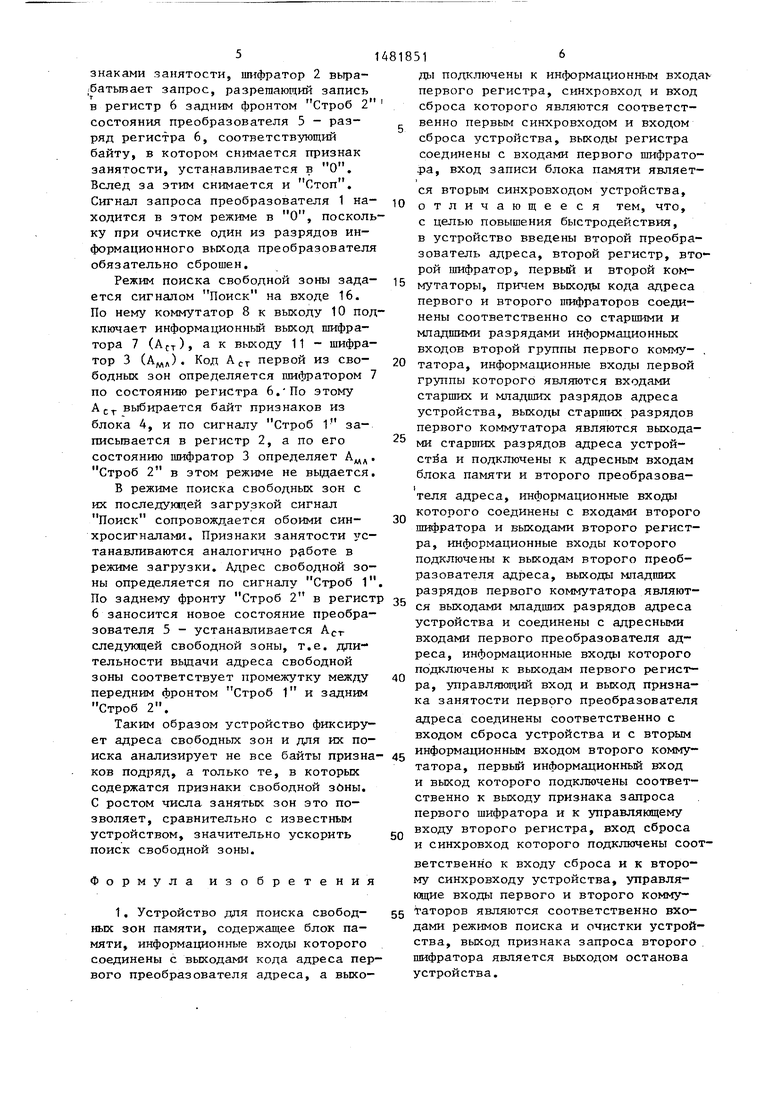

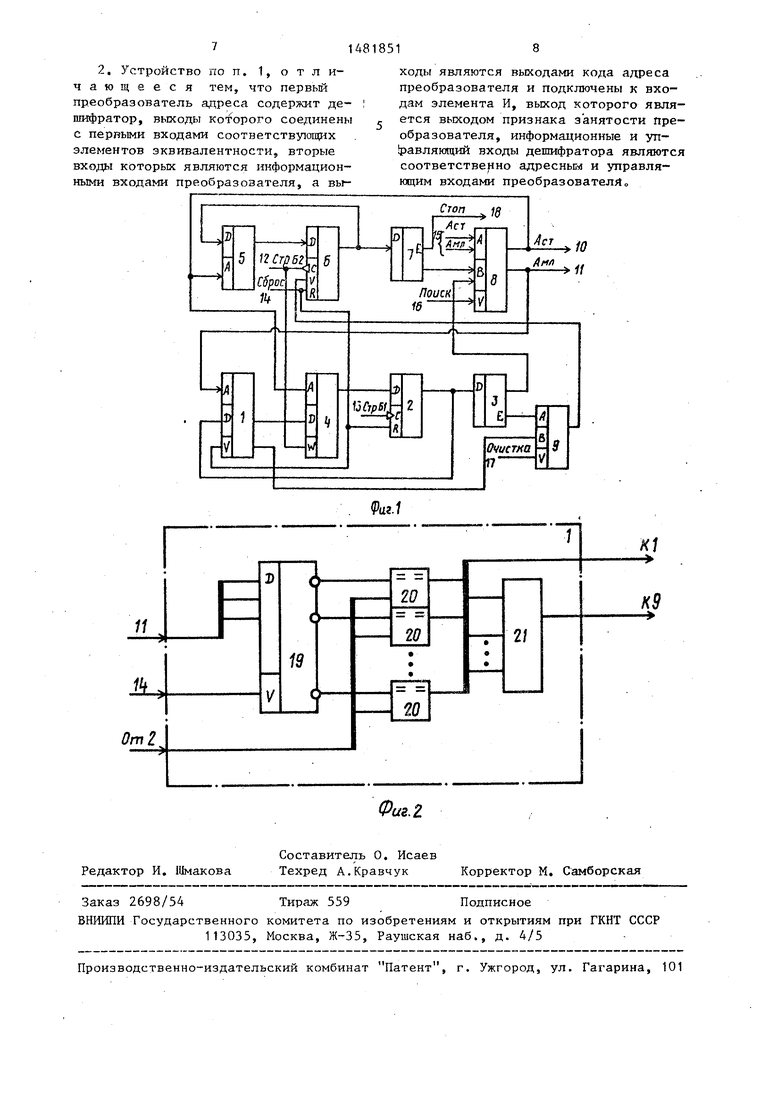

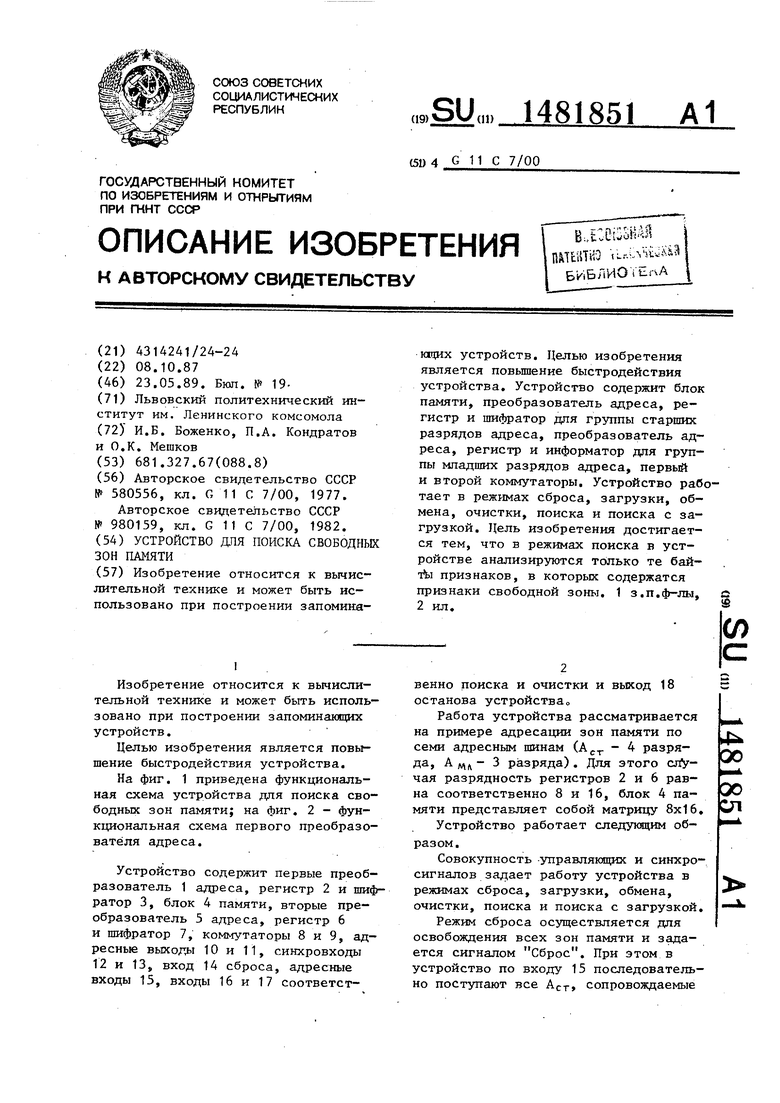

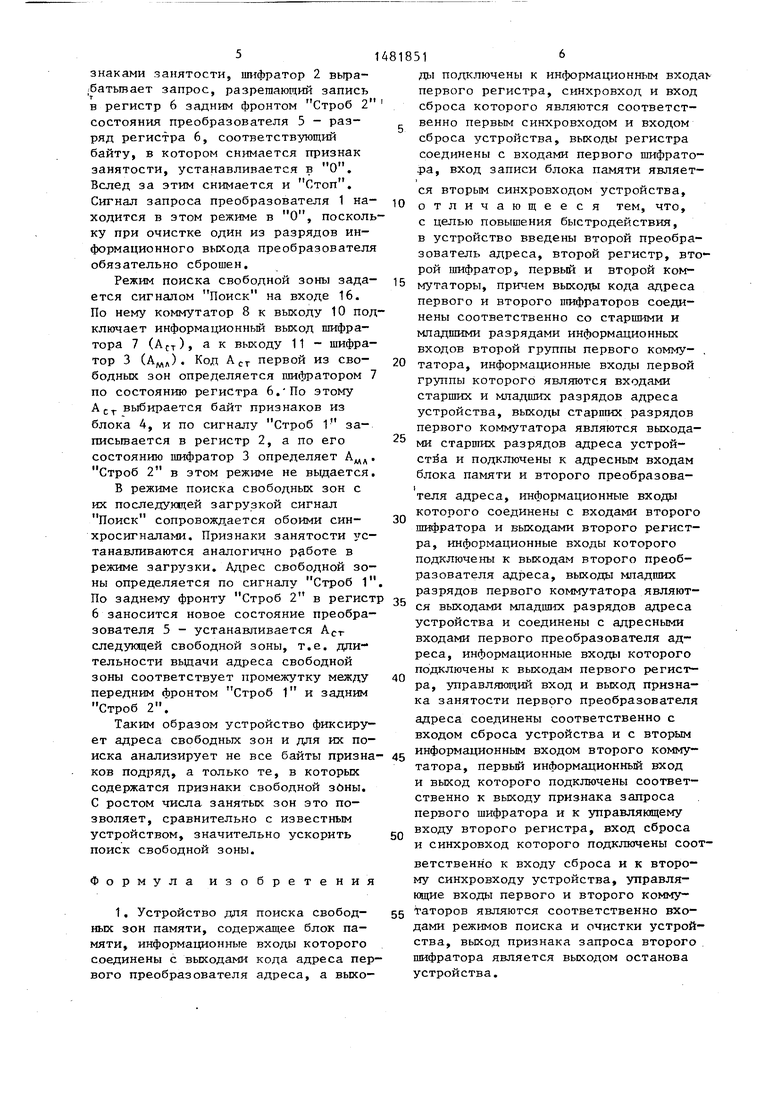

На фиг. 1 приведена функциональная схема устройства для поиска свободных зон памяти; на фиг. 2 - функциональная схема первого преобразователя адреса.

Устройство содержит первые преобразователь 1 адреса, регистр 2 и шифратор 3, блок 4 памяти, вторые преобразователь 5 адреса, регистр 6 и шифратор 7, коммутаторы 8 и 9, адресные выходы 10 и 11, синхровходы 12 и 13, вход 14 сброса, адресные входы 15, входы 16 и 17 соответственно поиска и очистки и выход 18 останова устройства

Работа устройства рассматривается на примере адресации зон памяти по семи адресным шинам (Аст - 4 разряда, А Мл- 3 разряда). Для этого случая разрядность регистров 2 и 6 равна соответственно 8 и 16, блок 4 памяти представляет собой матрицу 8x16.

Устройство работает следующим образом.

Совокупность управляющих и синхросигналов задает работу устройства в режимах сброса, загрузки, обмена, очистки, поиска и поиска с загрузкой.

Режим сброса осуществляется для освобождения всех зон памяти и задается сигналом Сброс. При этом в устройство по входу 15 последовательно поступают все Аст, сопровождаемые

ас

оо ел

сигналом Строб 2. По сигналу Сброс все разряды регистров 2 и 6 устанавливаются в состояние логического О, а выходы дешифратора 19 преобразователя 1 - в 1. При наличии этих уровней на соответствующих входах элементов 20 эквивалентности преобразователя 1 на их выходах устанавливается О, который и записыва- JQ ется по всем адресам блока 4 памяти. Эти адреса задаются сигналами Аст, которые с входа 15 через коммутатор 8 поступают на адресный вход блока 4.

В результате во всех разрядах 15 всех байтов, хранящихся в блоке 4, и во всех разрядах второго регистра 6, разрядность которого соответствует количеству этих байтов, сбрасываются признаки занятости.20

В режиме загрузки процессор загружает информацией определенные зоны памяти. Режим задается уровнем О на входах 14, 16 и 17 сброса и упвается 1 , срабатывает эл и 1 через коммутатор 9 п на разрешающий вход регист решая запись в него по зад ту. Строб 2 выходного сос преобразователя 5, которое ся аналогично работе преоб ля 1. Так при полном запол деленного байта признаками ти дополнительный признак устанавливается в соответс этому байту разряда регист

При загрузке последней ных зон (код 1111111) уста ется дополнительный призна ти в последнем из разрядов ра 6, шифратор 7 выставляе запроса, на выход 18 устро ступает сигнал Стоп, соо отсутствии свободных зоНо тах, хранящихся в блоке 4, ся признаки занятости зон, гистре 6 отмечаются байты,

равления и синхросигналами Строб 1, 25 занятые этими признаками. Строб 2, сопровождающими поступление Аст и Аж. По Аст из блока 4 выбирается соответствующий ему байт признаков и устанавливается в О соответствующий разряд дешифратора 19 30 второго преобразователя 5. По Ам„ устанавливается в О соответствующий ему разряд дешифратора 19 первого преобразователя 1. По Строб 1 байт,

В режиме обмена информа цессора с загруженными зон с входа 15 через коммутато выходы 10 и 11 передаются АМА о При этом они не сопр ся сигналами управления и ции.

В режиме очистки процес бождает от загрузки опреде зоны памяти, и в устройств сируется. Режим задается у сигнала Очистка на входе му на выход коммутатора 9 сигнала запроса преобразов подключается сигнал запрос ра 3, формируемый по состо гистра 2 о Задание Аст, АМ дается синхросигналами Ст Строб 2. По Аст из блока ется соответствующий ему б рый заносится по Строб 1 в Устанавливаются в О разр тора 19 преобразователя 5 ствующий. Аст , и разряд деш преобразователя 1, соответ Аддл. При совпадении уровня шифратора с уровнем 1 пр занятости соответствующий . устанавливает О на своем 55 и он по Строб 2 заноситс памяти. На выходах прочих 20 сохраняется предыдущее Если регистр 2 полностью з

выбранный из блока 4 по Агт, записы

вается в первый регистр 2. При совпадении в элементе 20 уровней О с дешифратора 19 с признаком свободной зоны, также уровня О и поступающим с регистра, на выходе элемента 20 формируется признак занятости уровня 1, который и записывается в блок 4 по Строб 2. Поскольку прочие разряды дешифратора 19 - в состоянии 1, то при совпадении его с уровнем О на выходе элемента 20 устанавливается О, а при совпадении с 1 устанавливается 1 - и в прочих разрядах байта подтверждаются ранее установленные признаки.

При установке в байте последнего признака занятости для кода адреса зоны, например, 0000111 устанавливается в О 8-й разряд дешифратора 19 преобразователя 1. По Строб 1 в регистр 2 заносится состояние, установившееся по предыдущей загрузке. В результате на выходах всех элементов 20 преобразователя 1 устанавли

вается 1 , срабатывает элемент И 21 и 1 через коммутатор 9 поступает на разрешающий вход регистра 6, разрешая запись в него по заднему фронту. Строб 2 выходного состояния преобразователя 5, которое формируется аналогично работе преобразователя 1. Так при полном заполнении определенного байта признаками занятости дополнительный признак занятости устанавливается в соответствующем этому байту разряда регистра 6.

При загрузке последней из свободных зон (код 1111111) устанавливается дополнительный признак занятости в последнем из разрядов регистра 6, шифратор 7 выставляет сигнал запроса, на выход 18 устройства поступает сигнал Стоп, сообщающий об отсутствии свободных зоНо Так в байтах, хранящихся в блоке 4, фиксируются признаки занятости зон, а в регистре 6 отмечаются байты, полностью

занятые этими признаками. 0

5

5

о

В режиме обмена информацией процессора с загруженными зонами памяти с входа 15 через коммутатор 8 на выходы 10 и 11 передаются коды Аст, АМА о При этом они не сопровождаются сигналами управления и синхрониэа-Т ;. ции.

В режиме очистки процессор освобождает от загрузки определенные зоны памяти, и в устройстве это фиксируется. Режим задается установкой сигнала Очистка на входе 17. По нему на выход коммутатора 9 вместо сигнала запроса преобразователя 1 подключается сигнал запроса шифратора 3, формируемый по состоянию регистра 2 о Задание Аст, АМА сопровождается синхросигналами Строб 1, Строб 2. По Аст из блока 4 выбирается соответствующий ему байт, который заносится по Строб 1 в регистр 2. Устанавливаются в О разряд дешифратора 19 преобразователя 5, соответствующий. Аст , и разряд дешифратора преобразователя 1, соответствующий Аддл. При совпадении уровня О с дешифратора с уровнем 1 признака занятости соответствующий элемент 20 . устанавливает О на своем выходе, 5 и он по Строб 2 заносится в блок 4 памяти. На выходах прочих элементов 20 сохраняется предыдущее состояние. Если регистр 2 полностью занят при-

знаками занятости, шифратор 2 вьтра- .батывает запрос, разрешающий запись в регистр 6 задним фронтом Строб 2 состояния преобразователя 5 - разряд регистра 6, соответствующий байту, в котором снимается признак занятости, устанавливается в О. Вслед за этим снимается и Стоп. Сигнал запроса преобразователя 1 на- ходится в этом режиме в О, поскольку при очистке один из разрядов информационного выхода преобразователя обязательно сброшен.

Режим поиска свободной зоны зада- ется сигналом Поиск на входе 16. По нему коммутатор 8 к выходу 10 подключает информационный выход шифратора 7 (Аст), а к выходу 11 - шифратор 3 (Амя). Код Асг первой из сво- бодных зон определяется шифратором 7 по состоянию регистра 6. По этому

СТ

выбирается байт признаков из

блока 4, и по сигналу Строб 1 записывается в регистр 2, а по его состоянию шифратор 3 определяет АМЛ. Строб 2 в этом режиме не выдается.

В режиме поиска свободных зон с их последующей загрузкой сигнал Поиск сопровождается обоими син- хросигналами. Признаки занятости устанавливаются аналогично работе в режиме загрузки. Адрес свободной зоны определяется по сигналу Строб 1 По заднему фронту Строб 2 в регист 6 заносится новое состояние преобразователя 5 - устанавливается Act- следующей свободной зоны, т.е. длительности выдачи адреса свободной зоны соответствует промежутку между передним фронтом Строб 1 и задним Строб 2.

Таким образом устройство фиксирует адреса свободных зон и для их поиска анализирует не все байты призна ков подряд, а только те, в которых содержатся признаки свободной зоны. С ростом числа занятых зон это позволяет, сравнительно с известным устройством, значительно ускорить поиск свободной зоны.

Формула изобретения

1. Устройство для поиска свобод- ных зон памяти, содержащее блок памяти, информационные входы которого соединены с выходами кода адреса первого преобразователя адреса, а выходы подключены к информационным входа первого регистра, синхровход и вход сброса которого являются соответственно первым синхровходом и входом сброса устройства, выходы регистра соединены с входами первого шифратора, вход записи блока памяти является вторым синхровходом устройства, отличающееся тем, что, с целью повышения быстродействия, в устройство введены второй преобразователь адреса, второй регистр, второй шифратор, первый и второй коммутаторы, причем выходы кода адреса первого и второго шифраторов соединены соответственно со старшими и младшими разрядами информационных входов второй группы первого коммутатора, информационные входы первой группы которого являются входами старших и младших разрядов адреса устройства, выходы старших разрядов первого коммутатора являются выходами старших разрядов адреса устройства и подключены к адресным входам блока памяти и второго преобразователя адреса, информационные входы которого соединены с входами второго шифратора и выходами второго регистра, информационные входы которого подключены к выходам второго преобразователя адреса, выходы младших разрядов первого коммутатора являются выходами младших разрядов адреса устройства и соединены с адресными входами первого преобразователя адреса, информационные входы которого подключены к выходам первого регистра, управляющий вход и выход признака занятости первого преобразователя адреса соединены соответственно с входом сброса устройства и с вторым информационным входом второго коммутатора, первьй информационный вход и выход которого подключены соответственно к выходу признака запроса первого шифратора и к управляющему входу второго регистра, вход сброса и синхровход которого подключены соответственно к входу сброса и к второму синхровходу устройства, управляющие входы первого и второго коммутаторов являются соответственно входами режимов поиска и очистки устройства, выход признака запроса второго шифратора является выходом останова устройства.

2. Устройство по п. 1, отличающееся тем, что первый преобразователь адреса содержит дешифратор, выходы которого соединены с пергшми входами соответствующих элементов эквивалентности, вторые входы которых являются информационными входами преобразователя, а выходы являются выходами кода адреса преобразователя и подключены к входам элемента И, выход которого является выходом признака занятости преобразователя, информационные и управляющий входы дешифратора являются соответственно адресным и управляющим входами преобразователи

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска свободных зон памяти | 1990 |

|

SU1829046A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для регенерации динамической памяти | 1988 |

|

SU1587594A1 |

| Устройство для сортировки данных | 1990 |

|

SU1784967A1 |

| Устройство для адресации памяти | 1990 |

|

SU1805472A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств. Целью изобретения является повышение быстродействия устройства. Устройство содержит блок памяти, преобразователь адреса, регистр и шифратор для группы старших разрядов адреса, преобразователь адреса, регистр и информатор для группы младших разрядов адреса, первый и второй коммутаторы. Устройство работает в режимах сброса, загрузки, обмена очистки, поиска и поиска с загрузкой. Цель изобретения достигается тем, что в режимах поиска в устройстве анализируются только те байты признаков, в которых содержатся признаки свободной зоны. 1 З.п.ф-лы, 2 ил.

| Устройство для распределения памяти | 1976 |

|

SU580556A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для выбора свободных зон в памяти | 1981 |

|

SU980159A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-05-23—Публикация

1987-10-08—Подача