Изобретение относится к радиоэлектронике и может быть использовано в высокоточных аналого-цифровых, преобразователях..;..-Цель изобретения -увеличение быстродействия за счет исключения влияния задержки входного каскада.

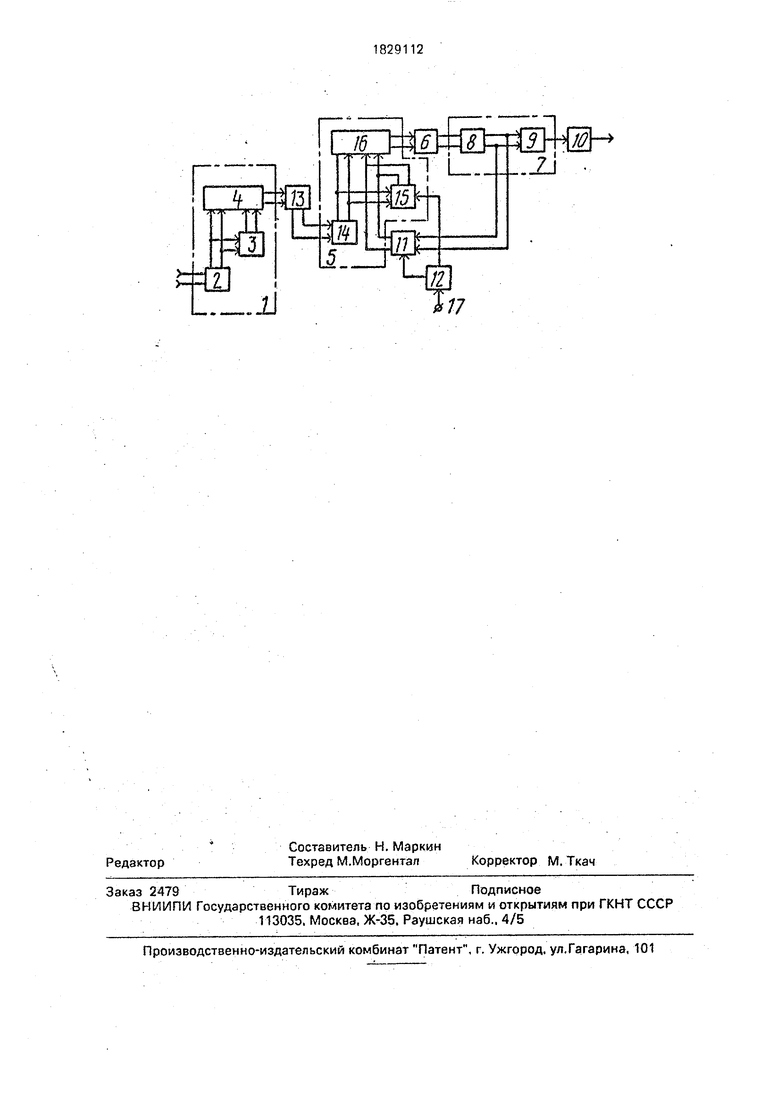

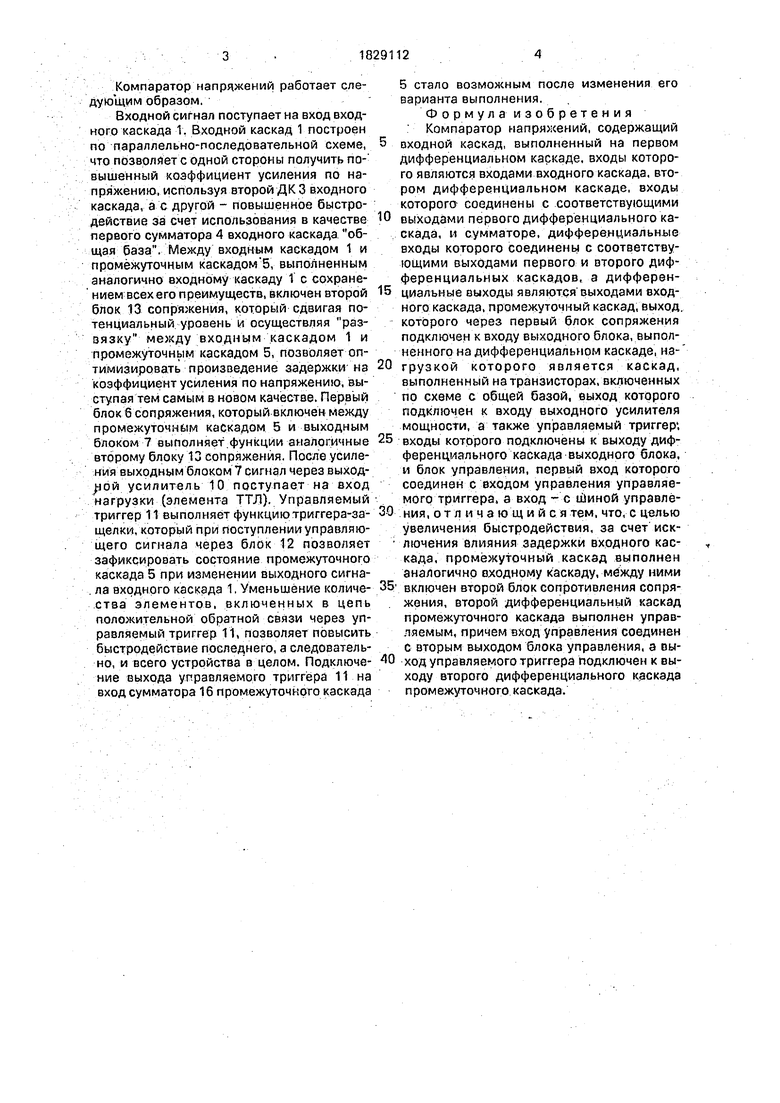

На чертеже представлена структурная схема компаратора напряжений.

Компаратор напряжений содержит входной каскад 1, выполненный на первом дифференциальном каскаде (ДК) 2, втором ДК 3 и сумматоре 4, промежуточный каскад 5, первый блок 6 сопряжения (БС), выходной блок 7, выполненный на дифференциальном каскаде 8, нагрузкой которого является каскад 9, выполненный на транзисторах, включенных по схеме с общей базой, выходной усилитель 10 мощности, управляемый триггер 11, блок 12 управления и второй блок 13 сопряжения, причем промежуточный каскад

5выполнен на первом ДК 14 промежуточного каскада, втором ДК 15 промежуточного каскада и сумматоре 16 промежуточного каскада, а также шину 17 управления, причем входной каскад 1, второй блок 13 сопряжения, промежуточный каскад 5. первый блок

6сопряжения, выходной блок 7 и выходной усилитель 10 соединены последовательно, входы управляемого триггера 11 подключены к выходу дифференциального каскада 8 выходного блока 7, первый вход блока 12 управления соединен со входом управления управляемого триггера 11, а вход - с шиной 17 управления, а выход управляемого триггера 11 подключен к выходу второго дифференциального каскада 15 промежуточного каскада 5.

К

ю

ю

Компаратор напряжений работает следующим образом.

Входной сигнал поступает на вход входного каскада 1. Входной каскад 1 построен по параллельно-последовательной схеме, что позволяете одной стороны получить по- вышенный коэффициент усиления по напряжению, используя второй ДК 3 входного каскада, а с другой - повышенное быстродействие за счет использования в качестве первого сумматора 4 входного каскада общая база. Между входным каскадом 1 и промежуточным каекадом 5, выполненным аналогично входному каскаду 1 с сохранением всехего преимуществ, включен второй блок 13 сопряжения, который сдвигая потенциальный уровень и осуществляя развязку между входным каскадом 1 и промежуточным каскадом 5, позволяет оптимизировать произведение задержки на коэффициент усиления по напряжению, выступая тем самым в новом качестве. Первый блок б сопряжения, который включен между промежуточным каскадом 5 и выходным блоком 7 выполняет .функции аналогичные второму блоку 13 сопряжения. После усиления выходным блоком 7 сигнал через выход- рой усилитель 10 поступает на вход нагрузки (элемента ТТЛ). Управляемый триггер 1Т выполняет функцию триггера-защелки, который при поступлении управляющего сигнала через блок 12 позволяет зафиксировать состояние промежуточного каскада 5 при изменении выходного сигна- . ла входного каскада 1. Уменьшение количества элементов, включенных в цепь положительной обратной связи через управляемый триггер 11, позволяет повысить быстродействие последнего, а следовательно, и всего устройства в целом. Подключение выхода управляемого триггера 11 на вход сумматора 16 промежуточного каскада

5 стало возможным после изменения его варианта выполнения. .

Формул а изобретения Компаратор напряжений, содержащий

входной каскад, выполненный на первом дифференциальном каскаде, входы которого являются входами входного каскада, втором дифференциальном каскаде, входы которого соединены с соответствующими

выходами первого дифференциального каскада, и сумматоре, дифференциальные входы которого соединены с соответствующими выходами первого и второго дифференциальных каскадов, а дифференциальные выходы являются выходами входного каскада, промежуточный каскад, выход, которого через первый блок сопряжения подключен к входу выходного блока, выполненного на дифференциальном каскаде, на-

грузкой которого является каскад, выполненный на транзисторах, включенных по схеме с общей базой, выход которого подключен к входу выходного усилителя мощности, а также управляемый триггер1,

входы которого подключены к выходу дифференциального каскада выходного блока, и блок управления, первый вход которого соединен с входом управления управляемого триггера, а вход -с шиной управлёкия .отличающий с я тем, что, с целью увеличения быстродействия, за счет иск- лючения влияния задержки входного каскада, промежуточный каскад выполнен аналогично входному каскаду, между ними

включен второй блок сопротивления сопря- жения, второй дифференциальный каскад промежуточного каскада выполнен управляемым, причем вход управления соединен С вторым выходом блока управления, а выход управляемого триггера подключен к выходу второго дифференциального каскада промежуточного каскада.

| название | год | авторы | номер документа |

|---|---|---|---|

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

| Устройство для моделирования оптимальной системы управления | 1984 |

|

SU1254432A1 |

| Цифроаналоговый преобразователь | 1983 |

|

SU1152091A1 |

| Логарифмический преобразователь напряжения в двоичный код | 1989 |

|

SU1709523A1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ УСИЛЕНИЕМ | 2008 |

|

RU2384937C1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU938396A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

Изобретение относится к радиоэлектроника и может быть использовано в высокоточных аналого-цифровых преобразователях. Цель - увеличение быстродействия. Компаратор напряжений содержит входной каскад 1, выполненный на первом дифференциальном каскаде (ДК) 2, втором ДК 3 и сумматоре 4, промежуточный каскад 5, первый блок б сопряжения (БС), выходной блок 7, выполненный на дифференциальном каскаде 8 и каскаде 9, выходной усилитель 10 мощности, управляемый триггер 11, блок 12 управления и второй блок 13 сопряжения, промежуточный каскад 5, выполненный на первом ДК 14. втором ДК 15 и сумматоре 16, и шину 17 управления. Повышение быстродействия обусловлено исключением влияния задержки входного каскада и уменьшением количества элементов, включенных в цепь положительной обратной связи через управляемый триггер 11.,;1 ил. N1 И

| Linear Integrated Circuits Data book, f | |||

| Raythcov, V.C.RC4 805, p | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| New Jearsey, 1986. | |||

Авторы

Даты

1993-07-23—Публикация

1990-03-07—Подача