зобретение относится.к области проводимой связи и предназначено к использованию в линейных трактах волоконно-оптических систем передачи (ВОСП) цифровой информации.

,ель изобретения - повышение помехоустойчивости и расширение области приме- нени ) кодера за счет возможности передачи в сиг 1але дополнительной информации.

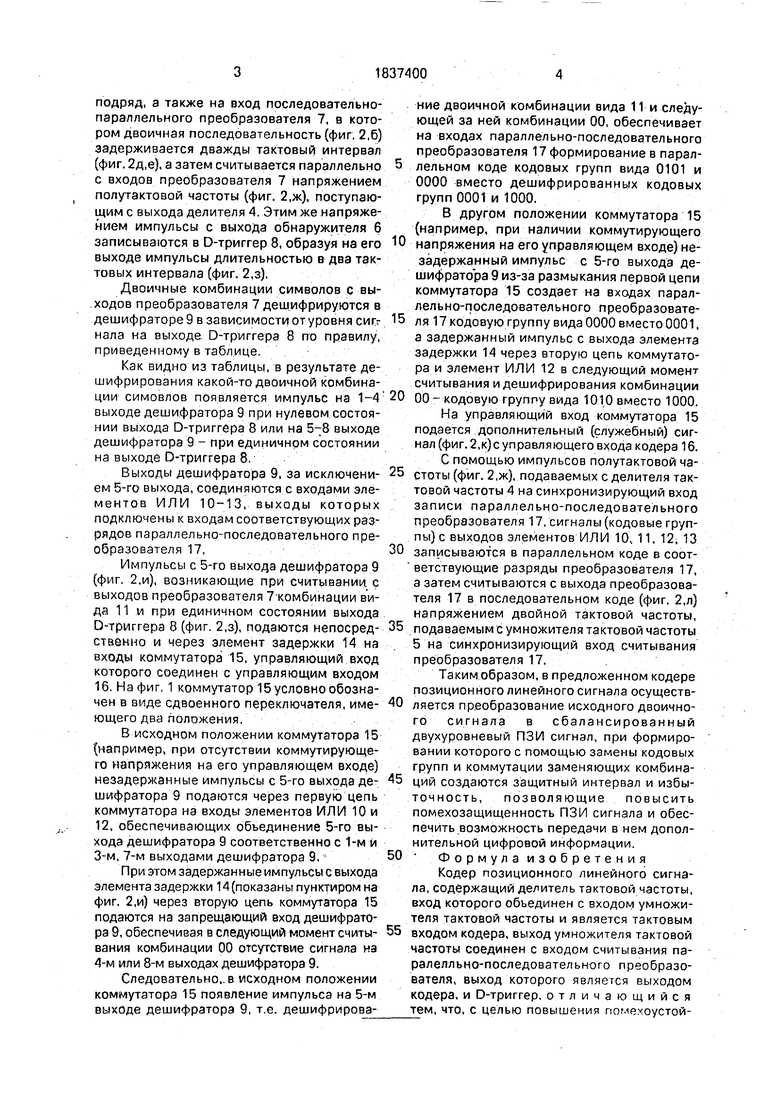

с ункциональная схема кодера позици- онно о линейного сигнала f .риведена на фиг. 1; временные диаграммы, поясняющие его

рабо- лине

у,- на фиг. 2; энергетические спектры ных ПНР-и ПЗИ-сигналов, полученных

соответственно в устройстве-прототипе и в пред/ оженном кодере,- на фиг. 3.

а фиг. 1 обозначены: информационный ф«эд 1 кодера, регистр сдвига 2, тактовый рсод 3 кодера, делитель 4 тактовой частоты, умножитель 5 тактовой частоты, селектор 6 комбинации двоичных символов, последовательно-параллельный преобразователь 7, D-триггер 8, дешифратор 9, элемент ИЛИ 10-13, элемент задержки 14,

коммутатор 15, управляющий вход 16 кодера, параллельно-последовательный преобразователь 17; на фиг-2-t - текущее время, Т - тактовый интервал, Тп - позиционный интервал; на фиг.3-5(т) - тактовая частота, fr - энергетический спектр.

Кодер позиционного линейного сигнала работает следующим образом.

Исходный двоичный сигнал с информационного входа 1 (фиг. 1) подается на регистр сдвига 2, в котором сигнал фазируется (фиг. 2,а) и сдвигается (фиг. 2,6) напряжением тактовой частоты (фиг. 2,в), поступающим с тактового входа 3. Напряжение тактовой частоты с входа 3,кроме того,подается на входы делителя 4 и умножителя 5 тактовой частоты, а также на вход записи последовательно-параллельного преобразователя 7.

Сигналы с входов регистра сдвига 2 подаются на входы обнаружителя комбинации двоичных символов 6, формирующего на его выходе импульсы (фиг. 2,г) при появлении в двоичном сигнале двух пробелов

со

СА) Ч О

О

подряд, а также на вход последовательно- параллельного преобразователя 7, в котором двоичная последовательность (фиг. 2,6) задерживается дважды тактовый интервал (фиг. 2д,е), а затем считывается параллельно с входов преобразователя 7 напряжением полутактовой частоты (фиг. 2,ж), поступающим с выхода делителя 4. Этим же напряжением импульсы с выхода обнаружителя 6 записываются в D-триггер 8, образуя на его выходе импульсы длительностью в два тактовых интервала (фиг. 2,з).

Двоичные комбинации символов с выходов преобразователя 7 дешифрируются в дешифраторе 9 в зависимости от уровня сигг нала на выходе D-триггера 8 по правилу, приведенному в таблице.

Как видно из таблицы, в результате дешифрирования какой-то двоичной комбинации симовлов появляется импульс на 1-4 выходе дешифратора 9 при нулевом состоянии выхода D-триггера 8 или на 5-8 выходе дешифратора 9 - при единичном состоянии на выходе D-триггера 8.

Выходы дешифратора 9, за исключени- ем 5-го выхода, соединяются с входами элементов ИЛИ 10-13, выходы которых подключены к входам соответствующих разрядов параллельно-последовательного преобразователя 17.

Импульсы с 5-го выхода дешифратора 9 (фиг. 2,и), возникающие при считывании, с выходов преобразователя 7 комбинации вида 11 м при единичном состоянии выхода D-триггера 8 (фиг. 2,з), подаются непосред- ственно и через элемент задержки 14 на входы коммутатора 15, управляющий вход которого соединен с управляющим входом 16, На фиг, 1 коммутатор 15 условно обозначен в виде сдвоенного переключателя, име- ющего два положения.

В исходном положении коммутатора 15 (например, при отсутствии коммутирующего напряжения на его управляющем входе) незадержанные импульсы с 5-го выхода де- шифратора 9 подаются через первую цепь коммутатора на входы элементов ИЛИ 10 и 12, обеспечивающих объединение 5-го выхода дешифратора 9 соответственно с 1-м и 3-м, 7-м выходами дешифратора 9.

При этом задержанные импульсы с выхода элемента задержки 14(показаны пунктиром на фиг. 2,и) через вторую цепь коммутатора 15 подаются на запрещающий вход дешифратора 9, обеспечивая в следующий момент считы- вания комбинации 00 отсутствие сигнала на 4-м или 8-м выходах дешифратора 9.

Следовательно, в исходном положении коммутатора 15 появление импульса на 5-м выходе дешифратора 9, т.е. дешифрирование двоичной комбинации вида 11 и следующей за ней комбинации 00, обеспечивает на входах параллельно-последовательного преобразователя 17 формирование в параллельном коде кодовых групп вида 0101 и 0000 вместо дешифрированных кодовых групп 0001 и 1000.

В другом положении коммутатора 15 (например, при наличии коммутирующего напряжения на его управляющем входе) незадержанный импульс с 5-го выхода дешифратора 9 из-за размыкания первой цепи коммутатора 15 создает на входах параллельно-последовательного преобразователя 17 кодовую группу вида 0000 вместо 0001, а задержанный импульс с выхода элемента задержки 14 через вторую цепь коммутатора и элемент ИЛИ 12 в следующий момент считывания и дешифрирования комбинации 00- кодовую группу вида 1010 вместо 1000.

На управляющий вход коммутатора 15 подается дополнительный (служебный) сигнал (фиг. 2,к)с управляющего входа кодера 16.

С помощью импульсов полутактовой частоты (фиг. 2,ж), подаваемых с делителя тактовой частоты 4 на синхронизирующий вход записи параллельно-последовательного преобразователя 17, сигналы (кодовые группы) с выходов элементов ИЛИ 10V 11, 12, 13 записываются в параллельном коде в соответствующие разряды преобразователя 17, а затем считываются с выхода преобразователя 17 в последовательном коде (фиг. 2,л) напряжением двойной тактовой частоты, подаваемым с умножителя тактовой частоты 5 на синхронизирующий вход считывания преобразователя 17.

Таким образом, в предложенном кодере позиционного линейного сигнала осуществляется преобразование исходного двоичного сигнала в сбалансированный двухуровневый ПЗИ сигнал, при формировании которого с помощью замены кодовых групп и коммутации заменяющих комбинаций создаются защитный интервал и избыточность, позволяющие повысить помехозащищенность ПЗИ сигнала и обеспечить возможность передачи в нем дополнительной цифровой информации.

Ф о р м у л а и з о б р е т е н и я

Кодер позиционного линейного сигнала, содержащий делитель тактовой частоты, вход которого объединен с входом умножителя тактовой частоты и является тактовым входом кодера, выход умножителя тактовой частоты соединен с входом считывания па- ралелльно-последовательного преобразователя, выход которого является выходом кодера, и D-триггер, отличающийся тем, что, с целью повышения помеу0устойчивости и расширения области применения за счет передачи в сигнале дополнительной информации, в кодер введены регистр сдвига, селектор комбинации двоичных символов, деиифратор, последовательно-пэраляель- ный преобразователь, коммутатор, элемент задержки и элемент ИЛИ, выходы которых сое, ;инены с соответствующими информаци- онными входами параллельно-последова- тел| ного преобразователя, информационный вхо i регистра сдвига является информацион- ныл входом кодера, синхронизирующий вход регистра сдвига и вход записи последова- тел .но-лараллельного преобразователя под- клкчены к тактовому входу кодера, первый вых эд регистра сдвига соединен с первым входов селектора комбинации двоичных симво- ЛОЕ , выход которого соединен с ормационным входом D-триггера, второй выход регистра сдвига соединен с вторым вхоцом селектора комбинации двоичных символов и с информационным входом последовательно-параллельного преобразо- ват ;ля, выходы которого и выход Ь-триггера соединены с соответствующими информа-

ционными входами дешифратора, выход делителя тактовой частоты соединен с входом записи параллельно-последовательного преобразователя, с входом считывания по- сгедовательно-параллельного преобразователя и с синхровходом D-триггера. первый-четвертый выходы дешифратора соединены с первыми входами соответственно первого-четвертого элементов ИЛИ, пятый вход дешифратора соединен непосредственно и через элемент задержки соот- ветственно с первым и вторым информационными входами коммутатора, управляющий вход которого является управляющим входом кодера, шестой- восьмой выходы дешифратора соединены с вторыми входами соответственно

второго-четвертого элементов ИЛИ. первый выход коммутатора соединен с третьим входом второго элемента ИЛИ, второй выход коммутатора соединен с вторым входом первого и третьим входом третьего элементов ИЛИ, третий выход коммутатора соединен с запрещающим входом дешифратора.

фиг

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| СЕЛЕКТОР ИМПУЛЬСОВ ЗАДАННОЙ КОДОВОЙ КОМБИНАЦИИ | 1994 |

|

RU2076455C1 |

| Система передачи и приема информации с многоосновным кодированием | 1989 |

|

SU1642590A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| Кодер кода 3В2 @ | 1984 |

|

SU1244803A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Автоматическая система единогоВРЕМЕНи | 1979 |

|

SU847262A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ КОДОМ ПЕРЕМЕННОЙ ДЛИНЫ | 1996 |

|

RU2123765C1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ МАГНИТНОЙ ЗАПИСИ ИНФОРМАЦИИ НА ВИДЕОМАГНИТОФОНЕ | 1993 |

|

RU2042218C1 |

Кодер позиционного линейного сигнала относится к технике проводной связи и может использоваться в линейных трактах во- локрнно-оптических систем передачи цифровой информации. Цель изобретения - повышение помехоустойчивости и расширение области применения кодера за счет возможности передачи в сигнале дополнительной информации. Кодер содержит регистр сдвига, делитель тактовой частоты, умножитель тактовой частоты, селектор комбинации двоичных сигналов, последовательно- параллельный преобразователь, D- триггер, дешифратор, элементы ИЛИ 10-13, элемент задержки, коммутатор, параллельно-последовательный преобразователь, информационный вход, тактовый вход, управляющий вход кодера. 3 ил., 1 табл.

йзиг.2

Н

| JT.Le Hiepand etw, Journal of Optical Communications, v | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР Мг 1403972, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-08-30—Публикация

1990-01-08—Подача