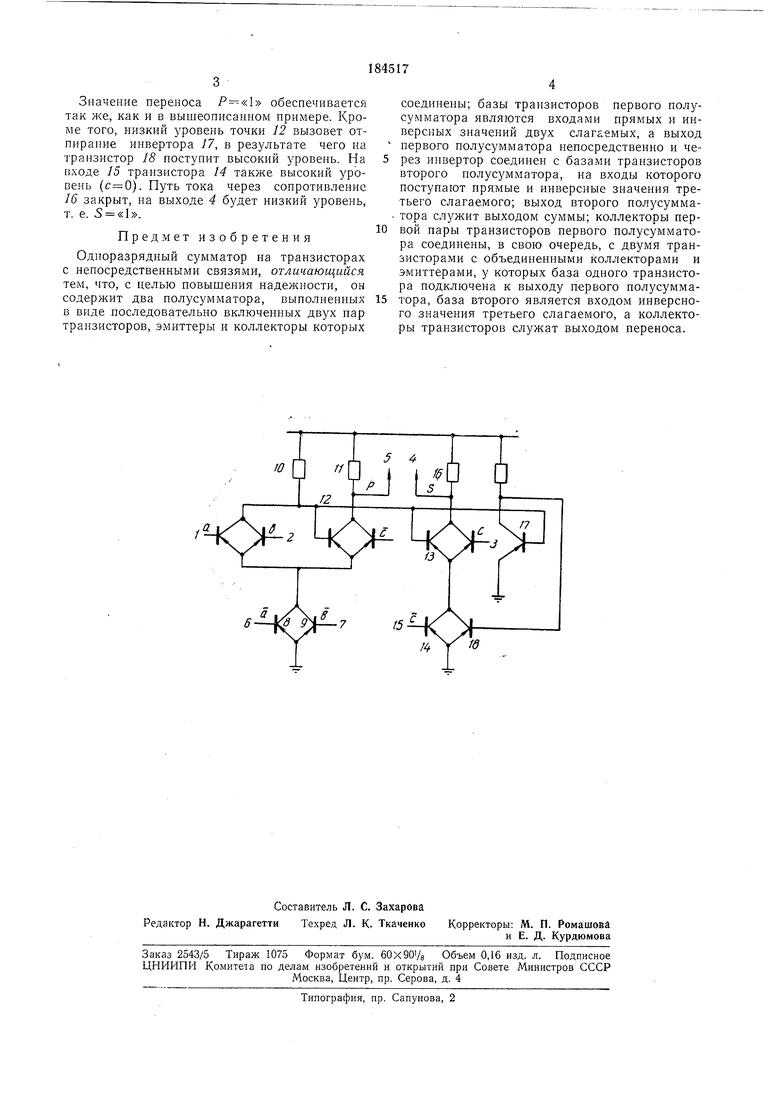

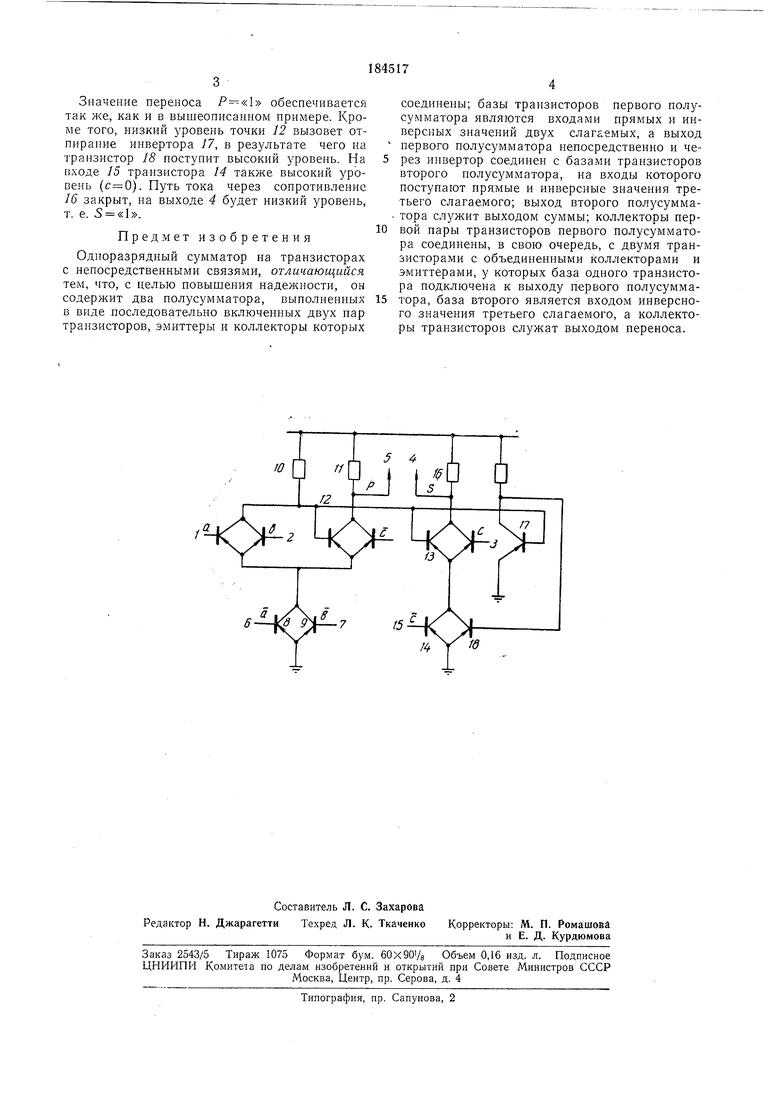

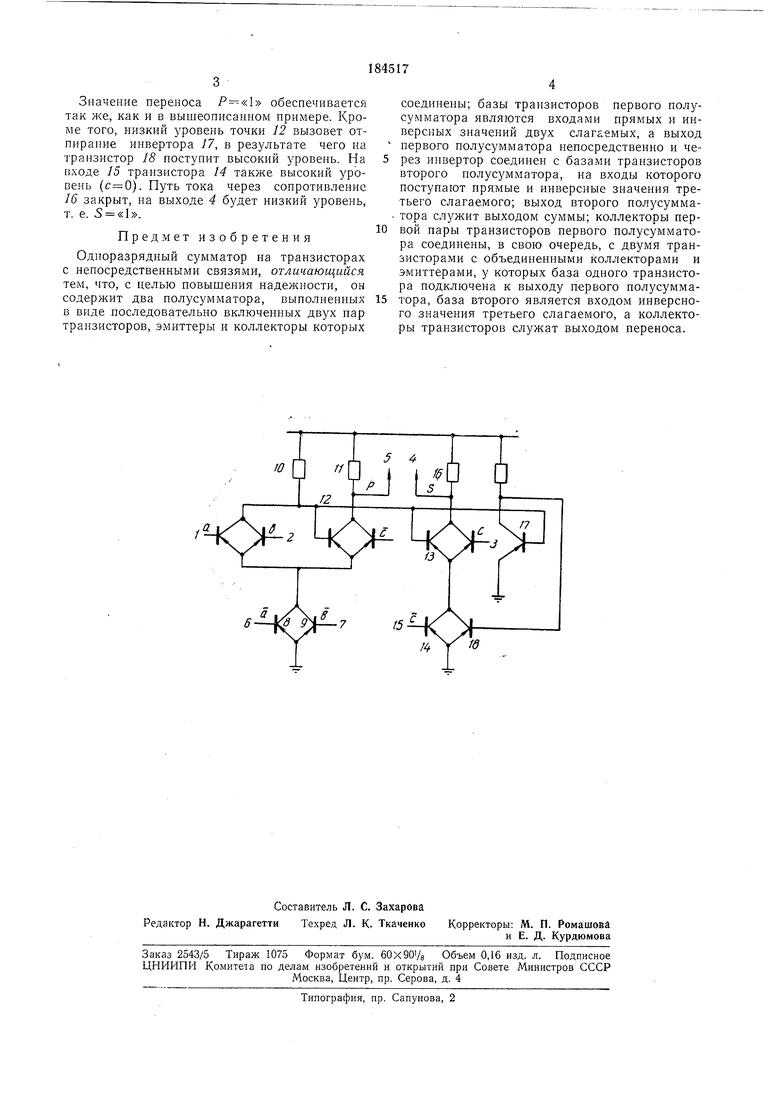

Р1звестны одноразрядные сумматоры с непосредственными связями и с трехъярусным включением транзисторов. Предложенный сумматор отличается от известных двухъярусным включением транзисторов, при котором коллекторы одной пары транзисторов электрически подключены к объединенным эмиттерам двух других пар транзисторов и участвуют в формировании логических функций одновременно. Базы транзисторов первого полусумматора являются входами прямых и инверсных значений двух слагаемых, а выход первого полусумматора непосредственно и через инвертор соединен с базами транзисторов второго полусумматора, на входы которого поступают прямые и инверсные значения третьего слагаемого. Выход второго полусумматора служит выходом суммы. Коллекторы первой пары транзисторов первого полусумматора соединены с двумя транзисторами с объединенными коллекторами и эмиттерами, у которых база одного транзистора подключена к выходу первого полусумматора, база второго является входом инверсного значения третьего слагаемого, а коллекторы транзисторов служат выходом переноса. На чертеже представлена принципиальная схема предложенного устройства, построенная на базе элемента с логикой «НЕ-ИЛИ, где «единице соответствует низкий уровень сигнала, а «нулю - высокий уровень. Рассмотрим работу схемы на следующем примере. Пусть на входы 7, 2 и 5 поданы слагаемые а «1, в «1, . Необходимо получить на выходе 4 сумму S «0 и на выходе 5 - перенос Р «1. В этом случае на входы б и 7 инверсных значений айв слагаемых будут поданы высокие уровни, соответствующие «О, и транзисторы 8 и 9 окажутся закрытыми. Путь тока через сопротивления 10 н 11 будет закрыт, в точке 12 и на выходе 5 переноса образуются низкие уровни, соответствующие «1. Низкий уровень точки 12 вызовет отпирание транзистора 13, а поскольку транзистор 14 также будет открыт низким уровнем на входе 15 (с «1), то образуется цепь тока через транзистор 14, транзистор 13 и сопротивление 16. На выходе 4 суммы образуется высокий уровень, соответствующий «О.

Значение переноса обеспечивается так же, как и в вышеописанном примере. Кроме того, низкий уровень точки 12 вызовет отпирание инвертора /7, в результате чего на транзистор 18 поступит высокий уровень. На входе 15 транзистора 14 также высокий уровень (). Путь тока через сопротивление 16 закрыт, на выходе 4 будет низкий уровень, т. е. 5 «1.

Предмет изобретения

Одноразрядный сумматор на транзисторах с непосредственными связями, отличающийся тем, что, с целью повышения падел :ности, он содержит два полусумматора, выполненных в виде последовательно включенных двух пар транзисторов, эмиттеры и коллекторы которых

соединены; базы транзисторов первого полусумматора являются входами прямых и инверсных зиачепий двух слагаемых, а выход первого полусумматора непосредственно и через иивертор соединен с базами транзисторов второго полусумматора, на входы которого поступают прямые и инверсные значения третьего слагаемого; выход второго полусумматора служит выходом суммы; коллекторы первой пары транзисторов первого полусумматора соединены, в свою очередь, с двумя транзисторами с объединенными коллекторами и эмиттерами, у которых база одного транзистора подключена к выходу первого полусумматора, база второго является входом инверсного значения третьего слагаемого, а коллекторы транзисторов служат выходом переноса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОРАЗРЯДНЫЙ Cy.iUMATOP | 1972 |

|

SU333555A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| ПОЛУСУММАТОР | 2015 |

|

RU2579980C1 |

| Блок переноса сумматора | 1988 |

|

SU1695293A1 |

| Одноразрядный сумматор | 1988 |

|

SU1599854A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1335982A1 |

| Одноразрядный сумматор | 1980 |

|

SU907543A1 |

| Четырехуровневый одноразрядный сумматор | 1982 |

|

SU1095174A1 |

| НИЗКОВОЛЬТНЫЙ D-ТРИГГЕР С АСИНХРОННОЙ УСТАНОВКОЙ ЗНАЧЕНИЯ НА ОСНОВЕ ЭМИТТЕРНО-СВЯЗАННОЙ ЛОГИКИ | 2016 |

|

RU2699684C2 |

| УНИВЕРСАЛЬНЫЙ ТРИГГЕР | 1973 |

|

SU364079A1 |

ff

0

kX

5 4

Ю

а tZ ,S с

6-j vrIJ -

Даты

1966-01-01—Публикация