Предлагаемое изобретение относится к устройствам обработки цифровых данных для сложения или вычитания и может быть использовано в устройствах вычислительной техники и систем управления.

Известен простой полусумматор [High Speed Half Adder Circuit, KR 100226756 (B1), опубл. 15.10.1999], так как у него отсутствует необходимость формирования двойной инверсии одного из слагаемых при выработке сигнала переноса, содержащий два информационных входа А и В, выходы суммы и переноса, два n-транзистора и две одинаковых пары р-n транзисторов, объединенных в каждой паре по входам управления и выходным цепям, причем у р-транзисторов инверсные входы управления, а у n-транзисторов прямые входы управления, кроме того, входные цепи р-транзистора и n-транзистора первой пары соединены соответственно с шинами питания и земли, при этом входная цепь р-транзистора второй пары соединена со вторым информационным входом В устройства, с входом управления первой пары р-n транзисторов, с входом управления первого n-транзистора и входной цепью второго n-транзистора, а входная цепь n-транзистора второй пары р-n транзисторов соединена с выходной цепью первой пары р-n транзисторов и входом управления второго n-транзистора, у которого выходная цепь соединена с выходом переноса и с выходной цепью первого n-транзистора, а входная цепь первого n-транзистора соединена с первым информационным входом А устройства и входом управления второй пары р-n транзисторов, а выходная цепь второй пары р-n транзисторов соединена с выходом суммы.

Формирование сигнала суммы происходит от взаимодействия первой и второй пар транзисторов. В зависимости от сигнала на первом информационном входе А, поступающем на вход управления второй пары транзисторов, на выход суммы со второго информационного входа В проходит прямой или инвертированный на первой паре транзисторов сигнал.

Формирование сигнала переноса происходит от взаимодействия первого и второго n-транзисторов, а также первой пары транзисторов. При этом сигнал со второго информационного входа В напрямую поступает на вход управления первого n-транзистора, и при единичном уровне этого сигнала первый n-транзистор пропускает на выход переноса сигнал с первого информационного входа А, а на вход управления второго n-транзистора поступает инвертированный на первой паре транзисторов сигнал со второго информационного входа В, и при единичном уровне инвертированного сигнала второй n-транзистор пропускает на выход переноса сигнал со второго информационного входа В.

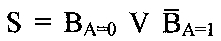

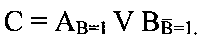

Работа аналога определяется функциями суммы  и переноса

и переноса

Однако устройство обладает пониженной помехоустойчивостью.

Из числа аналогов наиболее близким по технической сущности является полусумматор [Half Adder Circuit, KR 20030058821 (А), опубл. 07.07.2003], который и выбран в качестве прототипа. Этот полусумматор обладает большей помехоустойчивостью, так как в процессе формирования переноса при нулевом уровне сигнала на первом информационном входе учитывается предопределенность результата, реализуемая безусловным переходом этого входного сигнала на выход переноса через диодное включение транзистора, при котором входная цепь транзистора объединена с его входом управления.

В состав прототипа входит три n-транзистора с прямыми входами управления и три р-транзистора с инверсными входами управления, два информационных входа устройства, первый и второй, а также выходы суммы и переноса, при этом выходные цепи первого n-транзистора и первого р-транзистора объединены и соединены с выходом суммы, а входы управления этих транзисторов тоже объединены и соединены с первым информационным входом устройства и с входной цепью второго р-транзистора, причем входная цепь первого n-транзистора соединена с объединенными выходными цепями третьего р-транзистора и второго n-транзистора, входные цепи которых соединены с шинами соответственно питания и земли, а входы управления этих транзисторов объединены между собой, при этом выходные цепи второго р-транзистора и третьего n-транзистора объединены и соединены с выходом переноса.

Кроме того, входы управления второго р-транзистора и третьего n-транзистора объединены и соединены с первым информационным входом, а второй информационный вход соединен со входами управления третьего р-транзистора и второго n-транзистора, а также с объединенными входными цепями третьего n-транзистора и первого р-транзистора.

Формирование сигнала суммы происходит от взаимодействия первой и второй пар транзисторов. Причем первая пара транзисторов состоит из второго n-транзистора и третьего р-транзистора, а вторая пара транзисторов - из первого n-транзистора и первого р-транзистора. В зависимости от сигнала на первом информационном входе А, поступающем на вход управления второй пары транзисторов, на выход суммы со второго информационного входа В проходит прямой или инвертированный на первой паре транзисторов сигнал.

Формирование сигнала переноса происходит от взаимодействия второго р-транзистора и третьего n-транзистора. При этом сигнал с первого информационного входа А напрямую поступает на входы управления второго р-транзистора и третьего n-транзистора. При нулевом уровне рассматриваемого сигнала он проходит на выход переноса через второй р-транзистор, а при единичном уровне этого сигнала на выход переноса проходит сигнал со второго информационного входа В.

Работа прототипа определяется функциями суммы  и переноса

и переноса

Функции суммы прототипа и аналога совпадают, а функции переноса отличаются, при этом в прототипе используется предопределенность результата, а в аналоге необходимо дополнительное формирование инверсного управляющего сигнала.

Недостатком прототипа является пониженная помехоустойчивость из-за сквозного перехода входных сигналов на выход переноса и повышенных рисков возможности отработки ложных сигналов помех, связанных с асинхронной работой устройства.

Задачей, на решение которой направлено заявляемое изобретение, является повышение помехоустойчивости устройства за счет снижения рисков возможности отработки ложных сигналов помех при синхронной работе устройства и исключения сквозного перехода одного из входных сигналов на выход переноса.

Техническим результатом является введение тактируемого элемента памяти на двух последовательно включенных парах транзисторов, охваченных цепью локальной обратной связи и использование на выходе переноса сигнала непосредственно с шины земли при нулевом значении одного из входных сигналов, что позволяет уменьшить искажения внутренних и выходных сигналов, при сохранении функциональных возможностей устройства.

Поставленная задача решается тем, что в полусумматор, содержащий три n-транзистора с прямыми входами управления и три р-транзистора с инверсными входами управления, два информационных входа устройства первый и второй, а также выходы суммы и переноса, при этом выходные цепи первого n-транзистора и первого р-транзистора объединены и соединены с выходом суммы, а входы управления этих транзисторов тоже объединены и соединены с первым информационным входом устройства и с входной цепью второго р-транзистора, причем входная цепь первого n-транзистора соединена с объединенными выходными цепями третьего р-транзистора и второго n-транзистора, входные цепи которых соединены с шинами соответственно питания и земли, а входы управления этих транзисторов объединены между собой, при этом выходные цепи второго р-транзистора и третьего n-транзистора объединены и соединены с выходом переноса.

Дополнительно введены пять n-транзисторов с прямыми входами управления, четыре р-транзистора с инверсными входами управления, прямой и инверсный входы синхронизации, соединенные со входами управления соответственно четвертого n-транзистора и четвертого р-транзистора, при этом входные цепи этих транзисторов объединены и соединены со вторым информационным входом, а выходные цепи тоже объединены и соединены со входами управления третьего р-транзистора и второго n-транзистора, входом управления пятого n-транзистора, а также с входной цепью первого р-транзистора и с объединенными выходными цепями пятого р-транзистора и шестого n-транзистора, причем входы управления пятого р-транзистора и шестого n-транзистора объединены и соединены с выходными цепями третьего р-транзистора и второго n-транзистора и со входами управления третьего n-транзистора и второго р-транзистора, входная и выходная цепи которого объединены соответственно с входной и выходной цепями пятого n-транзистора, кроме того, входные цепи пятого р-транзистора и шестого р-транзистора соединены с шиной питания, а входные цепи шестого n-транзистора, третьего n-транзистора и седьмого n-транзистора соединены с шиной земли, при этом входы управления седьмого n-транзистора и шестого р-транзистора объединены и соединены с первым информационным входом устройства, а выходные цепи этих транзисторов тоже объединены и соединены с объединенными входами управления седьмого р-транзистора и восьмого n-транзистора, причем входная и выходная цепи седьмого р-транзистора объединены соответственно с входной и выходной цепями первого n-транзистора, а входная и выходная цепи восьмого n-транзистора объединены соответственно с входной и выходной цепями первого р-транзистора.

Сущность предлагаемого изобретения состоит в создании помехоустойчивого полусумматора, за счет синхронного приема одного из слагаемых с записью его в памяти и использования шины земли как источника сигнала, что позволяет уменьшить зависимость цепей формирования суммы и переноса от качества входных сигналов.

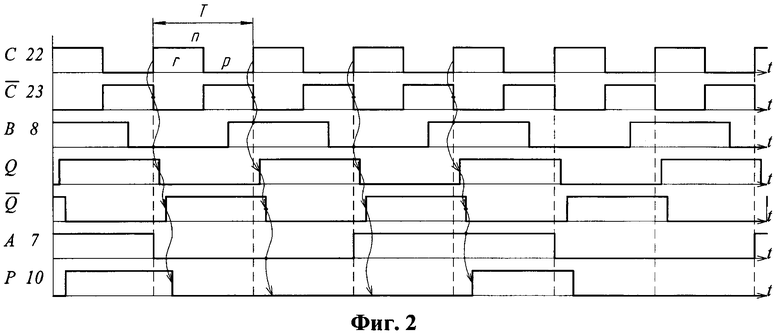

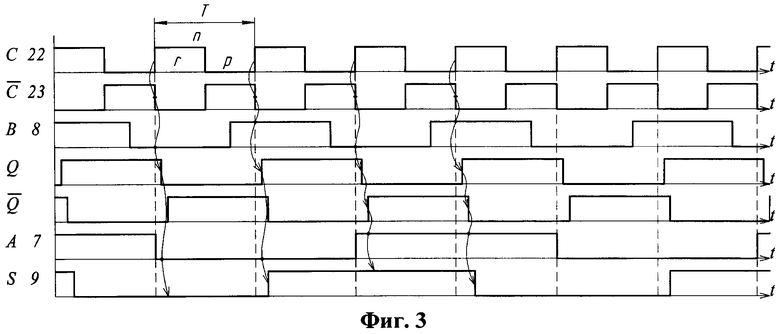

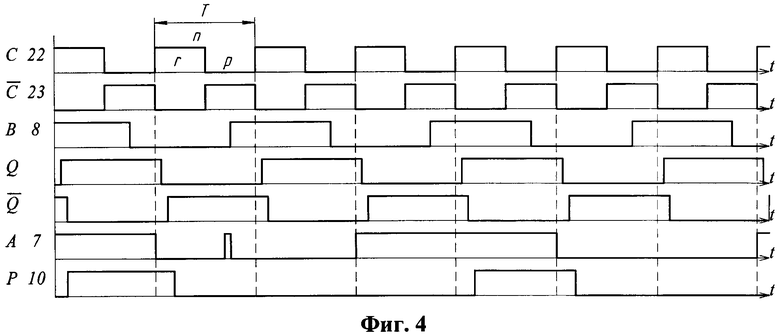

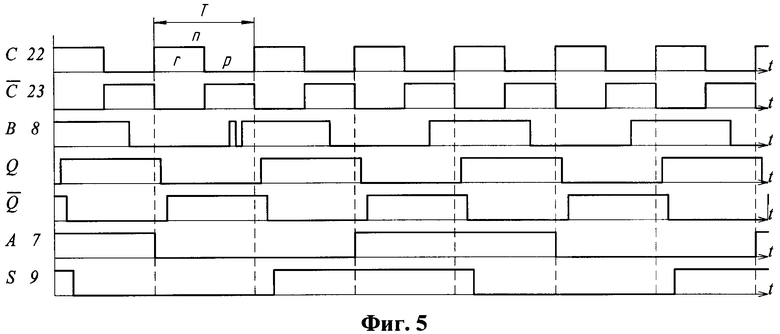

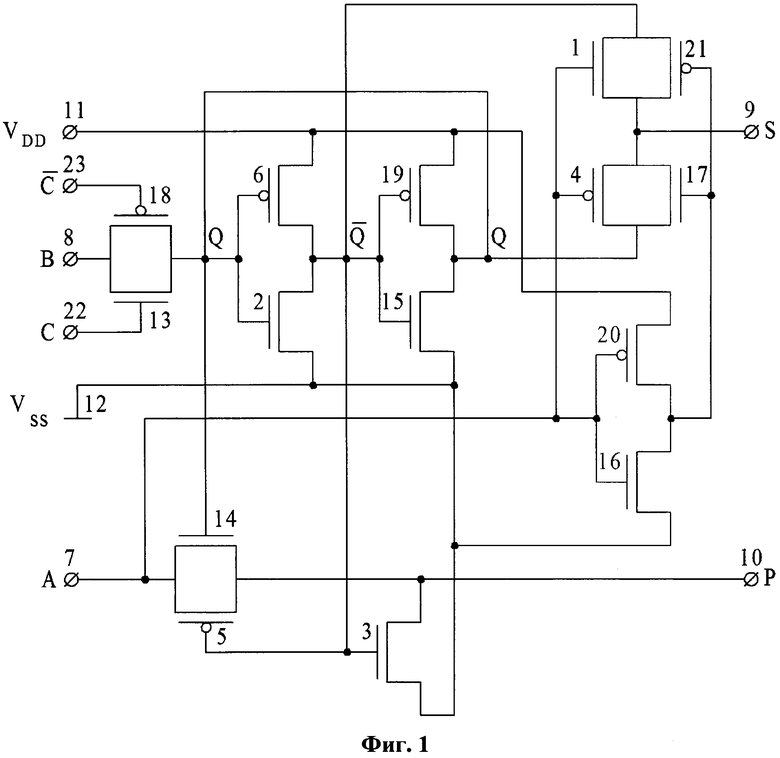

Сущность предлагаемого изобретения поясняется чертежами, где на фиг. 1 изображена схема предлагаемого полусумматора, на фиг. 2 и 3 представлены временные диаграммы процессов формирования переноса и суммы соответственно, а на фиг. 4 и 5 - временные диаграмма процессов формирования переноса и суммы с помехами на первом и втором информационных входах соответственно.

Полусумматор (фиг. 1) содержит первый 1, второй 2 и третий 3 n-транзисторы с прямыми входами управления и первый 4, второй 5 и третий 6 р-транзисторы с инверсными входами управления, первый 7 и второй 8 информационные входы устройства, а также выходы суммы 9 и переноса 10, при этом выходные цепи первого n-транзистора 1 и первого р-транзистора 4 объединены и соединены с выходом суммы 9, а входы управления этих транзисторов тоже объединены и соединены с первым информационным входом 7 устройства и с входной цепью второго р-транзистора 5, причем входная цепь первого n-транзистора 1 соединена с объединенными выходными цепями третьего р-транзистора 6 и второго n-транзистора 2, входные цепи которых соединены с шинами соответственно питания 11 и земли 12, а входы управления этих транзисторов объединены между собой, при этом выходные цепи второго р-транзистора 5 и третьего n-транзистора 3 объединены и соединены с выходом переноса 10.

Кроме того, полусумматор содержит четвертый 13, пятый 14, шестой 15, седьмой 16 и восьмой 17 n-транзисторы с прямыми входами управления, четвертый 18, пятый 19, шестой 20 и седьмой 21 р-транзисторы с инверсными входами управления, прямой 22 и инверсный 23 входы синхронизации, соединенные со входами управления соответственно четвертого n-транзистора 13 и четвертого р-транзистора 18, при этом входные цепи этих транзисторов объединены и соединены со вторым информационным входом 8, а выходные цепи тоже объединены и соединены со входами управления третьего р-транзистора 6 и второго n-транзистора 2, входом управления пятого n-транзистора 14, а также с входной цепью первого р-транзистора 4 и с объединенными выходными цепями пятого р-транзистора 19 и шестого n-транзистора 15, причем входы управления пятого р-транзистора 19 и шестого n-транзистора 15 объединены и соединены с выходными цепями третьего р-транзистора 6 и второго n-транзистора 2 и со входами управления третьего n-транзистора 3 и второго р-транзистора 5, входная и выходная цепи которого объединены соответственно с входной и выходной цепями пятого n-транзистора 14, кроме того, входные цепи пятого р-транзистора 19 и шестого р-транзистора 20 соединены с шиной питания 11, а входные цепи шестого n-транзистора 15, третьего n-транзистора 3 и седьмого n-транзистора 16 соединены с шиной земли 12, при этом входы управления седьмого n-транзистора 16 и шестого р-транзистора 20 объединены и соединены с первым информационным входом 7 устройства, а выходные цепи этих транзисторов тоже объединены и соединены с объединенными входами управления седьмого р-транзистора 21 и восьмого n-транзистора 17, причем входная и выходная цепи седьмого р-транзистора 21 объединены соответственно с входной и выходной цепями первого n-транзистора 1, а входная и выходная цепи восьмого n-транзистора 17 объединены соответственно с входной и выходной цепями первого р-транзистора 4.

Устройство работает следующим образом.

Пусть на входы синхронизации 22 и 23 поступают синхросигналы, соответственно прямой С и инверсный

При единичном уровне прямого синхросигнала С открыт четвертый n-транзистор 13, в то же время инверсный синхросигнал

При этом на втором информационном входе 8 возможна ситуация, когда входной сигнал представлен нулевым уровнем. Этот сигнал проходит через открытые четвертый n-транзистор 13 и четвертый р-транзистор 18 и поступает на входные цепи первого р-транзистора 4 и восьмого n-транзистора 17, а также на входы управления третьего р-транзистора 6, второго n-транзистора 2 и пятого n-транзистора 14. Нулевой уровень этого сигнала закрывает второй 2 и пятый 14 n-транзисторы и открывает третий р-транзистор 6. Таким образом, сигнал единичного уровня с шины питания 11 поступает через открытый третий р-транзистор 6 на входные цепи седьмого р-транзистора 21 и первого n-транзистора 1, а также на входы управления пятого р-транзистора 19, шестого n-транзистора 15, второго р-транзистора 5 и третьего n-транзистора 3. Единичный уровень этого сигнала закрывает пятый 19 и второй 5 р-транзисторы и открывает шестой 15 и третий 3 n-транзисторы. Сигнал нулевого уровня с шины земли 12 поступает через открытый третий n-транзистор 3 на выход переноса 10, а через открытый шестой n-транзистор 15 - на входные цепи первого р-транзистора 4 и восьмого n-транзистора 17.

В то же время если входной сигнал с первого информационного входа 7 полусумматора представлен нулевым уровнем, он поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16, а также на входные цепи пятого n-транзистора 14 и второго р-транзистора 5. Нулевой уровень этого сигнала закрывает первый 1 и седьмой 16 n-транзисторы и открывает первый 4 и шестой 20 р-транзисторы. Сигнал единичного уровня с шины питания 11 поступает через открытый шестой р-транзистор 20 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым закрывая седьмой р-транзистор 21 и открывая восьмой n-транзистор 17. Таким образом, сигнал нулевого уровня поступает через открытые первый р-транзистор 4 и восьмой n-транзистор 17 на выход суммы 9.

Если входной сигнал с первого информационного входа 7 полусумматора представлен единичным уровнем, он поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16, а также на входные цепи пятого n-транзистора 14 и второго р-транзистора 5. Единичный уровень этого сигнала закрывает первый 4 и шестой 20 р-транзисторы и открывает первый 1 и седьмой 16 n-транзисторы. Сигнал нулевого уровня с шины земли 12 поступает через открытый седьмой n-транзистор 16 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым открывая седьмой р-транзистор 21 и закрывая восьмой n-транзистор 17. Таким образом, сигнал единичного уровня поступает через открытые первый n-транзистор 1 и седьмой р-транзистор 21 на выход суммы 9.

На втором информационном входе 8 возможна другая ситуация, когда входной сигнал представлен единичным уровнем. Этот сигнал проходит через открытые четвертый n-транзистор 13 и четвертый р-транзистор 18 и поступает на входные цепи первого р-транзистора 4 и восьмого n-транзистора 17, а также на входы управления третьего р-транзистора 6, второго n-транзистора 2 и пятого n-транзистора 14. Единичный уровень этого сигнала открывает второй 2 и пятый 14 n-транзисторы и закрывает третий р-транзистор 6. Таким образом, сигнал нулевого уровня с шины земли 12 поступает через открытый второй n-транзистор 2 на входные цепи седьмого р-транзистора 21 и первого n-транзистора 1, а также на входы управления пятого р-транзистора 19, шестого n-транзистора 15, второго р-транзистора 5 и третьего n-транзистора 3. Нулевой уровень этого сигнала открывает пятый 19 и второй 5 р-транзисторы и закрывает шестой 15 и третий 3 n-транзисторы. Сигнал единичного уровня с шины питания 11 поступает через открытый пятый р-транзистор 19 на входные цепи первого р-транзистора 4 и восьмого n-транзистора 17.

В то же время если входной сигнал с первого информационного входа 7 полусумматора представлен нулевым уровнем, он проходит через открытые пятый n-транзистор 14 и второй р-транзистор 5 на выход переноса 10, а также поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16. Нулевой уровень этого сигнала закрывает первый 1 и седьмой 16 n-транзисторы и открывает первый 4 и шестой 20 р-транзисторы. Сигнал единичного уровня с шины питания 11 поступает через открытый шестой р-транзистор 20 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым закрывая седьмой р-транзистор 21 и открывая восьмой n-транзистор 17. Таким образом, сигнал единичного уровня поступает через открытые первый р-транзистор 4 и восьмой n-транзистор 17 на выход суммы 9.

Если входной сигнал с первого информационного входа 7 полусумматора представлен единичным уровнем, он проходит через открытые пятый n-транзистор 14 и второй р-транзистор 5 на выход переноса 10, а также поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16.

Единичный уровень этого сигнала закрывает первый 4 и шестой 20 р-транзисторы и открывает первый 1 и седьмой 16 n-транзисторы. Сигнал нулевого уровня с шины земли 12 поступает через открытый седьмой n-транзистор 16 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым открывая седьмой р-транзистор 21 и закрывая восьмой n-транзистор 17. Таким образом, сигнал нулевого уровня поступает через открытые первый n-транзистор 1 и седьмой р-транзистор 21 на выход суммы 9.

При смене прямого синхросигнала С на нулевой уровень (фиг. 2, 3, 4, 5) закроется четвертый n-транзистор 13. В то же время изменится инверсный синхросигнал

При этом возможна ситуация, когда поддерживаемый сигнал представлен нулевым уровнем. Этот сигнал с выхода второй пары транзисторов подается на входные цепи первого р-транзистора 4 и восьмого n-транзистора 17, а также через локальную обратную связь на входы управления третьего р-транзистора 6, второго n-транзистора 2 и пятого n-транзистора 14. Нулевой уровень этого сигнала поддерживает второй 2 и пятый 14 n-транзисторы закрытыми, а третий р-транзистор 6 открытым. Таким образом, сигнал единичного уровня с шины питания 11 подается через открытый третий р-транзистор 6 на входные цепи седьмого р-транзистора 21 и первого n-транзистора 1, а также на входы управления пятого р-транзистора 19, шестого n-транзистора 15, второго р-транзистора 5 и третьего n-транзистора 3. Единичный уровень этого сигнала поддерживает пятый 19 и второй 5 р-транзисторы закрытыми, а шестой 15 и третий 3 n-транзисторы открытыми. Сигнал нулевого уровня с шины земли 12 подается через открытый третий n-транзистор 3 на выход переноса 10, а через открытый шестой n-транзистор 15 - на выход второй пары транзисторов.

В то же время если входной сигнал с первого информационного входа 7 полусумматора представлен нулевым уровнем, он поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16, а также на входные цепи пятого n-транзистора 14 и второго р-транзистора 5. Нулевой уровень этого сигнала закрывает первый 1 и седьмой 16 n-транзисторы и открывает первый 4 и шестой 20 р-транзисторы. Сигнал единичного уровня с шины питания 11 поступает через открытый шестой р-транзистор 20 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым закрывая седьмой р-транзистор 21 и открывая восьмой n-транзистор 17. Таким образом, сигнал нулевого уровня поступает через открытые первый р-транзистор 4 и восьмой n-транзистор 17 на выход суммы 9.

Если входной сигнал с первого информационного входа 7 полусумматора представлен единичным уровнем, он поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16, а также на входные цепи пятого n-транзистора 14 и второго р-транзистора 5. Единичный уровень этого сигнала закрывает первый 4 и шестой 20 р-транзисторы и открывает первый 1 и седьмой 16 n-транзисторы. Сигнал нулевого уровня с шины земли 12 поступает через открытый седьмой n-транзистор 16 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым открывая седьмой р-транзистор 21 и закрывая восьмой n-транзистор 17. Таким образом, сигнал единичного уровня поступает через открытые первый n-транзистор 1 и седьмой р-транзистор 21 на выход суммы 9.

Возможна другая ситуация, когда поддерживаемый сигнал представлен единичным уровнем. Этот сигнал с выхода второй пары транзисторов подается на входные цепи первого р-транзистора 4 и восьмого n-транзистора 17, а также через локальную обратную связь на входы управления третьего р-транзистора 6, второго n-транзистора 2 и пятого n-транзистора 14. Единичный уровень этого сигнала поддерживает второй 2 и пятый 14 n-транзисторы открытыми, а третий р-транзистор 6 закрытым. Таким образом, сигнал нулевого уровня с шины земли 12 подается через открытый второй n-транзистор 2 на входные цепи седьмого р-транзистора 21 и первого n-транзистора 1, а также на входы управления пятого р-транзистора 19, шестого n-транзистора 15, второго р-транзистора 5 и третьего n-транзистора 3. Нулевой уровень этого сигнала поддерживает пятый 19 и второй 5 р-транзисторы открытыми, а шестой 15 и третий 3 n-транзисторы закрытыми. Сигнал единичного уровня с шины питания 11 подается через открытый пятый р-транзистор 19 на выход второй пары транзисторов.

В то же время если входной сигнал с первого информационного входа 7 полусумматора представлен нулевым уровнем, он проходит через открытые пятый n-транзистор 14 и второй р-транзистор 5 на выход переноса 10, а также поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16. Нулевой уровень этого сигнала закрывает первый 1 и седьмой 16 n-транзисторы и открывает первый 4 и шестой 20 р-транзисторы. Сигнал единичного уровня с шины питания 11 поступает через открытый шестой р-транзистор 20 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым закрывая седьмой р-транзистор 21 и открывая восьмой n-транзистор 17. Таким образом, сигнал единичного уровня поступает через открытые первый р-транзистор 4 и восьмой n-транзистор 17 на выход суммы 9.

Если входной сигнал с первого информационного входа 7 полусумматора представлен единичным уровнем, он проходит через открытые пятый n-транзистор 14 и второй р-транзистор 5 на выход переноса 10, а также поступает на входы управления первого n-транзистора 1, первого р-транзистора 4, шестого р-транзистора 20 и седьмого n-транзистора 16. Единичный уровень этого сигнала закрывает первый 4 и шестой 20 р-транзисторы и открывает первый 1 и седьмой 16 n-транзисторы. Сигнал нулевого уровня с шины земли 12 поступает через открытый седьмой n-транзистор 16 на входы управления седьмого р-транзистора 21 и восьмого n-транзистора 17, тем самым открывая седьмой р-транзистор 21 и закрывая восьмой n-транзистор 17. Таким образом, сигнал нулевого уровня поступает через открытые первый n-транзистор 1 и седьмой р-транзистор 21 на выход суммы 9.

При смене прямого синхросигнала С на единичный уровень (фиг. 2, 3, 4, 5) откроется четвертый n-транзистор 13. В то же время изменится инверсный синхросигнал

Таким образом, формирование сигнала суммы происходит от взаимодействия первой и второй пар транзисторов и транзисторов 1, 4, 17, 21. При единичном уровне прямого синхросигнала С и нулевом уровне инверсного синхросигнала С сигнал со второго информационного входа 8 поступает на входные цепи транзисторов 4, 17 и на вход первой пары транзисторов, с выхода первой пары поступает на входные цепи 1, 21 транзисторов и на вход второй пары транзисторов, с выхода второй пары транзисторов поступает на входные цепи транзисторов 4, 17. В зависимости от сигнала на первом информационном входе 7 и его инверсии с выходных цепей транзисторов 16, 20, поступающих на входы управления транзисторов 1, 4 и на входы управления транзисторов 17, 21 соответственно, на выход суммы 9 проходит прямой или инвертированный сигнал со второго информационного входа 8. И наоборот, при нулевом уровне прямого синхросигнала С и единичном уровне инверсного синхросигнала С сигнал с выхода второй пары транзисторов подается на входные цепи транзисторов 4, 17 и на вход первой пары транзисторов, сигнал с выхода первой пары поступает на входные цепи транзисторов 1, 21 и на вход второй пары транзисторов. В зависимости от сигнала на первом информационном входе 7 и его инверсии с выходных цепей транзисторов 16, 20, поступающих на входы управления транзисторов 1, 4 и на входы управления транзисторов 17, 21 соответственно, на выход суммы 9 проходит прямой или инвертированный сохраненный сигнал со второго информационного входа 8, который поддерживается на последовательно включенных двух парах транзисторов, охваченных цепью локальной обратной связи.

Формирование сигнала переноса происходит от взаимодействия первой пары транзисторов и транзисторов 3, 5, 14. При этом если сигнал на выходе первой пары транзисторов представлен единичный уровнем, тогда сигнал нулевого уровня с шины земли 12 проходит через транзистор 3 на выход переноса 10, и наоборот, если сигнал на выходе первой пары транзисторов представлен нулевым уровнем, а значит на входе первой пары транзисторов сигнал единичного уровня, тогда сигнал с первого информационного входа 7 проходит на выход переноса 10 через транзисторы 5, 14.

В основу работы полусумматора положен принцип фиксации одного из входных сигналов в памяти и предопределенности нулевого результата в цепи формирования переноса, благодаря чему в полусумматоре появилась возможность улучшения качества внутренних и выходных сигналов.

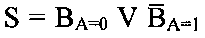

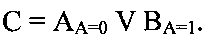

Характеристические функции полусумматора по выходам суммы 9 и переноса 10 определяются соответственно выражениями:

где А - сигнал на первом информационном входе;

Q - сигнал тактируемого элемента памяти на двух последовательно включенных парах транзисторов, охваченных цепью локальной обратной связи;

Функциональная характеристика сигнала тактируемого элемента памяти на n-ом такте имеет вид:

где Bn - сигнал на втором информационном входе на очередном n-ом такте прямого синхросигнала С в течение действия его единичного уровня от n до n+r;

Qn+r - сигнал тактируемого элемента памяти на двух последовательно включенных парах транзисторов, охваченных цепью локальной обратной связи на очередном n-ом такте инверсного синхросигнала

r - часть периода Т, определяемая действием синхросигнала С единичного уровня и синхросигнала С нулевого уровня;

р - часть периода Т, определяемая действием синхросигнала С нулевого уровня и синхросигнала

r+р=1 - период Т как прямого синхросигнала С, так и инверсного синхросигнала

При этом сигнал тактируемого элемента памяти сформировался на n-ом такте прямого синхросигнала С в течение действия его единичного уровня от n до n+r и определялся уровнем входного сигнала на втором информационном входе:

Подставляя выражения (4) в (3), получаем функциональную характеристику для сигнала Qn на n-ом такте:

Таким образом, для любого такта всегда справедливо равенство:

Подставляя выражения (6) в (1), получаем характеристическую функцию полусумматора по выходу суммы 9:

Подставляя выражения (6) в (2), получаем характеристическую функцию полусумматора по выходу переноса 10:

Указанные характеристические функции (7) и (8) соответствуют характеристическим функциям полусумматора [Карцев М.А. Арифметика цифровых машин [Текст] / М.А. Карцев. - М.: Наука, 1969. - С. 154].

Помеха, появившаяся на первом информационном входе А в ситуации, когда на выходе первой пары транзисторов сигнал был единичного уровня (фиг. 4), не повлияет на сигнал переноса, так как в этот момент на выход переноса Р напрямую подается сигнал с шины земли.

Помеха, появившаяся на втором информационном входе В в ситуации, когда прямой синхросигнал С имел нулевой уровень, а инверсный синхросигнал

Таким образом, предложенный полусумматор является более помехоустойчивым благодаря синхронному приему одного из слагаемых с записью его в памяти и использованию шины земли как источника сигнала, обеспечивающих уменьшение зависимости цепей формирования суммы и переноса от качества входных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| ДВУХСТУПЕНЧАТЫЙ ТРИГГЕР | 2014 |

|

RU2542575C1 |

| СУММАТОР НА КМДП ТРАНЗИСТОРАХ | 2001 |

|

RU2185655C1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| Устройство для умножения | 1987 |

|

SU1411733A1 |

| Устройство вычисления сумм произведений | 1990 |

|

SU1718216A1 |

| Сумматор в коде "М из @ | 1982 |

|

SU1053103A2 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| МНОГОВЫХОДНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2613536C1 |

Изобретение относится к устройствам обработки цифровых данных для сложения или вычитания и может быть использовано в устройствах вычислительной техники и систем управления. Техническим результатом является повышение помехоустойчивости устройства. Устройство содержит восемь n-транзисторов с прямыми входами управления и семь р-транзисторов с инверсными входами управления, прямой и инверсный входы синхронизации, два информационных входа, выходы суммы и переноса, шины питания VDD и земли. 5 ил.

Полусумматор, содержащий три n-транзистора с прямыми входами управления и три р-транзистора с инверсными входами управления, два информационных входа устройства, первый и второй, а также выходы суммы и переноса, при этом выходные цепи первого n-транзистора и первого р-транзистора объединены и соединены с выходом суммы, а входы управления этих транзисторов тоже объединены и соединены с первым информационным входом устройства и с входной цепью второго р-транзистора, причем входная цепь первого n-транзистора соединена с объединенными выходными цепями третьего р-транзистора и второго n-транзистора, входные цепи которых соединены с шинами соответственно питания и земли, а входы управления этих транзисторов объединены между собой, при этом выходные цепи второго р-транзистора и третьего n-транзистора объединены и соединены с выходом переноса, отличающийся тем, что в устройство дополнительно введены пять n-транзисторов с прямыми входами управления, четыре р-транзистора с инверсными входами управления, прямой и инверсный входы синхронизации, соединенные со входами управления соответственно четвертого n-транзистора и четвертого р-транзистора, при этом входные цепи этих транзисторов объединены и соединены со вторым информационным входом, а выходные цепи тоже объединены и соединены со входами управления третьего р-транзистора и второго n-транзистора, входом управления пятого n-транзистора, а также с входной цепью первого р-транзистора и с объединенными выходными цепями пятого р-транзистора и шестого n-транзистора, причем входы управления пятого р-транзистора и шестого n-транзистора объединены и соединены с выходными цепями третьего р-транзистора и второго n-транзистора и со входами управления третьего n-транзистора и второго р-транзистора, входная и выходная цепи которого объединены соответственно с входной и выходной цепями пятого n-транзистора, кроме того, входные цепи пятого р-транзистора и шестого р-транзистора соединены с шиной питания, а входные цепи шестого n-транзистора, третьего n-транзистора и седьмого n-транзистора соединены с шиной земли, при этом входы управления седьмого n-транзистора и шестого р-транзистора объединены и соединены с первым информационным входом устройства, а выходные цепи этих транзисторов тоже объединены и соединены с объединенными входами управления седьмого р-транзистора и восьмого n-транзистора, причем входная и выходная цепи седьмого р-транзистора объединены соответственно с входной и выходной цепями первого n-транзистора, а входная и выходная цепи восьмого n-транзистора объединены соответственно с входной и выходной цепями первого р-транзистора.

| KR 20030058821 A, 07.07.2003 | |||

| KR 100226756 B1, 15.10.1999 | |||

| JP 6225326 A, 03.02.1987 | |||

| US 4054788 A, 18.10.1977 | |||

| Полусумматор на МДП-транзисторах | 1981 |

|

SU1008909A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 1996 |

|

RU2164036C2 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2011 |

|

RU2444050C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

Авторы

Даты

2016-04-10—Публикация

2015-02-09—Подача