Изобретение относится к области вычислительной техники.

Известны одноразрядные сумматоры, содержащие два полусумматора на включенных по двухъярусной схеме транзисторах с дополняющей симметрией.

Предложенный сумматор отличается тем, что в нем управляющие входы пар транзисторов п-тяпа -первого яруса объединены в обоих нолусумматорах с управляющими входами пар транзисторов /7-типа второго яруса; управляющие входы пары транзисторов п-пта второго яруса первого полусумматора соединены соответственно с одним из его выходов и с одним из управляющих входов второго полусумматора, а также с выходом источиика инверсного сигнала одного из слагаемых; объединенные управляющие входы первого полусумматора подключены к выходам иеточников инверсных сигналов второго и третьего слагаемых; свободный управляющий вход второго полусумматора соединен с выходом источника прямого сигнала одного из слагаемых, а его выход подключен к выходному зажи.му сигнала судммы; второй выход первого полусумматора соединен с выходным зажнмом сигнала переноса.

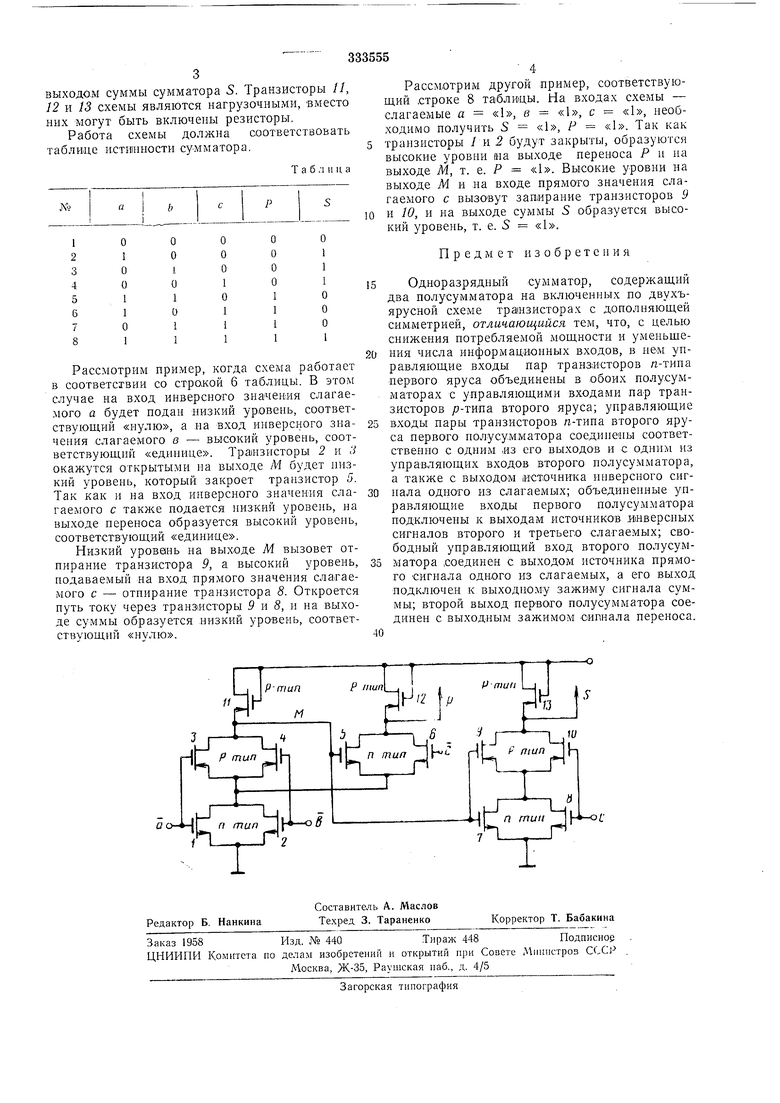

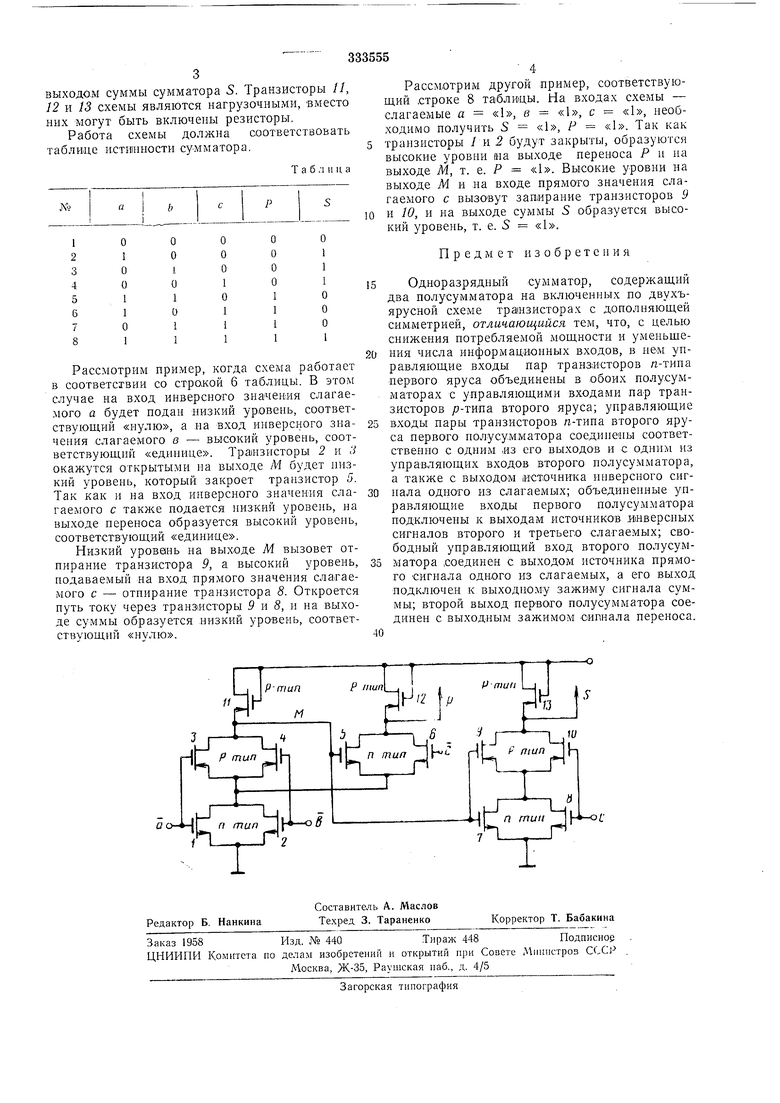

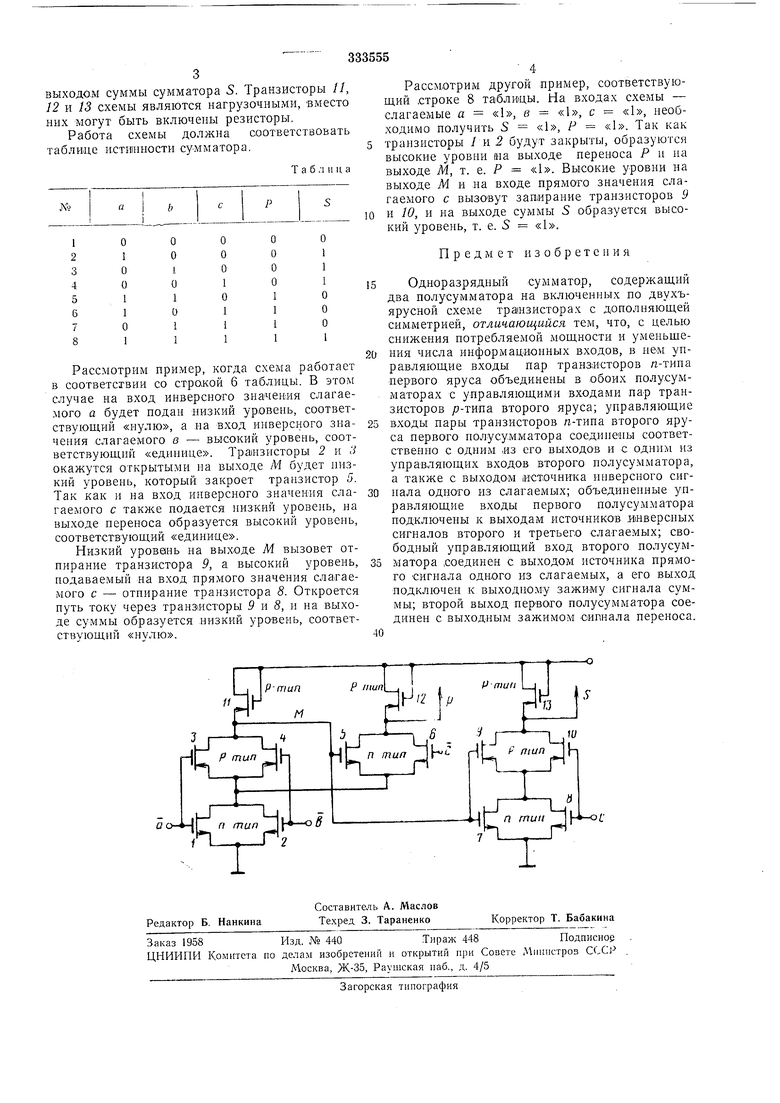

На чертеже представлена прин лнпналь.чая схема устройства.

Сумматор состоит из двух нол сумматорои с двухъярусным включением пар транзисгорои, объединенных по стокам и истокам. В первом ярусе первого полусумматора включена пара транзисторов я-тяпа / и 2, в левой половине второго яруса первого полусумматора включена пара транзисторов ;-типа 3 и 4,

а в правой половине второго яруса первого полусумматора включена пара транзисторов л-типа 5 и 5. В первом ярусе второго полусу.мматора включена пара транзисторов ;г-типа 7 и S, а во втором ярусе второго полусумматора

включена пара транзисторов р-тнпа .9 и }(). Два входа левой половины полусумматора служат входами инверсных значен:11Й двух слагаемых (а и в), а выход левой половины полусумматора связан с одним из входов пары транзисторов п-тн1па 5 и 5 второго яруса правой ПОЛОВИ1НЫ полусумматора и с одн1;м из входов второго полусумматора. Второй яход пары транзисторов п-типа 5 и 6 второго яруса правой половины полусумматора служит

входом инверсного значения третьего слагаемого с, а второй вход второго полусу.мматора служит входом прямого значения третьего слагаемого с. Выход правой половины полусумматора является выходом перено,са сумВЫХОДО.М суммы сумматора 5. Транзисторы 11, 12 и 13 схемы являются нагрузочными, вместо них могут быть включены резисторы.

Работа схемы должна соответствовать таблице и,сти1нности сумматора.

Т а б л и ц а

Рассмотрим пример, когда схема работает в соответствии со строкой 6 таблицы. В этом случае на вход инверсного значения слагаемого а будет подан иизкий уровень, соответствующий «нулю, а па вход инверсного значения слагаемого в - высокий уровень, соответствующнй «единице. Тра1нзисторы 2 и . окажутся открытыми на выходе М будет иизкий уровень, который закроет транзистор 5. Так как и на вход инверсного значения слагаемого с также подается низкий уровень, на выходе переноса образуется высокий уровень, соответствующий «единице.

Низкий уровень на выходе М вызовет отпирание транзистора 9, а высокий уровень, подаваемый на вход прямого значения слагаемого с - отпирание транзистора 8. Откроется путь току через транзисторы 9 и 8, и на выходе суммы образуется иизкий уровень, соответствующий «НУЛЮ.

Рассмотрим другой пример, соответствующий .строке 8 таблицы. На входах схемы - слагаемые а «1, в - «1, с «1, необходимо получить S «1, Р «1. Так как

транзисторы У и 2 будут закрыты, образуются высокие уровни на выходе переноса Р н на выходе М, т. е. Р «1. Высокие уровни на выходе М и на входе прямого значения слагаемого с вызовут запирание транзисторов 9

и 10, и на выходе суммы S образуется высокий уровень, т. е. 5 «1.

Предмет изобретения

Одноразрядный сумматор, содержащий два полусумматора на включенных по двухъярусной схеме траизисторах с дополняющей симметрией, отличающийся тем, что, с целью снижения потребляемой мощности и умеиьщення числа информационных входов, в нем управляющие входы пар транзисторов п-тина первого яруса объединены в обоих полусумматорах с управляющими входами пар транзисторов р-типа второго яруса; управляющие

входы пары транзисторов п-типа второго яруса первого полусумматора соединены соответствеппо с одним «з его выходов и с одним из управляющих входов второго полусумматора, а также с выходом источника инверсного сигнала одного из слагаемых; объединенные управляющие входы первого полусумматора подключены к выходам источников виверспых сигналов второго и третьего слагаемых; свободный управляющий вход второго полусумматора .соединен с выходом источника прямого сигнала одного из слагаемых, а его выход подключен к выходному зажиму сигнала суммы; второй выход первого полусумматора соедннеи с выходным зажимом силнала переноса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 1966 |

|

SU184517A1 |

| ПОЛУСУММАТОР | 2015 |

|

RU2579980C1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| Накапливающий сумматор | 1990 |

|

SU1829031A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Блок переноса сумматора | 1988 |

|

SU1695293A1 |

| Преобразователь кода грея в двоичныйКОд | 1973 |

|

SU842783A1 |

Авторы

Даты

1972-01-01—Публикация