Известны .Параллельные частотные сумматоры, использующие .двух- и трехвходовые -ичйые одноразрядные частотные сумматоры.

Предлагаемое устройство отличается тем, что оно содержит дешифратор лереносов на фильтре верхних частот и детекторах для выявления частот, соответствующих наибольшей цифре, и -видеоимпульсных двоичных схемах совпадения и сэ-бирания, .выходы которых подключены к переключателям ко.ммутации частот в соответствии с -признаками переносов.

Это .позволяет увеличить его быстродействие.

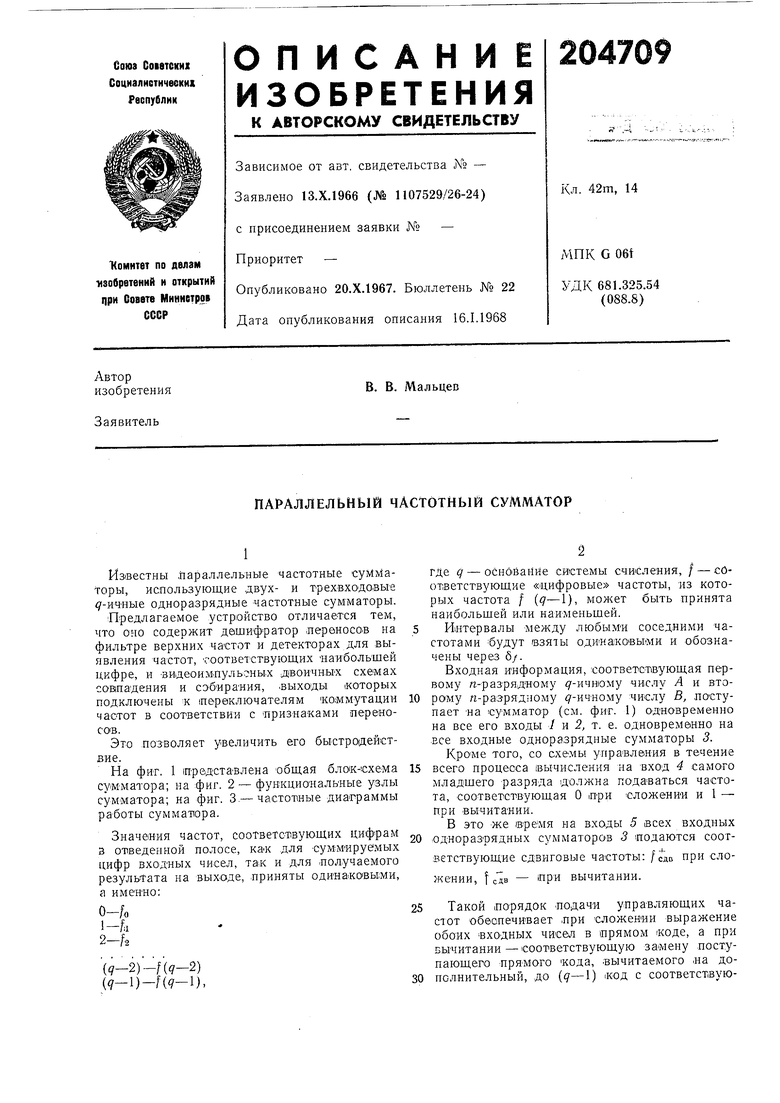

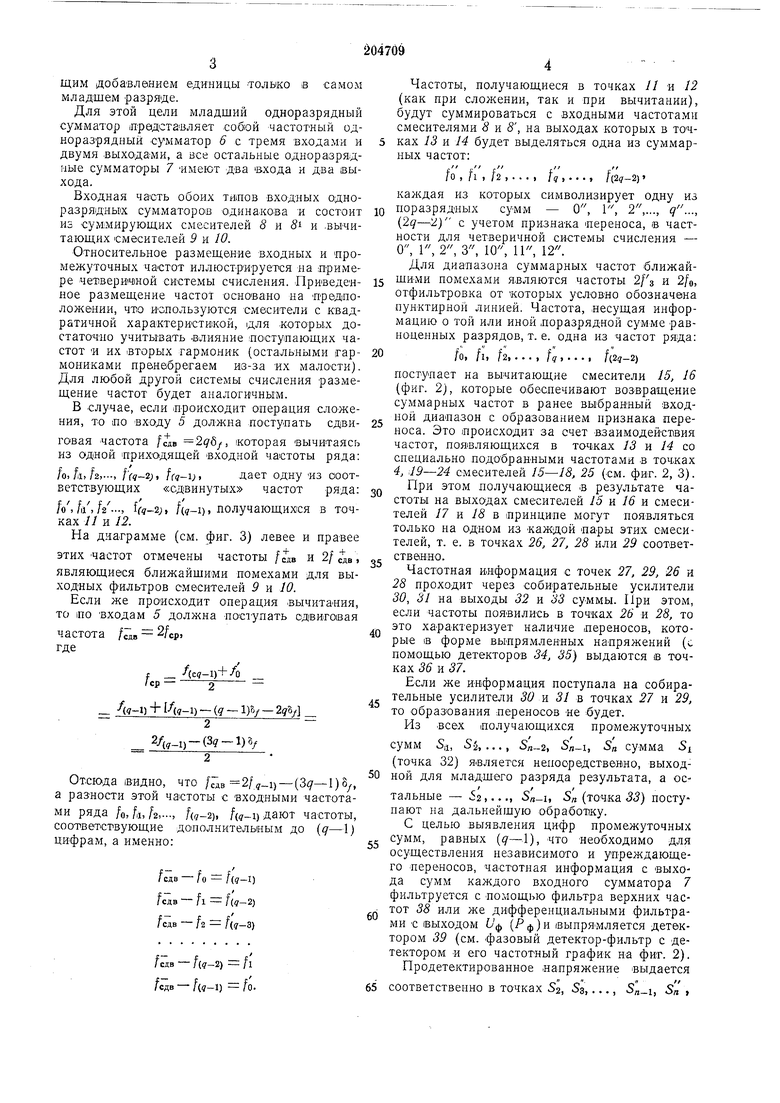

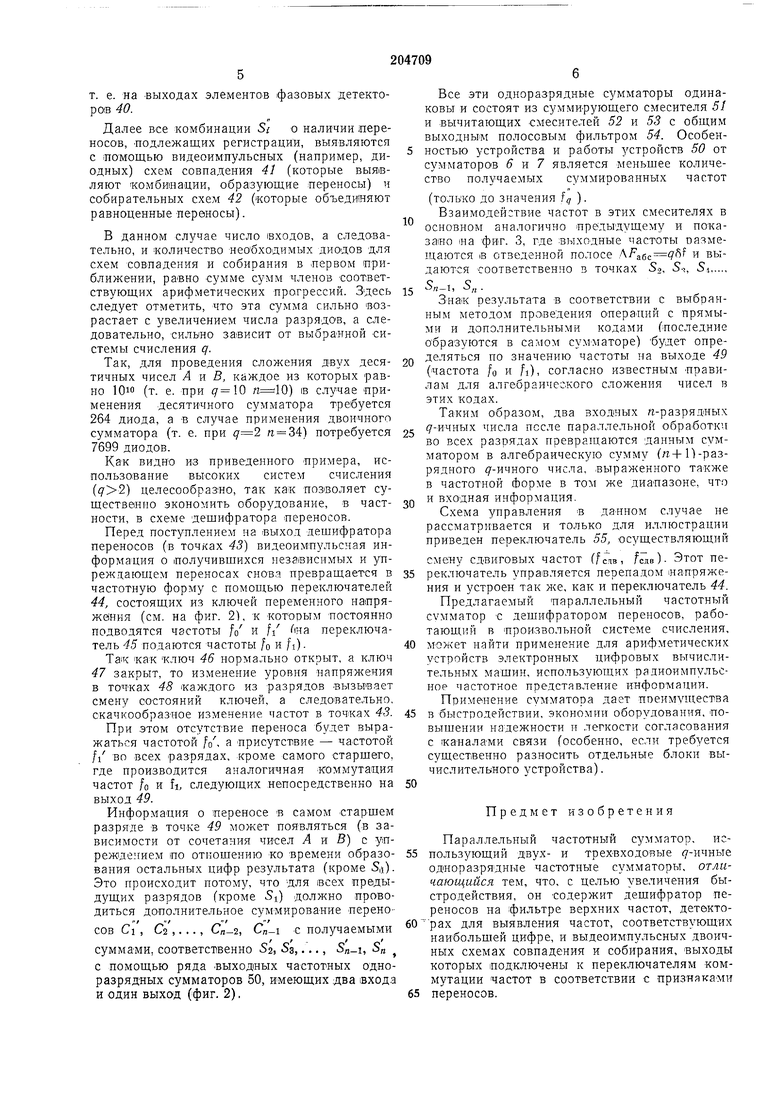

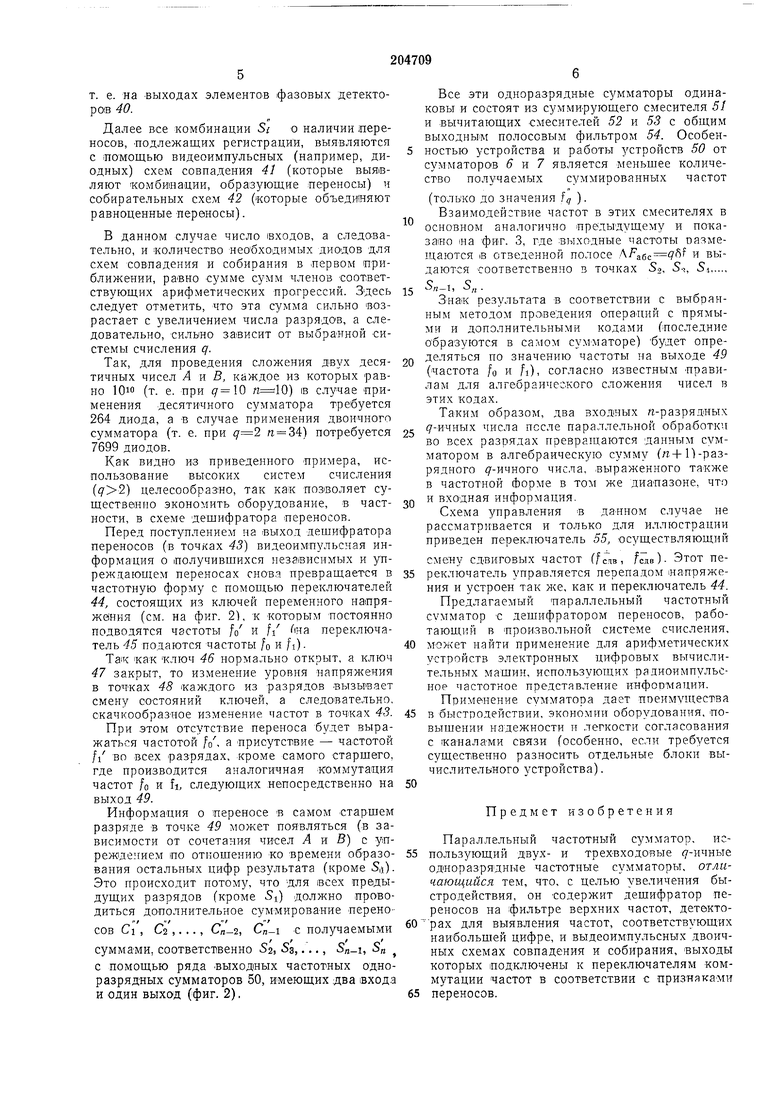

На фиг. 1 1П-редстаВлена общая блок-схема сумматора; на фиг. 2 - фувкциональные узлы сумматора; на фиг. 3 -частотные диаграммы работы сумматора.

Значения частот, соответспвующих цифрам в отведенной полосе, КНК для Сум-Мируемых цифр входных чисел, та;к и для -получаемого результата на выходе, приняты одинаковыми, я имеино:

0-/0 -fa

2-/2

где q - основание системы счисления, / - соответствующие «цифровые частоты, из которых частота / (д-1), может быть принята наибольшей или наименьшей. Интервалы между любыми соседними частотами будут взяты одинаковыми и обозначены через б/.

Входная информация, соответствующая первому и-разрядному (у-ичнюму числу А и второму «-разрядному -ичному числу В, поступает на сумматор (см. фиг. 1) одновременно на все его входы / и 2, т. е. одновременно на все входные одноразрядные сумматоры 3. Кроме того, со схемы управления в течение

всего процесса вычисления на вход 4 самого младщего разрЯДа подаваться частота, соответствующая О при сложении и 1 - при вычитании. В это же время на входы 5 всех входных

одноразрядных сумматоров 3 подаются соответствующие сдвиговые частоты: /сдв при сложении, f сдв - при вычитании.

Такой порядок лодачи управляющих частот обеспечивает лри -сложении выражение обоих входных чисел в прямом «оде, а при вычитании-соответствующую замену поступающего прямого кода, вычитаемого «а дощим добавлением единицы только в самом младшем разряде. Для этой цели младший одноразрядный сумматор лрадставляет собой частотный одноразрядный сумматор 6 с тремя входами и двумя .выходами, а все остальные однора13рядаые сумматоры 7 имеют два входа и два выхода. Входная часть обоих тилов входных одноразрядных сумматоров одинакова и состоит из Сум|МируЮШ,их смесителей S и Si и -вычитающих смесителей 9 и 10. Относительное размеш,бние входных и промежуточных частот иллюстрируется на лримере четверич1ной системы счисления. Приведенное размеш;ение частот основано на лредноложении, что ионользуются смесители с квадратичной характеристикой, для «оторыл достаточно учитывать влияние ;постуиаюш,их частот И их вторых гармоник (остальными гармониками ирбнебрегаем из-за их малости). Для любой другой системы счисления размещение частот будет аналогичным. В случае, если происходит онерация сложения, то 1по входу 5 должна поступать сдвиговая частота /ia 2q8f, которая вычитаясь из одной приходящей входной частоты ряда: fo,k,f2,.-, f(q-2), f(),дает одну «3 ооответствующих «сдвинутых частот ряда: /о, fd,/г..., , f(Vi), получающихся в точках 7/ и 12. На диаграмме (см. фиг. 3) левее и правее этих -частот отмечены частоты /ыв и являющиеся ближайшими помехами для выходных фильтров смесителей 9 и 10. Если же происходит операция вычитания, то 100 входам 5 должна поступать сдвиговая частота 2/ср, где f - (:g-i) /ср -2 ) + I/(g-l) (д- 1)В/ - 2qbf 2 ()г Отсюда 1ВИДНО, что /ив ) -()8, а разности этой частоты с входными частотами ряда /о, fii,/2,-.., /(-2), /(1)дают частоты, соответствующие дополнительным до (q-1) цифрам, а именно: / сдв - 10 /(-) /сдв - /1 f(-2) /сдв - f 2 f(-3) 4 Частоты, получающиеся в точках // и 12 (как при сложении, так и при вычитании), будут суммироваться с входными частотами смесителями S и 8, на выходах которых в точках 13 и 14 будет выделяться одна из суммарных частот: /о , f 1 , /2 , . . . , /у , . . . , f () каждая из которых символизирует одну из поразрядных сумм - О, Г , 2,..., q..., {2q-.2) с учетом признака переноса, s частности для четверичной системы счисления - О, 1, 2, 3, 10, 11, 12. Для диапазона суммарных частот ближайши-ми помехами являются частоты 2/з и 2/о, отфильтровка от которых усл-овяо обозначена пунктирной линией. Частота, несущая информацию о той или иной поразрядной сумме равноценных разрядов, т. е. одна из частот ряда: /о, fi, fa,..., /,..., /(27-2) поступает на вычитающие смесители 15, 16 (фиг. 2), которые обеспечивают возвращение суммарных частот в ранее выбранный входной диапазон с образованием признака переноса. Это Происходит за счет взаимодейст1вия - частот, появляющихся в точках 13 и 14 со специально подобранными частотами в точках 4, .19-24 смесителей 15-18, 25 (см. фиг. 2, 3). При этом получающиеся в результате частоты на выходах смесителей 15 и 16 ji смесителей /7 и в принципе могут появляться только на одном из -каждой пары этих смесителей, т. е. в точках 26, 27, 28 или 29 соответственно. Частотная информация с точек 27, 29, 26 н 28 проходит через собирательные усилители 30, 31 на выходы 32 и 33 суммы. При этом, если частоты появились в точках 26 и 28, то это характеризует наличие переносов, которые в форме выпрямленных напряжений (с помощью детекторов 34, 35) выдаются в точках 55 и 37. Если же информация поступала на собирательные усилители 30 Л 31 в точках 27 и 29, то образования переносов не будет. Из всех получающихся промежуточных сумм S,i, Ss, .,,, 5л-2, , Sn сумма S (точка 32) является непосредственно, выходной для младшего разряда результата, а остальные - б2,..., , 5л (точка ) поступают на дальнейшую обработ1ку. С целью выявления цифр промежуточных сумм, равных (q-1), что необходимо для осуществления независимого и упреждающего переносов, частотная информация с выхода сумм каждого входного сумматора 7 фильтруется с помощью фильтра верхних частот 38 или же дифференциальными фильтрами с выходом Оф (/ф)и вьшрямляется детектором 39 (см. фазовый детектор-фильтр с детектором и его частотный график на фиг. 2). Продетектированное напряжение выдается

т. е. на выходах элементов фазовых детекторов 40.

Далее все комбинации S{ о наличии переносов, подлежащих регистрации, выявляются с помощью видеоимпульсных (например, диодных) схем совпадения 41 (которые выявляют комбинации, образующие переносы) и собирательных схем 42 (которые объединяют равноценные переносы).

В данном случае число входов, а следовательно, и количество необходимых диодов для схем совпадения и собирания в первом приближении, равно сумме сумм членов соответствующих арифметических прогрессий. Здесь следует отметить, что эта сумма сильно возрастает с увеличением числа разрядов, а следовательно, сильно зависит от выбранной системы счисления q.

Так, для проведения сложения двух десятичных чисел А и В, каждое из которых равно IQio (т. е. при 10 ) в случае применения десятичного сумматора требуется 264 диода, а в случае применения двоичного сумматора (т. е. при п 34) потребуется 7699 диодов.

Как видно из приведенного примера, использование высоких систем счисления () целесообразно, так позволяет существенно экономить оборудование, в частности, в схеме дещифратора переносов.

Перед поступлением на выход дешифратора переносов (в точках 43) видеоимпульсная информация о получившихся независимых и упреждающем переносах снова превращается в частотную форму с помощью переключателей 44, состоящих из ключей переменного наоряже1ння (см. на фиг. 2), к которым постоянно подводятся частоты fo и f/ fea переключатель 45 подаются частоты /о и fi).

TaiK 1как ключ 46 нормально открыт, а ключ 47 закрыт, то изменение уровня напряжения в точках 48 каждого из разрядов вызывает смену состояний ключей, а следовательно, скачкообразное изменение частот в точках 43.

При этом отсутствие переноса будет выражаться частотой fo. а присутствие - частотой // во всех разрядах, кроме самого старщего, где производится аналогичная коммутация частот fo и fi, следующих непосредственно на выход 49.

Информация о переносе в самом старшем разряде в точке 49 может появляться (в зависимости от сочетания чисел Л и S) с упреж1де 1ием по отношению ко времени образования остальных цифр результата (кроме S,). Это происходит потому, что для всех предыдущих разрядов (кроме Si) должно проводиться дополнительное суммирование переносов Ci , Сз,..., , Сл-1 с получаемыми суммами, соответственно Sz, 83,..., Sn-г, Sn с помощью ряда выходных частотных одноразрядных сумматоров 50, имеющих два входа и один выход (фиг. 2).

Все эти одноразрядные сумматоры одинаковы и состоят из сумми-рующего смесителя 51 и вычитающих смесителей 52 -к 53 с общим выходным полосовым фильтром 54. Особенностью устройства и работы зстройств 50 от сумматоров (5 и 7 является меньщее количество получаемых суммированных частот

(только до значения fg ).

Взаимодействие частот в этих смесителях в

0 основном аналогично предыдущему и показано 1на фиг. 3, где выходные частоты размещаются в отведенной полосе .Рабс и выдаются соответственно в точках 5,, 5т, 5,..., 5„„1, 5„ .

5

Знак результата в соответствии с выбранным методом проведения операпий с прямыми и дополнительными кодами (последние образуются в самом сумматоре) будет определяться по значению частоты на выходе 49

0 (частота fo и fi), согласно известным правилам для алгебраического сложения чисел в этих кодах.

Таким образом, два входных «-разрядных 9-ичных числа после параллельной обработки

5 во всех разрядах превращаются данным сумматором в алгебраическую сумму (л+П-разрядного -ичного числа, выраженного также в частотной форме в том же диапазоне, что и входная информация.

0

Схема управления в данном случае не рассматривается и только для иллюстрации приведен переключатель 55, осуществляющий

смену сдвиговых частот (fens, fcis). Этот пе5реключатель управляется перепадом напряжения и устроен так же, как и переключатель 44.

Предлагаемый параллельный частотный сумматор с дешифратором переносов, работающий в произвольной системе счисления, может найти применение для арифметических

0 устройств электронных цифровых вычислительных машин, использующих радиоимпульсное частотное представление инфоомации.

Применение сумматора дает преимущества в быстродействии, экономии оборудования, по5вышении надежности и легкости согласования с каналами связи (особенно, если требуется существенно разносить отдельные блоки вычислительного устройства).

0

Предмет изобретения

Параллельный частотный сумматор, использующий двух- и трехвходовые (/Ичные одноразрядные частотные сумматоры, отличающийся тем, что, с целью увеличения быстродействия, он содержит дещифратор переносов на фильтре верхних частот, детекторах для выявления частот, соответствующих наибольшей цифре, и выдеоимпульсньтх двоичных схемах совпадения к собирания, выходы которых подключены к переключателям коммутации частот в соответствии с признаками переносов.

1 Z

D .щ I t feif ,-Щ tb. x I Iwlj,/

if 11 и (f

У яУ

.

Л

W

( И i И. «4rt: «-ii « jjhj Ji« I g Ea Ш

Л

. а. iMotuHOCmb „,„012

- . I I

. fcdf 2qJf

Частота

fo fifz fftf-nfs

22 I-(Ч-)

fk-n 4

J9

,.

-.f4-2fa

fi T-n-r

f- ofifz i

o

f

o

fcf,

0,

T-n-r-

/Tfrr

--rrrTi 2f,

ti-tfy f fi/S.J

Даты

1967-01-01—Публикация