Известно устройство для преобразования двоично-десятичного кода целых чисел в двоичный код, содержащее сдвиговой регистр кода преобразуемого числа, шифратор, двоичный параллельный сумматор и узел управления.

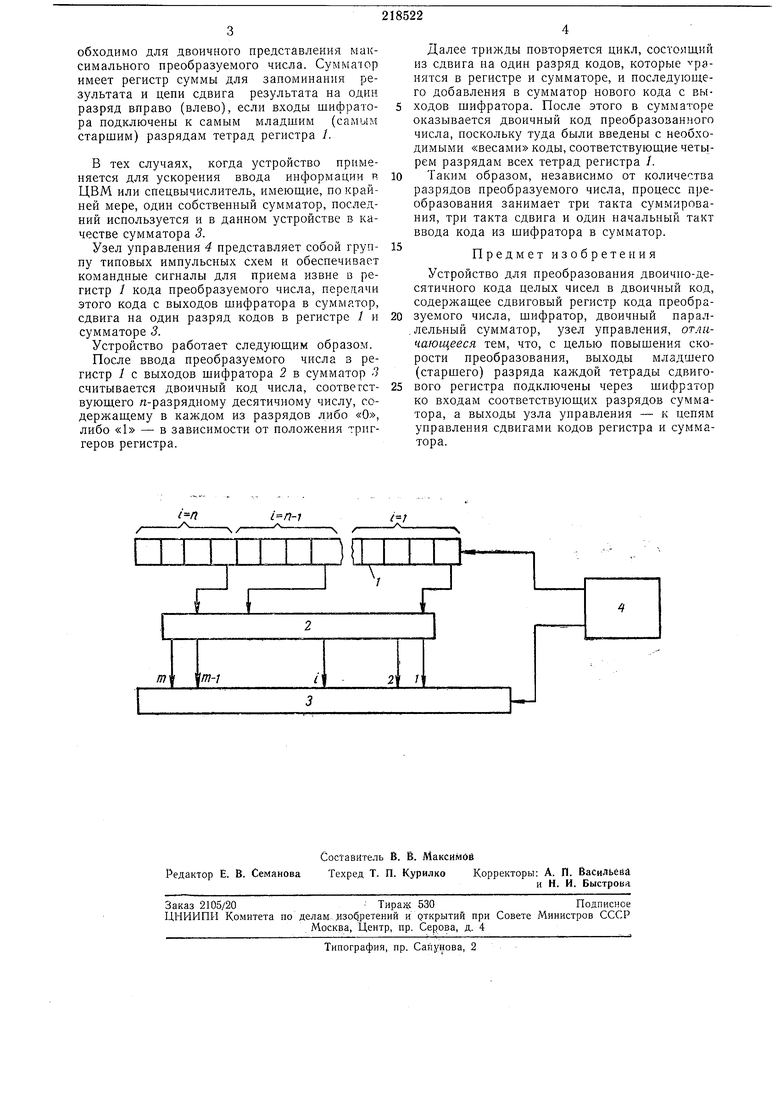

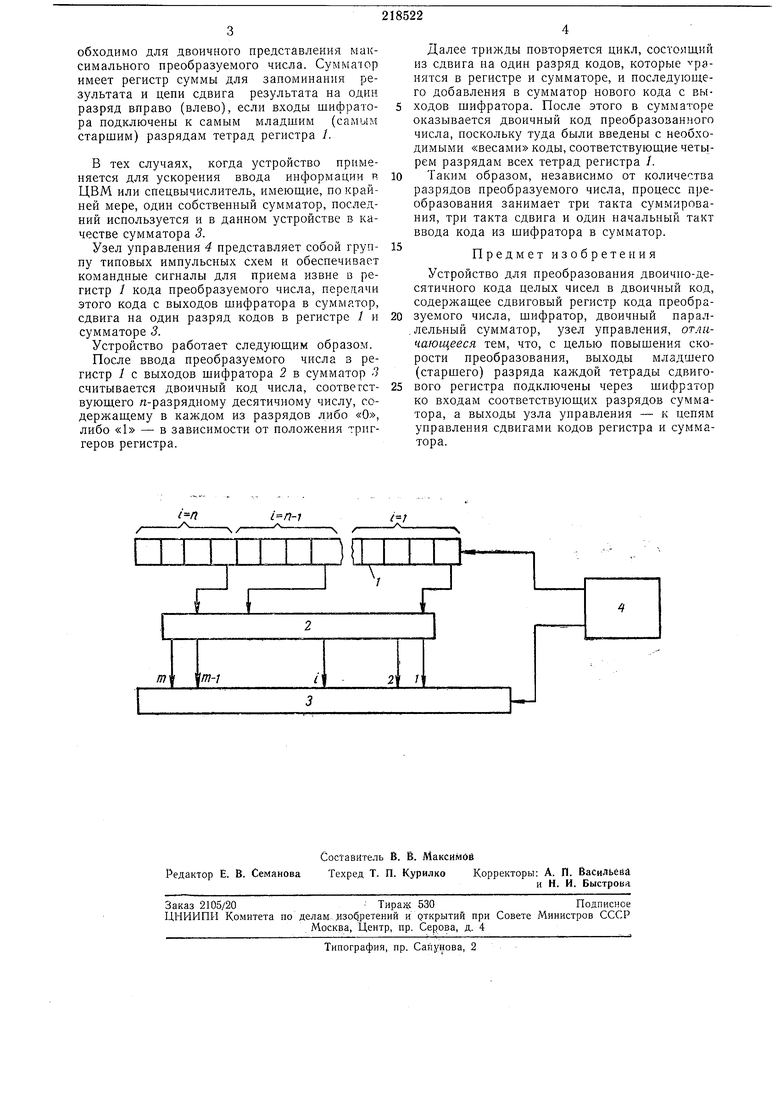

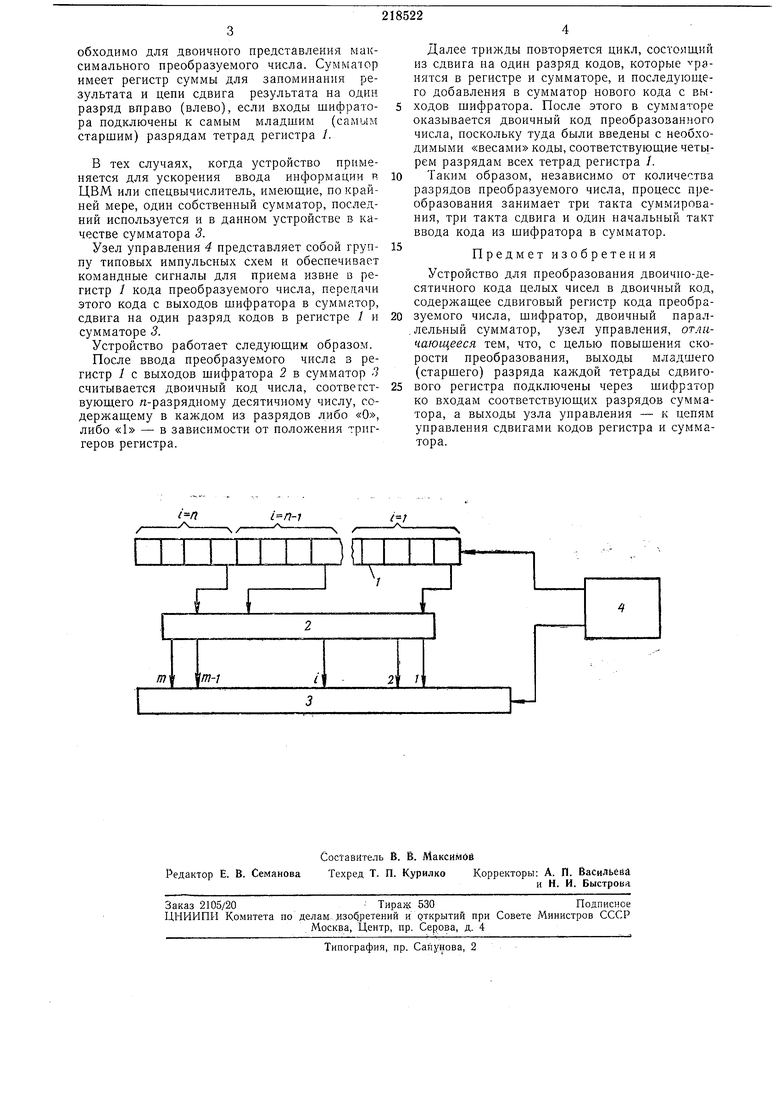

Предлагаемое устройство отличается от известных тем, что выходы младшего (старшего) разряда каждой тетрады сдвигового регистра подключены через шифратор ко входам соответствующих разрядов сумматора, а выходы узла управления - к цепям управления сдвигами кодов регистра и сумматора. Это позволяет повысить скорость преобразования. Функциональная схема устройства изображена на чертеже.

Устройство состоит из сдвигового регистра У, шифратора 2, двоичного параллельного сумматора 3 и узла управления 4.

Сдвиговый регистр, служащий для записи двоично-десятичного кода преобразуемого числа, разделен на тетрады (четверки разрядов), количество которых равно максимально возможному количеству десятичных разрядов п преобразуемого числа. Таким образом, регистр имеет 4/г разрядов. Для двоично-десятичного представления чисел чаще всего используется код 8 4-2-1, применительно к которому и ведется дальнейшее описание. Однако с небольшими усложнениями это устройство может использоваться и для других типов кода (например, 2-4-2-1). Регистр / имеет цепи для сдвига записанного в нем когда на один разряд вправо (если преобразование начинается от младших разрядов тетрад), или на один разряд влево (если оно начинается от старших разрядов)

Шифратор 2 включает в себя группу логических схем с буферными каскадами и имеет

п (по числу те1рад) входов и m выходов, где т - число разрядов двоичного кода, необходимое для представления двоично-десятичного кода. Б каждой из п тетрад зафиксирован код 0001. Каждый из входов шифратора подключается к выходу триггера одного разряда (самого младшего или самого старшего) соответствующей ему тетрады.

На т выходах шифратора образуется параллельный двоичный код суммы (взятой по

всем тетрадам), код произведений двоичного представления числа 10 (где i - номер тетрады; t l-f-n) на цифру, содержащуюся в подключенном к шифратору разряде г-й тетрады.

Каждый из выходов шифратора подключается к входному вентилю соответствуюи1его разряда сумматора 3 для считывания в сумматор кода шифратора. Параллельный двоичный сумматор 3 содеробходимо для двоичного представления максимального преобразуемого числа. Сумматор имеет регистр суммы для запоминания результата и цепи сдвига результата на один разряд вправо (влево), если входы шифратора подключены к самым младшим (самым старшим) разрядам тетрад регистра 1.

В тех случаях, когда устройство применяется для ускорения ввода информации в ЦВМ или спецвычислитель, имеющие, по крайней мере, один собственный сумматор, последний используется и в данном устройстве в качестве сумматора 3.

Узел управления 4 представляет собой группу типовых импульсных схем и обеспечивает командпые сигналы для приема извне в регистр / кода преобразуемого числа, передачи этого кода с выходов шифратора в сумматор, сдвига на один разряд кодов в регистре / и сумматоре 3.

Устройство работает следуюш,им образом.

После ввода преобразуемого числа з регистр 1 с выходов шифратора 2 в сумматор 3 считывается двоичный код числа, соответствующего л-разрядпому десятичному числу, содержащему в каждом из разрядов либо «О, либо «1 - в зависимости от положения триггеров регистра.

Далее трижды повторяется цикл, состоящий из сдвига на один разряд кодов, которые ранятся в регистре и сумматоре, и последуюп его добавления в сумматор нового кода с выходов щифратора. После этого в сумматоре оказывается двоичный код преобразованного числа, поскольку туда были введены с необходимыми «весами коды, соответствующие четь1рем разрядам всех тетрад регистра /. Таким образом, независимо от количества разрядов преобразуемого числа, процесс преобразования занимает три такта суммирования, три такта сдвига и один начальный такт ввода кода из шифратора в сумматор.

гги

Предмет изобретения

Устройство для преобразования двоично-десятичного кода целых чисел в двоичный код, содержащее сдвиговый регистр кода преобразуемого числа, шифратор, двоичный параллельный сумматор, узел управления, отличающееся тем, что, с целью повышения скорости преобразования, выходы младшего (старшего) разряда каждой тетрады сдвигового регистра подключены через шифратор ко входам соответствующих разрядов сумматора, а выходы узла управления - к цепям управления сдвигами кодов регистра и сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1978 |

|

SU752323A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ПРАВИЛЬНОЙ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1972 |

|

SU331382A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ В ДВОИЧНЫЕ | 1972 |

|

SU329525A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

Даты

1968-01-01—Публикация