Предложенное устройство предназначено для умножения десятичных чисел, выраженных в фазо-импульсном коде.

Как и известные аналогичные устройства оно содержит преобразователи фазо-импульсного кода в пространственный и обратно, устройство формирования сигналов произведения и переноса в старший разряд и дешифратор пар сомножителей и отличается тем, что каждый элемент «И» преобразователей фазо-импульсного кода сомножителей в пространственно-импульсный связан по одному входу с шиной представления цифры сомножителя, по другому - с шиной представления фазо-импульсных сигналов цифр 0+9, а по выходу - с запоминающим элементом указанного преобразователя. Выходы запоминающих элементов, соответствующие парам сомножителей, из которых хотя бы один равен нулю, подключены на вход устройства формирования сигналов произведения и переноса, а выходы остальных запоминающих элементов соединены с элементами «И» дешифратора пар сомножителей; выходы последнего, соответствующие парам сомножителей, не равных нулю, соединены соответственно с двумя элементами «ИЛИ», содержащимися в устройствах формирования сигналов произведения и переноса; выходы элементов «ИЛИ» подключены ко входам запоминающих элементов преобразователей пространственно-импульсного кода в фазо-импульсный код произведения и переноса, вторые входы указанных запоминающих элементов связаны с шиной представления фазо-импульсных сигналов цифр 0+9, а выходы соединены с элементами «ИЛИ», выходы которых соответствуют произведению и переносу в следующий разряд.

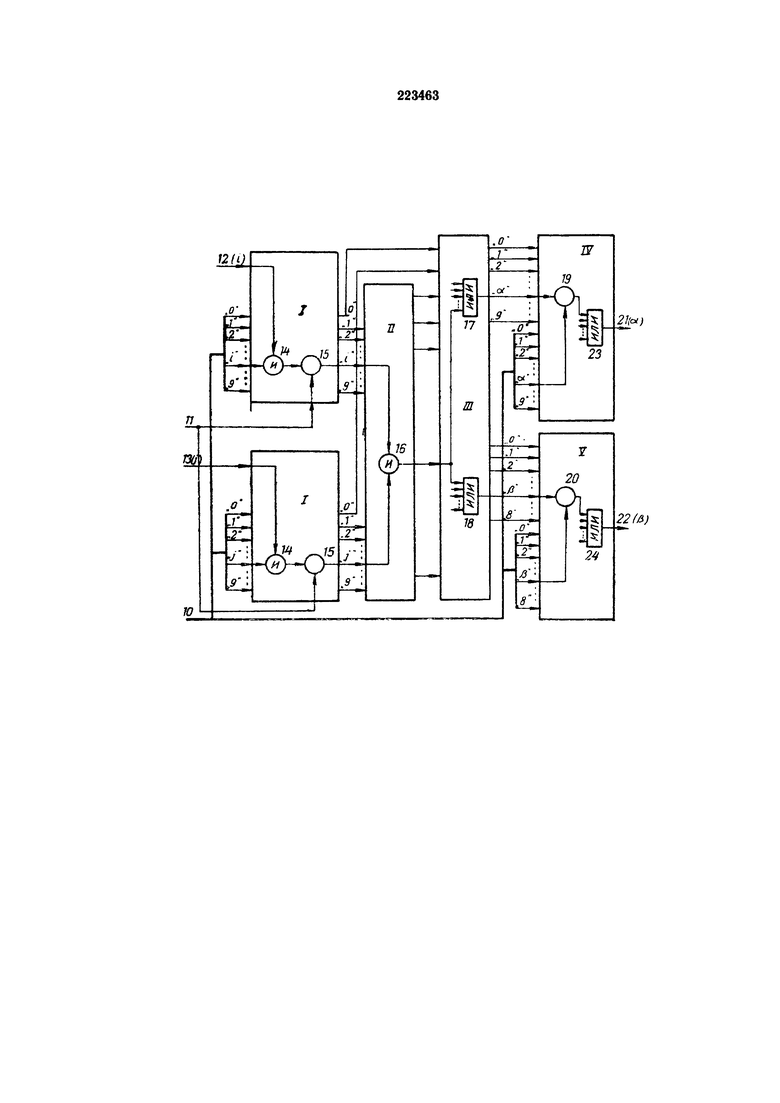

Схема предложенного устройства изображена на чертеже, где:

I - преобразователи фазо-импульсного кода сомножителей в пространственно-импульсный;

II - дешифратор пар сомножителей;

III - устройство формирования сигналов произведения и переноса;

IV, V - преобразователи пространственно-импульсного кода произведения и переноса в фазо-импульсный код.

Схема работает следующим образом.

На преобразователи I на входы «0», «1»…«i»…«9» и «0», «1»…«j»…«9» с шины 10 поступают цифры (константы) «0» «1»…, «9» в фазо-импульсном представлении.

По проводу 11 на преобразователи I поступает сдвинутая опорная производительность импульсов.

Фазо-импульсные сигналы цифр сомножителей i и j поступают по проводам 12 и 13 соответственно на один из двух входов всех элементов «И» 14 в схемах I. Каждая схема I содержит десять элементов «И». На другие входы элементов «И» по шине 10 поступают фазо-импульсные сигналы цифр от «0» до «9», причем каждый сигнал поступает на отдельный элемент «И». Совпадение двух одинаковых сигналов на входе одного из элементов «И» в каждой из схем I приводит к тому, что на выходе элемента «И» с i-ми входными сигналами в одной схеме I и на выходе элемента «И» с j-ми входными сигналами в другой схеме I появляются сигналы совпадения, являющиеся пространственно-импульсными представлениями цифр, поданных по проводам 12 и 13. Эти сигналы поступают на обмотки записи элементов 15 в схемах I и запоминаются в них. Так как количество возможных значений цифр i и j равно десяти, то и каждая схема I содержит по десять элементов 15.

После того, как в схемах I на указанных элементах 15 произойдет запоминание пространственно-импульсных представлений цифр i и j, на обмотки считывания всех элементов 15 в схемах I по проводу 11 поступает импульс сдвинутой опорной последовательности. Этот импульс возвращает i-й и j-й элементы 15 в исходное состояние. При этом на i-м и j-м выходных проводах соответствующих схем I появляются два импульсных сигнала, которые при i≠o и j≠0 поступают на входы одного из элементов «И» 16 в схеме II. В том случае, когда i=0 или j=0, импульсный сигнал, представляющий эту цифру, подается с выхода схемы I непосредственно на схему III. Поскольку из ста возможных сочетаний значений цифр i и j девятнадцать сочетаний приходятся на случай, когда i=0, j=0, либо i=0 и j=0 одновременно, то количество элементов «И» в схеме III равно восьмидесяти одному.

Импульсный сигнал, полученный либо в схеме II на выходе соответствующего элемента «И» 16, либо со схем I (когда i=0, j=0, либо i=j=0), поступает на вход схемы III. Для преобразования этого сигнала, представляющего произведение входных цифр i и j, в два импульсных сигнала, представляющих цифры α и β (сигналы произведения и переноса), он подается на два элемента «ИЛИ» 17 и 18. Таким образом, в схеме III имеется две группы элементов «ИЛИ». На входы каждого из элементов первой группы подаются только те импульсные сигналы с выхода схемы II (либо с выхода схем I), которые представляют одну и ту же десятичную цифру α; на входы каждого из элементов «ИЛИ» второй группы поступают только те сигналы с выхода схемы II (либо с выхода схем I), которые представляют одну и ту же десятичную цифру β. В связи с тем, что цифра α может в общем случае принимать одно из десяти значений, то и количество элементов «ИЛИ» в первой группе равно десяти. Вследствие того, что цифра переноса β может принимать только девять значений (так как значения β=9 быть не может), а случай, когда перенос β=8, бывает только при одном сочетании цифр сомножителей, а именно, когда i=j=9, и в этом случае также нет надобности в применении элемента «ИЛИ», то общее количество элементов «ИЛИ» во второй группе равно восьми.

С выхода схемы III пространственно-импульсные представления цифр α и β поступают на обмотки записи α-го и β-го запоминающих элементов (19, 20) в схемах IV и V соответственно. По приведенным выше соображениям схема IV содержит десять элементов 19, а схема V - девять элементов 20.

После того, как в схемах IV и V на элементах 19 и 20 произошло запоминание импульсных представлений цифр α и β, на обмотки считывания всех элементов 19 в схеме IV по шине 10 поступают фазо-импульсные сигналы цифр от «0» до «9» и на обмотки считывания всех элементов 20 в схеме V - сигналы цифр от «0» до «8», причем каждый сигнал поступает на отдельный элемент. Благодаря этому α-й элемент 19 в схеме IV и β-й элемент 20 в схеме V возвращаются в исходное состояние, и на их выходных обмотках появляются два импульса с фазами α и β соответственно.

Эти фазо-импульсные сигналы поступают на выходные провода 21 и 22 устройства умножения через два элемента «ИЛИ» 23, 24, которые собирают десять возможных фазо-импульсных сигналов цифр произведения по mod 10 с выхода десяти элементовв схеме IV и девять возможных фазо-импульсных сигналов цифр переноса с выхода девяти элементов 20 в схеме V.

Полученные фазо-импульсные сигналы в проводах 21 (α) и 22 (β) являются результатом умножения двух десятичных цифр i и j, поданных на вход матрицы умножения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ | 1973 |

|

SU409222A1 |

| МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1969 |

|

SU244713A1 |

| Матричное устройство для умножения | 1979 |

|

SU842800A1 |

| Устройство для контроля умножения по модулю три | 1982 |

|

SU1072049A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧИСЕЛ, НРЕДСТАВЛЕННЫХ ФАЗОИМПУЛЬСНЫМИ ДЕСЯТИЧНЫМИ КОДАМИ | 1973 |

|

SU384104A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

Устройство для умножения десятичных чисел, выраженных в фазо-импульсном коде, содержащее преобразователи фазо-импульсного кода в пространственный и обратно, устройство формирования сигналов произведения и переноса в старший разряд и дешифратор пар сомножителей, отличающееся тем, что, с целью упрощения устройства и повышения точности, каждый элемент «И» преобразователей фазо-импульсного кода сомножителей в пространственно-импульсный связан по одному входу с шиной представления цифры сомножителя, по другому - с шиной представления фазо-импульсных сигналов цифр 0+9, а по выходу - с запоминающим элементом указанного преобразователя; выходы запоминающих элементов, соответствующие парам сомножителей, из которых хотя бы один равен нулю, подключены на вход устройства формирования сигналов произведения и переноса, а выходы остальных запоминающих элементов соединены с элементами «И» дешифратора пар сомножителей, выходы которого, соответствующие парам сомножителей, не равных нулю, соединены соответственно с двумя элементами «ИЛИ», содержащимися в устройствах формирования сигналов произведения и переноса; выходы элементов «ИЛИ» подключены ко входам запоминающих элементов преобразователей пространственно-импульсного кода в фазо-импульсный код произведения и переноса, вторые входы указанных запоминающих элементов связаны с шиной представления фазо-импульсных сигналов цифр 0+9. а выходы соединены с элементами «ИЛИ», выходы которых соответствуют произведению и переносу в следующий разряд.

Авторы

Даты

1968-11-05—Публикация

1967-06-07—Подача