Известны устройства для автоматического фазирования, содержащие регистр сдвига, счетчик, делитель частоты, схему сложения по модулю два, блок выделения местного сигнала, генератор импульсов и логические схемы.

Предложенное устройство отличается тем, что в нем выход генератора импульсов подсоединен ко входу делителя частоты, ко входам триггеров, ко входу блока выделения местного сигнала, ко входам схемы «И» и схемы сложения по модулю два и ко входам линии задержки, выход которой подключен к триггеру и к схеме совпадения. Второй вход схемы совпадения через схему «ИЛИ» соединен с выходами делителя частоты, а выход схемы совпадения подсоединен ко второму триггеру. Выходы триггеров подключены соответственно ко входам реверсивного счетчика, выходы которого соединены со входами блока выделения местного сигнала. Выход этого блока подключен ко входу схемы «ИЛИ», ко входу делителя частоты и ко входу регистрирующего блока.

Такое выполнение устройства позволяет сократить время фазирования.

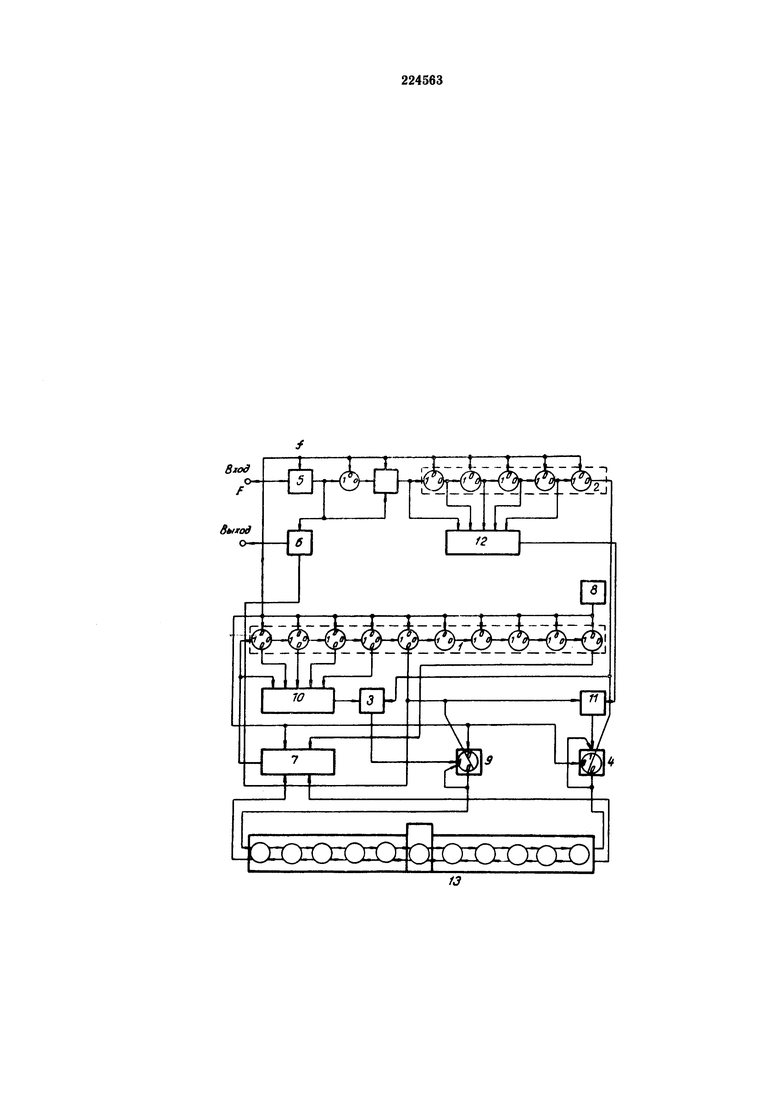

На чертеже изображена схема описываемого устройства.

При отсутствии краевых искажений входного сигнала и при точном равенстве длительностей элементарной информационной посылки и некорректированного цикла делителя 1 фазное соотношение основных сигналов таково, что моменту выхода очередного «дифференциала» с последней ячейки линии задержки 2 соответствует наличие единицы в средней ячейке делителя 1 (пятой по счету слева направо).

При этом выходные сигналы линии задержки 2 никакой логической работы не производят, так как в моменты их появления схема «И» 3 не возбуждена по второму ее входу, а в динамическом триггере 4 «1» отсутствует. В результате чего при точном фазовом балансе полезно функционируют только входное реле 5, регистрирующее устройство 6 и делитель 1 с блоком 7 выделения местного сигнала, питаемые генератором импульсов 8, причем корректирование делителя 1 не производится.

При возникновении фазового рассогласования, например, из-за неточности номиналов частот F и f появление информационных «дифференциалов» на выходе линии задержки не будет совпадать по времени с размещением «единицы» делителя в средней его ячейке.

Рассмотрим один из двух возможных случаев крайнего фазового рассогласования, когда появление очередного «дифференциала» на выходе линии задержки 2 совпало с записью «1» в первую ячейку делителя 1.

При этом «дифференциал» через схему «И» 3 записывает «1» в динамический триггер 9. Схема «И» 3 оказывается к этому подготовленной благодаря одновременному воздействию на другой ее вход выходного сигнала из блока 7, прошедшего через схему «ИЛИ» 10.

Очевидно, что динамический триггер 9 будет находиться в возбужденном состоянии ровно такое количество тактов частоты f, которое необходимо для перемещения «1» делителя 1, разрешившей функционирование триггера 9, до средней ячейки делителя 1, осуществляющей запрет функционирования триггера 9 (в рассмотренном примере -  тактов частоты f).

тактов частоты f).

Таким образом, при совпадении момента появления очередного «дифференциала» на выходе линии задержки 2 с одним из фазных состояний первой половины цикла делителя 1 возбуждается динамический триггер 9 на такое количество тактов частоты f, которое разделяет между собой моменты появления «дифференциала» на выходе линии задержки 2 и «1» в средней ячейке делителя 1. В этом смысле сигнал рассогласования (продолжительность возбужденного состояния триггера 9) прямо пропорционален величине фазового рассогласования с точностью до постоянной величины

При противоположном фазовом рассогласовании (выход «дифференциала» соответствует второй половине цикла делителя 1) устройство функционирует следующим образом.

Если в момент считывания «1» со средней ячейки делителя 1 очередной «дифференциал» размещен в любой из ячеек линии задержки 2, исключая последнюю, что соответствует появлению этого «дифференциала» на выходе линии задержки в пределах второй половины цикла делителя, то возбуждается динамический триггер 4. Возбуждение триггера 4 осуществляется благодаря тому, что на схему «И» 11 одновременно воздействуют выходной сигнал средней ячейки делителя 1 и скоммутированный через схему «ИЛИ» 12 соответствующий «дифференциал».

Очевидно, что триггер 4 будет находиться в возбужденном состоянии ровно столько тактов частоты f, сколько необходимо для перемещения «дифференциала», разрешившего возбуждение триггера 4, до конца линии задержки 2, поскольку запрет возбужденного состояния триггера 4 осуществляется выходным сигналом линии задержки 2.

Таким образом, в рассмотренном случае сигнал рассогласования (количество тактов возбужденного состояния триггера 4) также прямо пропорционален величине рассогласования с точностью до постоянной величины

В связи с этим в совокупности взаимодействий элементов предлагаемого устройства обнаруживается эффект линейного фазового детектирования.

Следует отметить, что возбуждения триггеров 9 и 4 являются событиями несовместимыми, так как они четко разграничены во времени серединой цикла делителя 1.

Каждый из триггеров управляет перемещением «1» вдоль реверсивного счетчика 13, причем один из триггеров смещает «1» вдоль счетчика 13 слева направо, а другой - в противоположном направлении.

Существенным является тот факт, что при каждом факте возбуждения одного из триггеров «1» перемещается вдоль реверсивного счетчика на количество тактов, пропорциональное величине мгновенного фазового рассогласования. Таким образом, при больших начальных фазовых рассогласованиях (в  цикла) для появления на выходе реверсивного счетчика 13 коррекционного эффекта достаточно двух информационных переходов, при минимальном же рассогласовании (в

цикла) для появления на выходе реверсивного счетчика 13 коррекционного эффекта достаточно двух информационных переходов, при минимальном же рассогласовании (в  цикла) количество переходов, приводящее к корректированию делителя 1, должно быть не менее

цикла) количество переходов, приводящее к корректированию делителя 1, должно быть не менее  (если длина плеч реверсивного счетчика 13 равна

(если длина плеч реверсивного счетчика 13 равна  ячейкам).

ячейкам).

При этом шаг корректирования во всех случаях остается неизменным.

Предлагаемое устройство обладает ускоренным начальным фазированием системы при вхождении в связь; неизменным шагом корректирования; высокой интегрирующей способностью при малых фазовых рассогласованиях; автоматической трансформируемостью коррекционных свойств в зависимости от величины среднего расхождения фактических значений сравниваемых скоростей. При близком соответствии сравниваемых скоростей исправляющая способность устройства близка к  при относительном расхождении скоростей в

при относительном расхождении скоростей в  от номинала предлагаемое устройство еще сохраняет работоспособность, но при меньшей исправляющей способности, если краевые искажения сигнала не превышают

от номинала предлагаемое устройство еще сохраняет работоспособность, но при меньшей исправляющей способности, если краевые искажения сигнала не превышают  от длительности элементарной посылки. В этом отношении предлагаемое устройство существенно превосходит известные, содержащие интеграторы такой же эффективности.

от длительности элементарной посылки. В этом отношении предлагаемое устройство существенно превосходит известные, содержащие интеграторы такой же эффективности.

Предлагаемое устройство обладает также «плавающей» установкой фазы стробирования (это свойство проявляется в том, что если сигнал имеет постоянное преобладание длительности посылок одной полярности, то стробирующие импульсы на устройстве 6 автоматически устанавливаются в такой фазе, что соответствуют серединам как укороченных, так и удлиненных посылок); высокой корректирующей способностью при редком заполнении сигнала переходами, что характерно, например, квантованному фототелеграфному сигналу.

При редком появлении переходов фазовый набег накапливается из-за отсутствия корректирования в интервалах времени, не заполненных переходами. Так как предлагаемое устройство обладает способностью компенсировать рассогласования большой величины с помощью малого количества переходов, то в этом отношении оно превосходит применяемые.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР ДЛЯ ОПРЕДЕЛЕНИЯ УСТОЙЧИВОСТИ ФАЗИРУЮЩИХ УСТРОЙСТВ С ДИСКРЕТНЫМ УПРАВЛЕНИЕМ | 1968 |

|

SU211151A1 |

| Устройство дискретного фазирования | 1980 |

|

SU1016847A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство тактовой синхронизации | 1980 |

|

SU938419A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| ВСЕСОЮЗН.АЯ ГAT:irriiG-ii:](Kn^ECHAeБ-^ | 1971 |

|

SU291357A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство для программного управления положением вала электродвигателя | 1977 |

|

SU708310A1 |

Устройство для автоматического фазирования, содержащее регистр сдвига, счетчик, делитель частоты, схему сложения по модулю два, блок выделения местного сигнала, генератор импульсов и логические схемы, отличающееся тем, что, с целью сокращения времени фазирования, в нем выход генератора импульсов подсоединен ко входу делителя частоты, ко входам триггеров, ко входу блока выделения местного сигнала, ко входам схемы «И» и схемы сложения по модулю два и ко входам линии задержки, выход которой подключен к триггеру и к схеме совпадения, второй вход схемы совпадения через схему «ИЛИ» соединен с выходами делителя частоты, а выход схемы совпадения подсоединен ко второму триггеру, выходы триггеров подключены соответственно ко входам реверсивного счетчика, выходы которого соединены со входами блока выделения местного сигнала, выход блока выделения местного сигнала подключен ко входу схемы «ИЛИ», ко входу делителя частоты и ко входу регистрирующего блока.

Авторы

Даты

1968-11-22—Публикация

1967-07-08—Подача