Известны системы модулей, реализующие определенные логические функции и имеющие малую логическую мощность.

Предлагаемая система отличается тем, что в ней внешние выводы узлов в строго фиксированном и одинаковом для каждого узла количестве имеют эквивалентное в пределах систем расположение, их последующее соединение непосредственно определено структурой устройства, а варьирование элементов, их относительное физическое расположение в узле и внутренняя коммутация узла обусловлены инвариантностью конструкции к схемам узлов, реализующим полный набор информационных функций.

Это позволяет сократить внешнюю коммутацию, обеспечить параллельное и независимое производство и контроль составных частей устройства, а также повысить эффективность эксплуатации готовых устройств.

Предлагаемая система узлов реализует максимально возможный уровень логической мощности, при котором еще сохраняется допустимая степень унификации вне зависимости от структурной реализации дискретного устройства.

Каждый из узлов указанной системы выполняет одну из совокупностей информационных функций - кодирование, декодирование, передачу, обработку и хранение информации, и система, таким образом, обеспечивает построение всех основных блоков устройств дискретного действия: регистров, счетчиков, сумматоров, каналов передачи информации, дешифраторов, шифраторов и устройств управления.

Для обеспечения возможности реализации дискретного устройства произвольной структуры на базе предлагаемой унифицированной системы узлов эти узлы конструктивно выполнены так, что внешние выводы изготавливаются в строго фиксированном и одинаковом для каждого узла количестве и имеют стандартное относительное расположение.

Каждый узел функционально представляет собой «черный ящик» со строго определенной системой входных и выходных контактов, несущих определенное логическое назначение вне зависимости от выбранного логического элемента, схемотехнических решений, технологического исполнения и внутренних технологических связей.

Предлагаемая система узлов вследствие сложности информационных функций и большой логической мощности существенно разгружает внешнюю (по отношению к узлу) коммутацию, поскольку значительная часть коммутационных линий располагается на самом узле.

Необходимое для создания дискретного устройства количество узлов изготавливается в производстве независимо от структурной схемы устройства и параллельно с разработкой последней. Большая, по сравнению с упомянутыми модулями, логическая мощность узлов позволяет в три-четыре раза повысить экономичность устройства в целом (расчеты производились для конкретного случая гибридной пленочной технологии).

Сборка и построение устройства из предварительно проверенных узлов высокой логической мощности также осуществляются с меньшей трудоемкостью.

Эксплуатационная надежность устройства, построенного на основе предлагаемой унифицированной системы узлов, существенно повышается вследствие уменьшения времени локализации ошибки с точностью до узла, что позволяет повысить частоту проведения профилактических работ.

Независимость конструктивно-функционального исполнения узла от типа логического элемента, схемотехнических решений и технологии изготовления обеспечивается варьированием относительного расположения элементов в узле и внутренних технологических связей между элементами.

Так, например, при выполнении узла из отдельных микросхем или в едином технологическом процессе изменяется расположение отдельных элементов, а внутренняя коммутация перераспределяется между технологией микросхемы и соединительной платы (однако это не отражается на внешней коммутации узла).

Новая система узлов приводит и к новому способу проектирования схем устройств дискретного действия, состоящего из двух этапов: разработки и изготовления функционально универсальной системы узлов с постоянным относительным расположением и количеством внешних выводов; непосредственно по структурной схеме устройства получают функциональную логическую схему из вышеуказанных узлов и таблицу соединений между узлами.

Таким образом, при предлагаемом способе выполнения дискретного устройства отпадает необходимость в одном из самых трудоемких этапов проектирования. Непосредственный переход от структурной схемы к функционально-логической схеме на узлах оказывается возможным благодаря тому, что каждый из узлов системы выполняет одну из совокупностей информационных функций - кодирование, декодирование, передачу, обработку и хранение информации, и система, таким образом, обеспечивает выполнение всех основных блоков устройств дискретного действия.

Поскольку структурная схема отражает информационно-логическую сущность проектируемого устройства, этап построения функциональной логической схемы следует сразу за этапом построения структурной схемы устройства.

Новый способ устраняет неоднозначность выполнения функционально-логической схемы устройства, сокращая трудоемкость его разработки и позволяя легко получать оптимальную схему.

Одновременно с этим количество ошибок и, следовательно, корректировок в первоначально разработанное и изготовленное устройство существенно сокращается, так как связи между узлами являются информационными, а большая часть проверок осуществляется на стадии изготовления узла, обладающего большой логической мощностью.

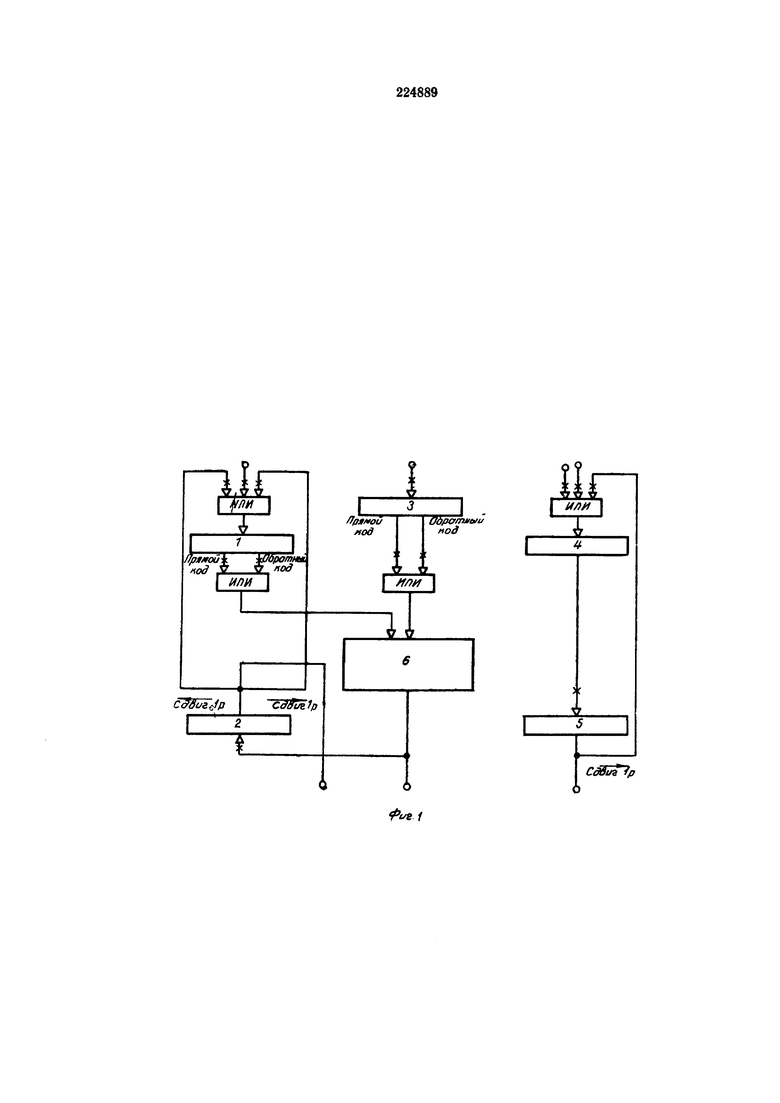

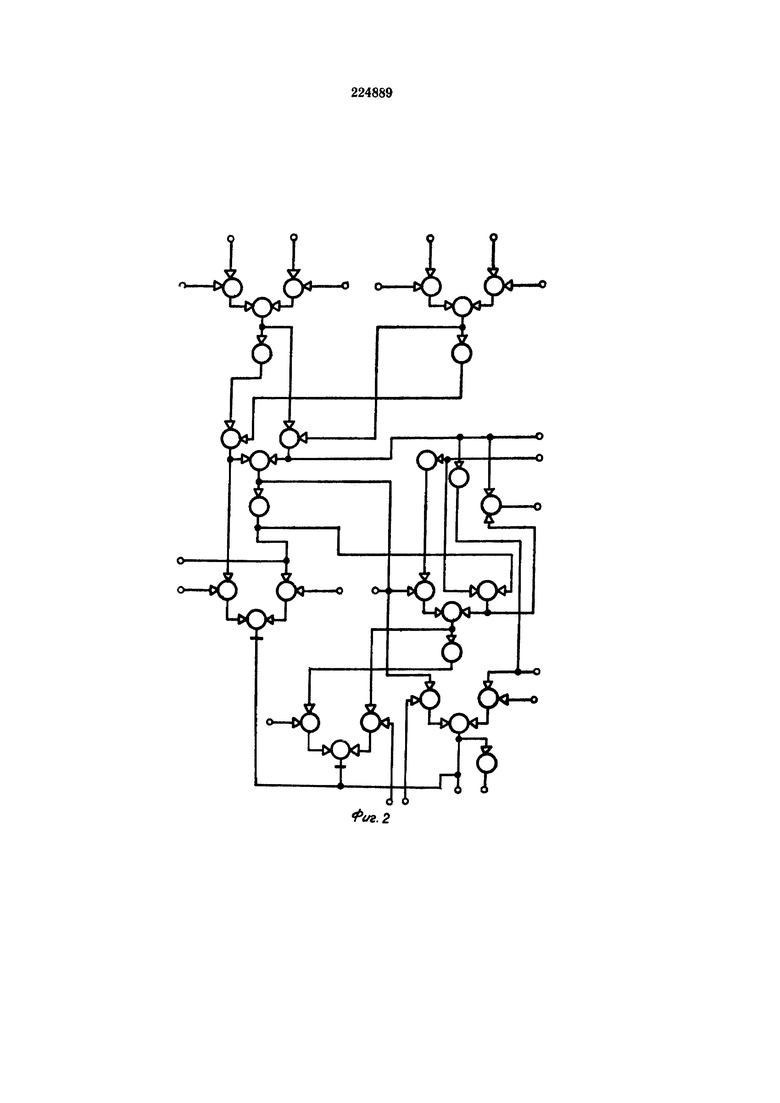

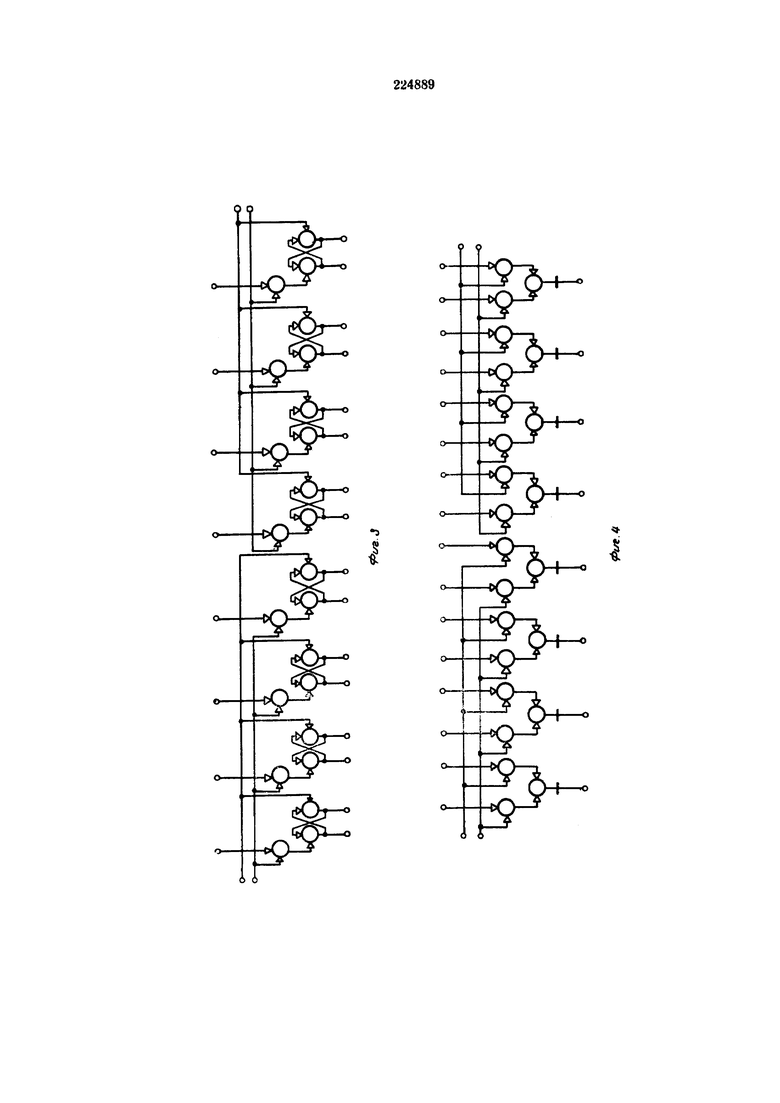

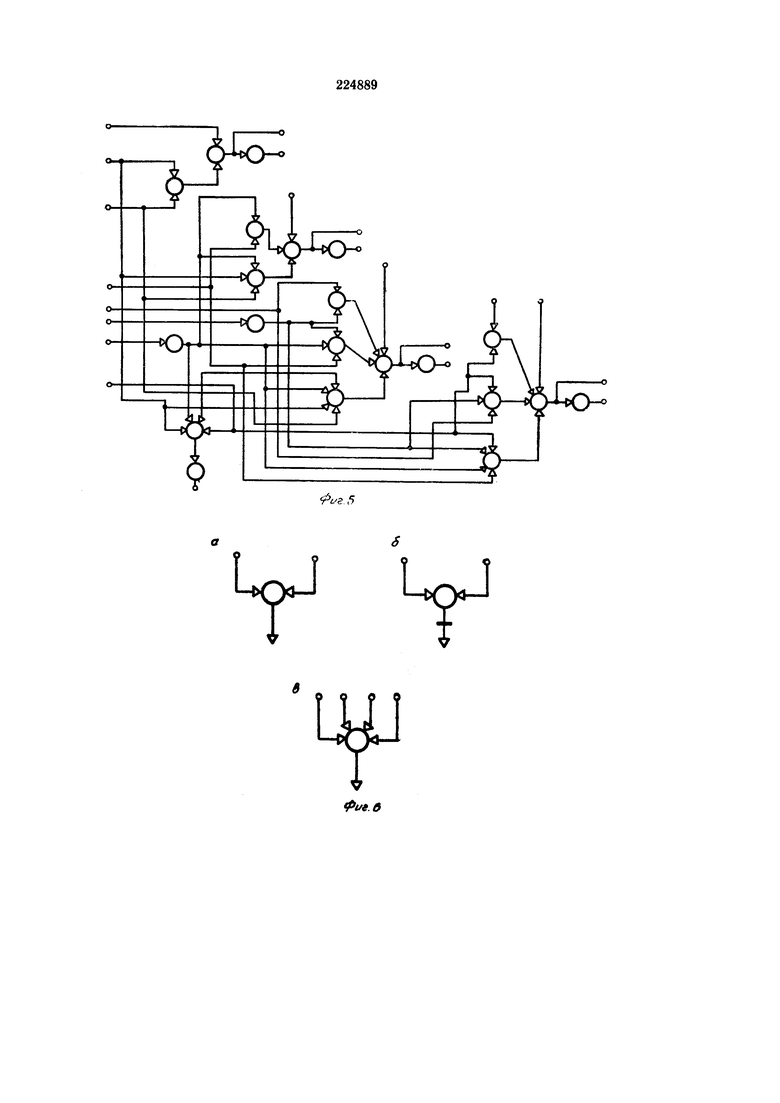

На фиг. 1 приведена структурная схема параллельного восьмиразрядного арифметического устройства (в качестве примера); на фиг. 2 - узел «Сумматор»; на фиг. 3 - узел «Регистр»; на фиг. 4 - узел «Шина»; на фиг. 5 - узел «Перенос сумматора»; на фиг. 6 - схемы «ИЛИ-НЕ».

Арифметическое устройство (фиг. 1) состоит из регистров 1-5 и сумматора 6 с параллельно-последовательным ускоренным переносом. Изображенная структурная схема должна производить операции сложения, вычитания, умножения, деления, а также логические операции поразрядных дизъюнкции, конъюнкции, сложения то модулю 2 и сравнения. При умножении множимое и множитель поступают в регистры 3 и 4 соответственно, а при делении - делимое и делитель в регистры 1 и 3 соответственно. Операнды всех остальных операций поступают в регистры 1 и 3. В регистрах 1 и 2 производится сдвиг делимого и частичных произведений, а в регистре 4 - сдвиг множителя.

Для реализации структурной схемы, изображенной на фиг. 1, используются конструктивно-функциональные узлы, изображенные на фиг. 2.

Кружок на фигурах означает схему «ИЛИ-НЕ» с числом входов, равным числу стрелок, входящих в данный кружок.

Схема (см. фиг. 2) представляет собой один разряд комбинационного сумматора, содержащего входные величины, два полусумматора, схему переноса в следующий разряд и выходные вентили. Сумматор выполняет как арифметические, так и логические операции над двумя числами. Выходная информация может сниматься либо прямым, либо инверсным кодом.

Схема (см. фиг. 3) состоит из двух четверок разрядов регистра со сбросом.

Схема (см. фиг. 4) служит для увеличения числа вентильных входов в узел «Регистр» с помощью операции, рассмотренных на фиг. 6. Схема (см. фиг. 4) также может использоваться при «шинной» организации передачи информации между совокупностью регистров.

Схема (см. фиг. 5) представляет собой ускоренный перенос между четырьмя разрядами сумматора и служит для организации ускоренной работы параллельного сумматора. Сумматор разбивается на группы по четыре разряда. Внутри каждой группы действует схема ускоренного переноса. Группы, в свою очередь, объединяются по четыре и также охватываются ускоренным переносом, образуя блоки, между которыми тоже можно организовать ускоренный перенос и т.д. При этом используется один и тот же узел «Перенос сумматора».

На фиг. 6, а изображена схема «ИЛИ-НЕ» на два входа, а на фиг. 6,б - такая же схема, но только без нагрузки (последняя схема позволяет наращивать число входов в схему «ИЛИ-НЕ»); на фиг. 6,в - схема «ИЛИ-НЕ» на четыре входа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1517026A1 |

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Ячейка однородной структуры | 1990 |

|

SU1805461A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1986 |

|

SU1390608A1 |

Система узлов для устройств дискретного действия, отличающаяся тем, что, с целью сокращения внешней коммутации, обеспечения параллельного и независимого производства и контроля составных частей устройства, а также повышения эффективности эксплуатации готовых устройств, в ней внешние выводы узлов в строго фиксированном и одинаковом для каждого узла количестве имеют эквивалентное в пределах системы расположение, их последующее соединение определено непосредственно структурой устройства, а варьирование элементов, их относительное физическое расположение в узле и внутренняя коммутация узла обусловлены инвариантностью конструкции к схемам узлов, реализующим полный набор информационных функций.

Авторы

Даты

1968-12-16—Публикация

1967-01-31—Подача