В системах, исиользующи.х средства дискретной техники, например цифровые регистрирующие приборы и цифровые управляющие машины, аналоговая информация должна быть представлена в цифровой форме. Устройства, преобразующие аналоговые сигналы в цифровую форму, преобразователи типа аналог-код в таких система.ч часто имеют на входах многоканальные коммутаторы аналоговых сигналов. При переключении каналов во входном коммутаторе иа входе преобразователя возникает переходиой процесс из-за наличия реактивиостей в линиях связи от источника аналогового сигнала до коммутатора, а также из-за паразитиой и монтажной емкостей ка входе преобразователя. Характер этого переходного процесса в большинстве случаев монотонный, приближающийся к экспоненциальному. Обычно быстродейс1вую1дие преобразователи типа аналог-код выполняются на основе способа поразрядного кодирования. Одн-ако в многоканальном преобразователе, использующем способ поразрядного кодирования, преобразование можно начинать лишь после того, как закоичится переходный процесс на.входе преобразователя. В противном случае иогрешность преобразования может значительно превышать допустимую величину. Переходный процесс при этом считается законченным, когда разность между сигналом на входе иреобразователя и его установившемся значением становится и остается в дальнейшем меньше половины значения допустимой абсолютной погрешности преобразования. Таким образом, при использовании преобразователей, выполненных по способу поразрядного кодирования, ,зремя, необходимое для получения результирующего кода, складывается из времени переходного процесса на входе преобразователи при пеиеключенин каналов во входном ко.ммутаторе и вре.меин кодирования. Для того, чтобы получать результирующий код сразу же после окончаиия переходного процесса от нереключеиия каналов во входном коммутаторе, можно выполнять преобразование по способу считывания через фиксированный интервал времени после начала переключения каналов в ком1 утаторе или по способу, основанному на последовательном совмещении поразрядного кодирования со способом слежения, прпчем процесс слежения необходимо также заканчивать через фиксированный момент времени после начала переключения каналов во входно.м коммутаторе.

рядного кодирования, тоже треоует дополнительного сборудовання.

По предложенному способу преобразовапня можно получить результнрующий код в момент окончания переходного процесса на входе преобразователя, а также автоматически устранить возможные случайные сбои процесса поразрядного код розания. В этом способе преобразования аналогового сигнала в цифровой я разрядный код компенсирующий сигнал обратной связн, который вырабатывается с помощью преобразователя код-аналог, сначала формируют по способу поразрядного кодирования для Л старщих разрядов результирующего кода. Затем в зависимости от знака и величины разности между входным сигналом и компеиси ующим сигиалом, иолучивщимся в носледнем такте поразрядного кодирования, комненсирующий сигнал уменьщают на одну нлн несколько одинаковых ступеней, имеющих вес, эквивалентный единице (п - к-1)-го разряда. После этого компенсируюп пй сигнал увеличивают одпнаковыми ступенями, имеющими вес, эквивалентный единице /1-го (младшего) разряда результирующего кода. Процесс преобразования закапчивается, когда компенсирующий сигнал станет равным входному. Такой комбиинрованный способ преобразования целесообразно использовать, например, в преобразователях устройств связи с объектом управляющих вычислительных машип, для которых характерио наличие многоканальных коммутато)ов аналоговых сигналов.

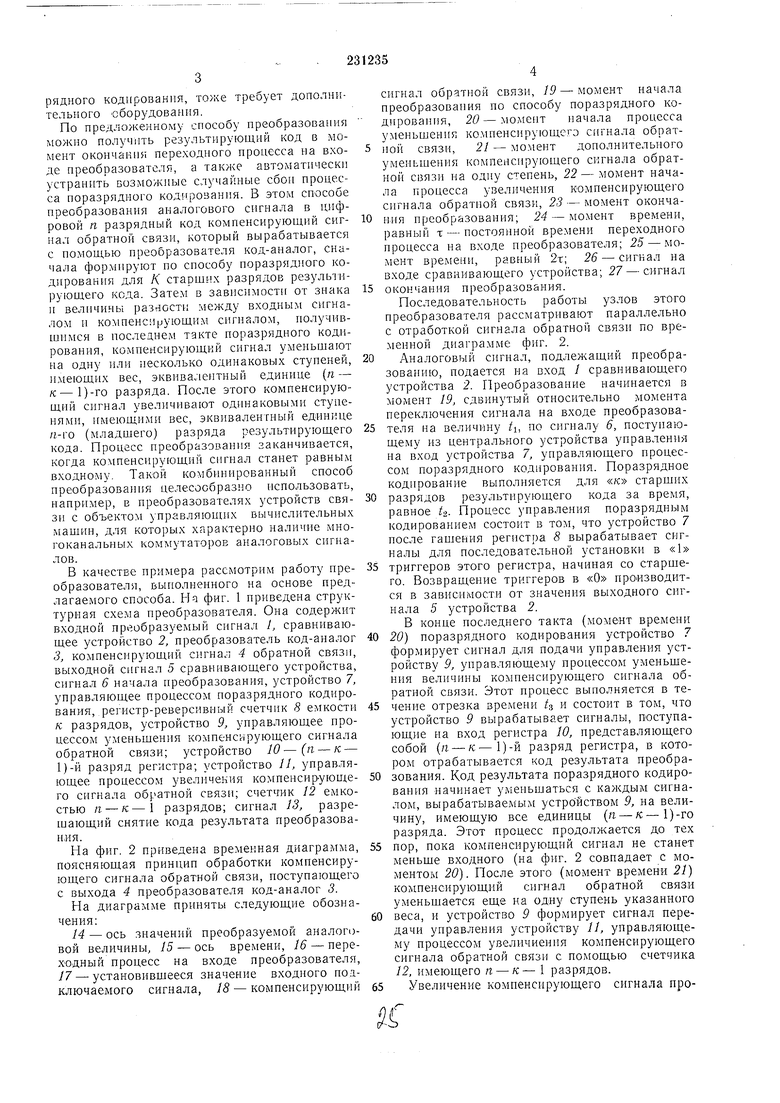

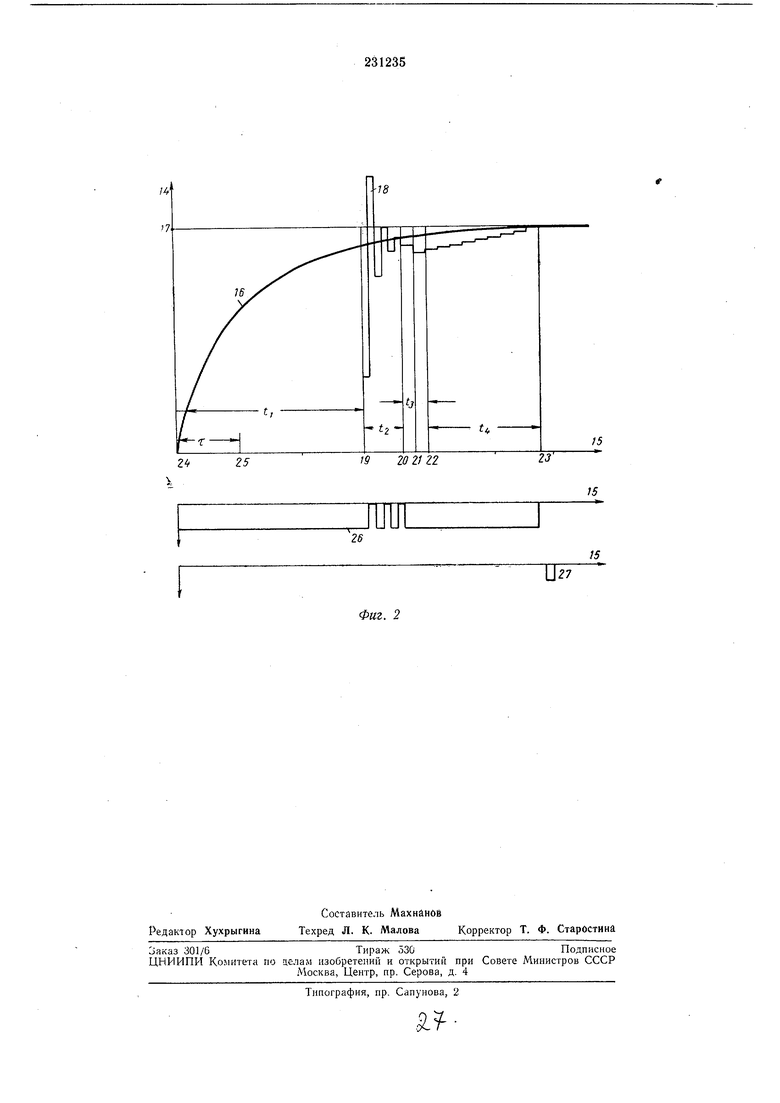

В качестве примера рассмотрим работу преобразователя, вынолнеиного на основе предлагаемого способа. НТ фиг. 1 приведена структурная схема преобразователя. Она содержит входной преобразуемый сигнал 1, сравнивающее устройство 2, преобразователь код-аналог 3, компенсирующий сигнал 4 обратной связи, выходной сигнал 5 сравнивающего устройства, сигнал 5 начала преобразования, устройство 7, управляющее процессом поразрядного кодирования, регистр-реверсивный счетчнк 8 емкости к разрядов, устройство 9, управляюи ее процессом уменьщения компенсирующего сигнала обратной связи; устройство 10-(п - к - 1)-й разряд регистра; устройство 11, управляющее процессом увеличения компенсир-ующего сигнала обратной связи; счетчик 12 емкостью п - к-1 разрядов; сигнал 13, разрещающий снятие кода результата преобразования.

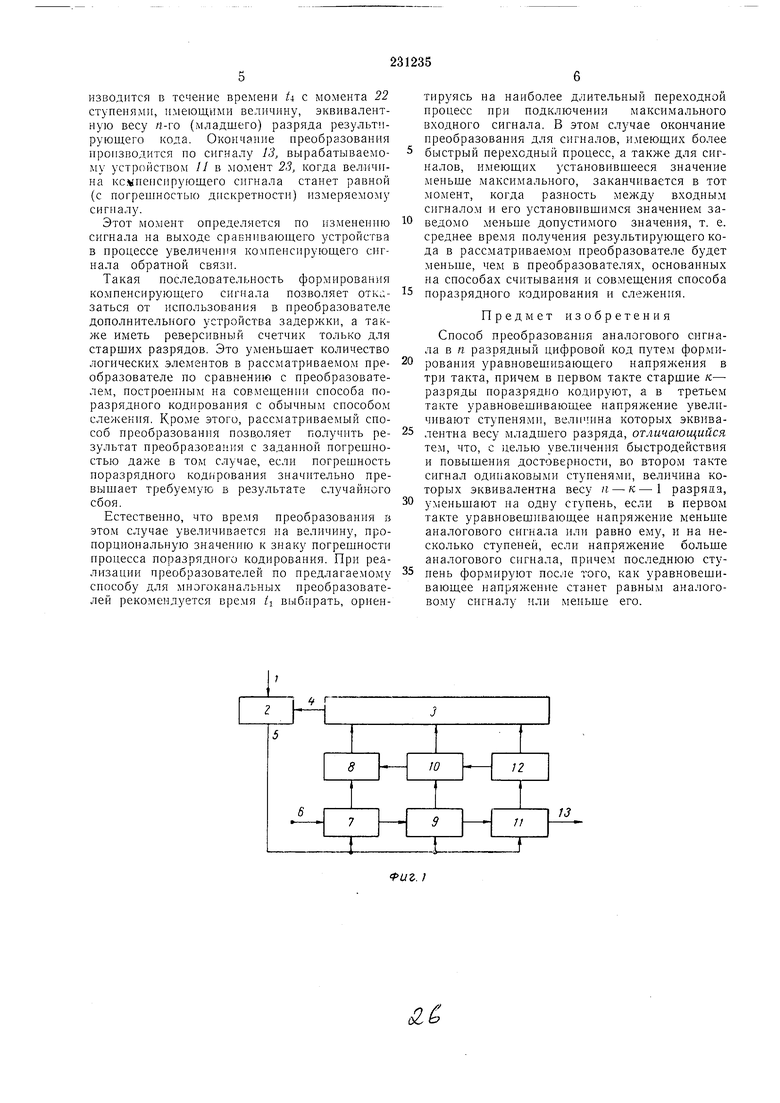

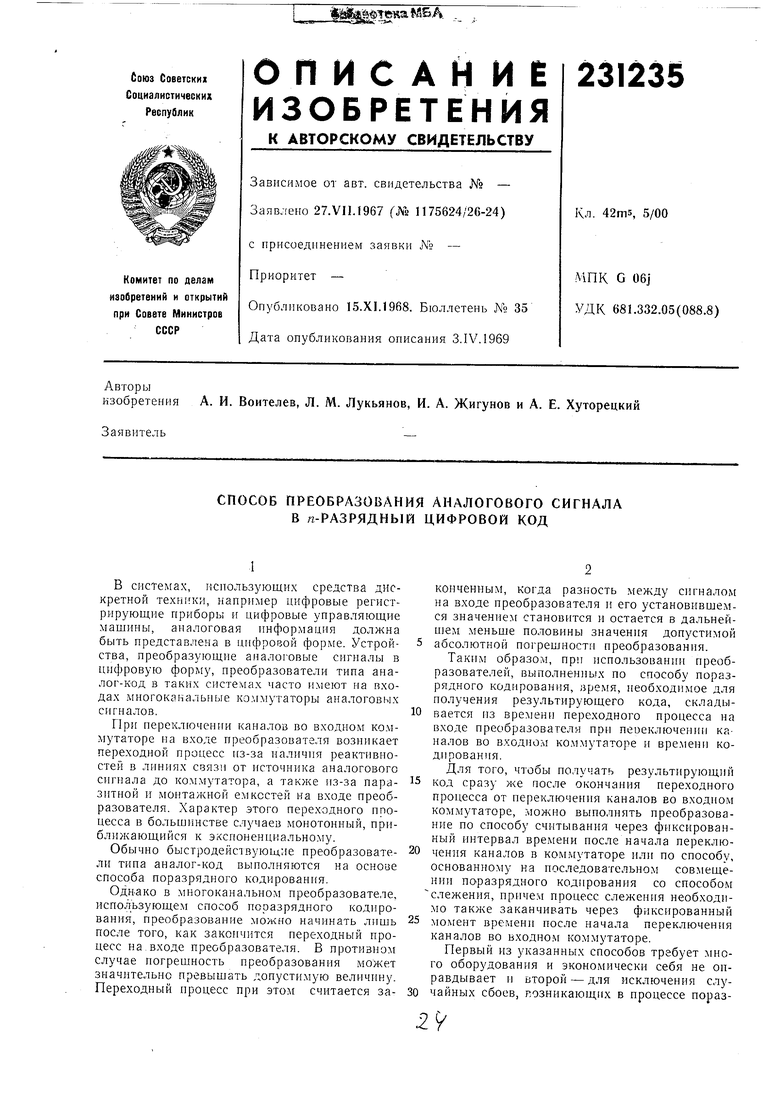

На фиг. 2 приведена временная диаграмма, поясняющая принцип обработки компенсирующего сигнала обратной связи, поступающего с выхода 4 преобразователя код-аналог 3.

На диаграмме приняты следующие обозначения:

14 - ось значений преобразуемой аналоговой величины, 15 - ось времени, 16 - переходный процесс на входе преобразователя, 17 - установившееся значение входного иоаключаемого сигнала, 18 - компенсирующий

сигнал обратной связи, 19 - момент иачала преобразовапия но способу поразрядного кодироваиия, 20 - момент иачала процесса умеиьщения колшеисирующсго сигнала обратпой связи, 21 - момент доиолнительного уменьщения компенсирующего сигнала обратной связи на одну степень, 22 - момент начала процесса увеличения Компенсирующе1-о сигиала обратпой связи, 23-момент окончаПИЯ преобразования; 24-момент времени, равный т - иостоянной времени переходного процесса иа входе преобразователя; 25-момент времени, равный 2т; 26 - сигнал на входе сравнивающего устройства; 27 - сигнал

окончания преобразования.

Последовательность работы узлов этото преобразователя рассматривают параллельно с отработкой сигнала обратной связи по времен иой диаграмме фиг. 2.

Аналоговый сигнал, подлежащий преобразоваиию, подается на сход / сравнивающего устройства 2. Преобразоваиие начинается в момент 19, сдвннутый относительно момента переключения сигнала на входе преобразователя иа величину /i, по сигиалу 6, поступающему из центрального устройства управления на вход устройства 7, управляющего процесCOJM поразрядного кодирования. Поразрядное кодпрованпе выполняется для «к старших

разрядов результирующего кода за время, равное 4- Процесс уиравления поразрядным кодированием состоит в том, что устройство 7 иосле гашения регистра 8 вырабатывает сигналы для последовательной установки в «1

триггеров этого регистра, начиная со старшего. Возвращение триггеров в «О производится в зависимости от значения выходного сигнала 5 устройства 2.

В конце последнего такта (момент времени

20) поразрядного кодирования устройство 7 формирует сигнал для подачи уиравления устройству 9, управляющему процессом уменьшеиия величины компенсирующего сигнала обратной связн. Этот процесс выполняется в течение отрезка времени /з и состоит в том, что устройство 9 вырабатывает сигналы, поступающие иа вход регистра 10, представляющего собой (п - к-1)-й разряд регистра, в котором отрабатывается код результата преобразованпя. Код результата поразрядного кодирования начинает уменьшаться с каждым сигналом, вырабатываемым устройством 9, на величину, имеющую все единицы (п - к-1)-го разряда. Этот процесс продолжается до тех

пор, пока компенсирующий сигнал не станет меиьще входного (на фиг. 2 совпадает с моментом 20). После этого (момент времени 21) компенсирующий сигнал обратной связи уменьщается еще на одну ступень указанного

веса, и устройство 9 формирует сигнал передачи управления устройству 11, управляющему процессом увеличиеиия компенсирующего сигиала обратной связи с помощью счетчика 12, имеющего п - к- 1 разрядов.

изводится в течение времени /4 с момента 22 ступенями, И-меющнми величину, эквивалентную весу /г-го (младшего) разряда результирующего кода. Окончание преобразования иропзводится по сигналу 13, вырабатываемому устройством /У в момент 2,, когда величина кс.иенспрующего сигнала станет равной (с погрешностью дискретности) измеряемому сигналу.

Этот момент определяется по изменению сигнала на выходе сравниваюшего устройства в процессе увеличения компенсируюш,его сигнала обратной связи.

Такая последовательность формирования компенсируюш,его сигнала позволяет отказаться от использования в преобразователе дополнительного устройства задержки, а также иметь реверсивиый счетчик только для старших разрядов. Это уменьшает количество логических элемеитов в рассматриваемом преобразователе ио сравнению с преобразователем, построенным на совмеш,ении сиособа поразрядного кодирования с обычным способом слежения. Кроме этого, рассматриваемый способ преобразования позволяет получить результат преобразования с за.а,анной погрешностью даже в том случае, если погрешность поразрядного кодирования значительно превышает требуемую в результате случайного сбоя.

Естественно, что вре.мя преобразования в этом случае увеличивается на величину, пропорциональную значению к знаку погрешности процесса иоразрядиого кодирования. При реализации преобразователей по предлагае.мому способу для многокаиальных преобразователей рекомендуется время /i выбирать, ориентируясь на наиболее длительный переходной процесс при подключении максимального входного сигнала. В этом случае окончание преобразования для сигналов, и.меющих более быстрый переходный процесс, а также для сигналов, ил еющих установившееся значение меиьше максимального, заканчивается в тот момент, когда разность между входным сигналом и его установившимся значением заведомо меньше допустимого значения, т. е. среднее время получения результируюш,его кода в рассматриваемом преобразователе будет меньше, чем в преобразователях, основанных на способах считывания и еовмеш,ения способа поразрядного кодирования и слежения.

Предмет изобретения

Способ преобразования аналогового сигнала в п разрядный цифровой код путем формирования уравновешивающего напряжения в три такта, причем в первом такте старшие к.- разряды поразрядно кодируют, а в третьем такте уравновешивающее напряжение увеличивают ступенями, величина которых эквивалентна весу младшего разряда, отличающийся тем, что, с ;елью увеличения быстродействия и повышения достоверности, во втором такте сигиал одинаковыми ступенями, величина которых эквивалентна весу п - разряда, уменьшают на одну ступень, если в первом такте уравновешивающее напряжение меньше аналогового сигнала нли равно ему, и на несколько ступеней, если напряжение больще аналогового сигнала, причем последнюю ступень формируют после того, как уравновешивающее напряжение станет равным аналоговому сигналу или меньше его.

2425

16 20 21 22

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| МНОГОКАНАЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬВСЕСОЮЗНАЯПй | 1972 |

|

SU330539A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1179533A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Аналого-цифровой преобразователь с коррекцией динамической погрешности | 1987 |

|

SU1607076A1 |

| Способ аналого-цифрового преобразования | 1986 |

|

SU1388985A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU428547A1 |

| Аналого-цифровой преобразователь с коррекцией динамических погрешностей | 1976 |

|

SU660240A1 |

| Способ аналого-цифрового преобразования | 1985 |

|

SU1304172A1 |

Фиг. 2

Авторы

Даты

1968-01-01—Публикация