Предложенное устройство относится к области цифровой вычислительной техники и может быть использовано в универсальных цифровых вычислительных машинах.

Известны устройства для умножения чисел одновременно на три разряда, содержащее сумматор со схемой сдвига на три разряда вправо, регистр множителя со схемой сдвига на три разряда вправо, регистры множимого и утроенного множимого, узел формирования управляющих сигналов, узлы выдачи в сумматор множимого и утроенного множимого в прямом и обратном кодах без сдвига, узлы выдачи в сумматор множимого и утроенного множимого в прямом коде со сдвигом на один разряд влево, узел выдачи множимого в прямом коде со сдвигом на два разряда влево.

Для увеличения быстродействия предлагается выходы регистра множимого и выходы узла формирования управляющих сигналов подсоединить ко входам узла выдачи в сумматор множимого в обратном коде со сдвигом влево на один и два разряда, выходы которых подсоединены ко входам сумматора, выходы регистра утроенного множимого и выходы узла формирования уиравляющих сигналов подсоединить ко входам узлов выдачи в сумматор утроенного множимого в прямом коде со сдвигом на два разряда влево и в обратном коде со сдвигом на один и на два разряда влево.

выходы которых подсоединены ко входам сумматора, а входы узла формирования унравляющих сигналов подсоединены к выходам ияти младших разрядов регистра множителя. Это позволяет уменьшить число сложений, а значит, и повысить быстродействие.

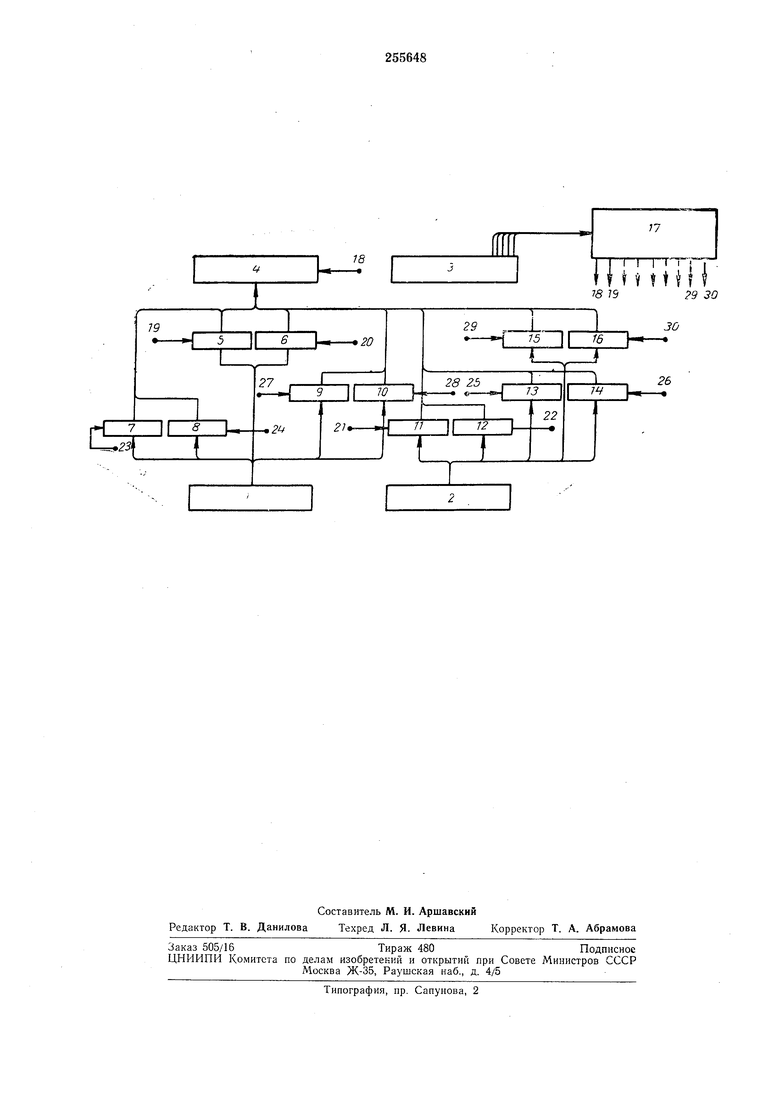

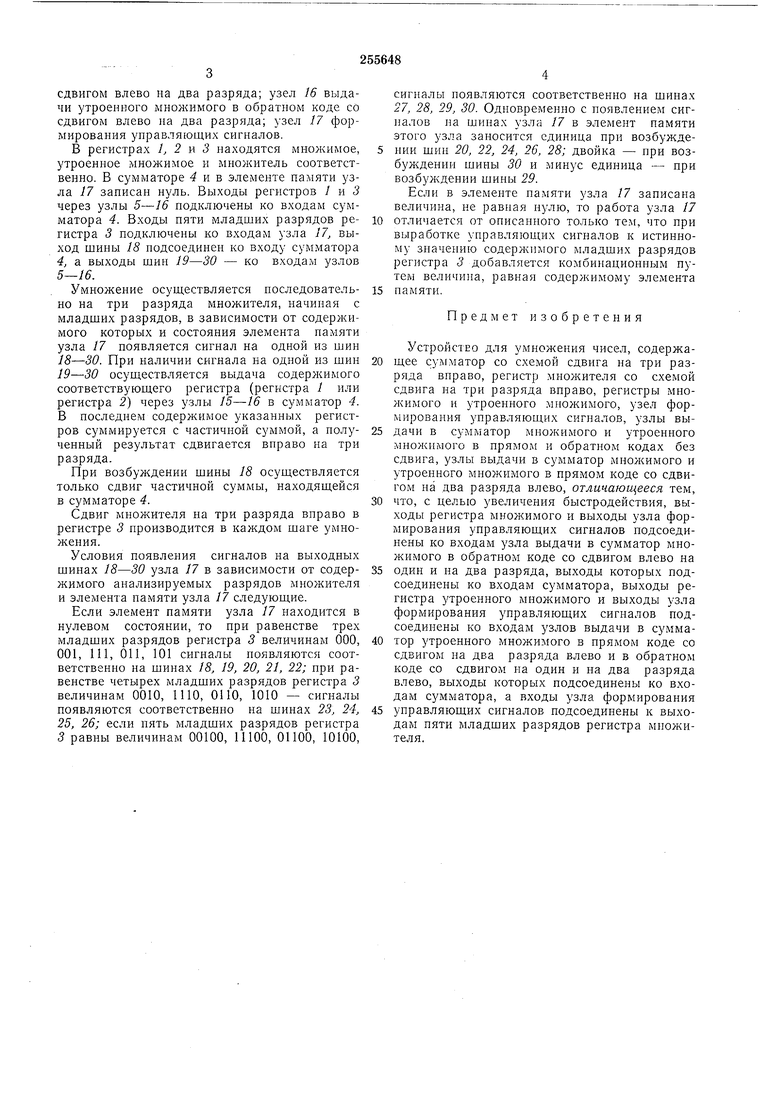

На чертеже приведена блок-схема предлагаемого устройства.

Блок-схема содержит регистр 7 множимого:

регистр 2 утроенного множимого; регистр 3 множителя со схемой сдвига на три разряда вправо; сумматор 4 со схемой сдвига на три разряда вправо; узел 5 выдачи множимого в нрямом коде без сдвига; узел 6 выдачи множимого в обратном коде без сдвига; узел 7 выдачи множимого в прялгом коде со сдвигом влево на один разряд; узел 8 выдачи множимого в обратном коде со сдвигом влево на один разряд; узел 9 выдачи мнол имого в прямом коде со сдвигом влево на два разряда; узел 10 выдачи множимого в обратном коде со сдвигом влево на два разряда; узел // выдачи утроенного множимого в прямом коде без сдвига; узел 12 выдачи утроенного множимого в обратном коде без сдвига; узел 13 выдачи утроенного множимого в прямом коде со сдвиго.м влево на один разряд; узел 14 выдачи утроенного множимого в обратном коде со сдвигом влево на один разряд; узел 15 выдасдвигом влево на два разряда; узел 16 выдачи утроенного множимого в обратном коде со сдвигом влево на два разряда; узел 17 формирования унравляющих сигналов.

В регистрах Д 2 и находятся множимое, утроенное множимое и множитель соответственно. В сумматоре 4 и в элементе памяти узла 17 записан нуль. Выходы регистров 1 и 3 через узлы 5-16 нодключены ко входам сумматора 4. Входы пяти младших разрядов регистра 3 подключеиы ко входам узла 17, выход шины 18 иодсоединен ко входу сумматора 4, а выходы шин 19-30 - ко входам узлов 5-16.

Умножение осуш,ествляется последовательно на три разряда множителя, начиная с младших разрядов, в зависимости от содержимого которых и состояния элемента памяти узла /7 появляется сигнал на одной из шин 18-30. При наличии сигнала на одной из шин 19-30 осушествляется выдача содержимого соответствуюшего регистра (регистра 1 или регистра 2) через узлы 15-16 в сумматор 4. В последнем содержимое указанных регистров суммируется с частичной суммой, а полученный результат сдвигается вправо на три разряда.

При возбуждении шины 18 осуществляется только сдвиг частичной суммы, находяш,ейся в сумматоре 4.

Сдвиг множителя на три разряда вправо в регистре 3 производится в каждом шаге умножения.

Условия появления сигналов на выходных шинах 18-30 узла 17 в зависимости от содержимого анализируемых разрядов множителя и элемента памяти узла 17 следуюш,ие.

Если элемент памяти узла 17 находится в нулевом состоянии, то при равенстве трех младших разрядов регистра 3 величинам 000, 001, 111, 011, 101 сигналы появляются соответственно на шинах 18, 19, 20, 21, 22; при равенстве четырех младших разрядов регистра 3 величинам 0010, 1110, ОНО, 1010 - сигналы появляются соответственно на шипах 23, 24, 25, 26; если пять младших разрядов регистра 3 равны величинам 00100, 11100, 01100, 10100,

сигналы появляются соответственно на шинах 27, 28, 29, 30. Одновременно с появлением сигналов на шинах узла 17 в элемент памяти этого узла заносится единица при возбуждеиии шин 20, 22, 24, 26, 28; двойка - нри возбуждении шины 30 и минус единица - при возбуждении шины 29.

Если в элементе намяти узла 17 записана величина, не равная нулю, то работа узла 17

отличается от описанного только тем, что при выработке унравляющих сигналов к истинному значению содержимого младших разрядов регистра 3 добавляется комбинационным путем величина, равная содержимому элемента

намяти.

Предмет изобретения

Устройство для умножения чисел, содержащее сумматор со схемой сдвига на три разряда вправо, регистр множителя со схемой сдвига на три разряда вправо, регистры множимого и утроенного множимого, узел формирования управляющих сигналов, узлы выдачи в сумматор множимого и утроенного множимого в прямом и обратном кодах без сдвига, узлы выдачи в сумматор множимого и утроенного множимого в прямом коде со сдвигом на два разряда влево, отличающееся тем,

что, с целью увеличения быстродействия, выходы регистра множимого и выходы узла формирования управляющих сигналов нодсоединены ко входам узла выдачи в сумматор множимого в обратном коде со сдвигом влево на

один и на два разряда, выходы которых нодсоедипены ко входам сумматора, выходы регистра утроенного множимого и выходы узла формирования управляющих сигналов подсоединены ко входам узлов выдачи в сумматор утроенного множимого в прямом коде со сдвигом на два разряда влево и в обратном коде со сдвигом на один и на два разряда влево, выходы которых подсоединены ко входам сумматора, а входы узла формирования

управляющих сигналов подсоединены к выходам пяти младших разрядов регистра множителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1977 |

|

SU675422A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1976 |

|

SU603989A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Устройство для выполнения операций умножения и деления | 1980 |

|

SU955038A1 |

| Устройство для умножения на п-разрядов множителя | 1977 |

|

SU717764A1 |

| Устройство для умножения | 1977 |

|

SU662940A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ И ДЕЛЕНИЯ | 1973 |

|

SU385273A1 |

| Устройство для умножения десятич-НыХ чиСЕл | 1979 |

|

SU817704A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

Даты

1969-01-01—Публикация