(34) УСЯРОЙСГГБО ДЛЯ УСКОРЕННОГО УМНОЖЕНИЯ ДВОИЧНЫХ

ЧИС:Е:Л, ПРЕДСТАВЛЕННЫХ в ОБРАТНОМ КОДЕ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| БКБЛЙОТЕК.Д | 1970 |

|

SU273520A1 |

| Устройство для умножения @ -разрядных чисел | 1984 |

|

SU1256018A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения чисел | 1979 |

|

SU817702A1 |

| Устройство для вычисления суммы произведений | 1973 |

|

SU717765A1 |

| Устройство для умножения | 1985 |

|

SU1290301A1 |

Изсоре екие LrrHooHTCH к вычисли-юггьной гехнйке и йоже-1- найти п|зикенение в арнф - MeTK etiKHJC устройствах Еьнггсяитепьяых ма-

11ШН,

Иавестны устройства для ускоренного yr-viпожения двончньж чжсея, содержащее сум -. матор модифншфованкых обратных кодов, регистры M:iojKmvjoro, множителя и результа- та бтюк Metrr-HOio узи /авлешгЯ; элементы И, неравнозьажосли, - фл-атер знака, шины ctuifSifiifB noicroi-oBKH Ji ;Гмножания, вькоды регисяра г. подключепы к. нер.:j ьк-л ExoHfiM сс -тветс-гаунощих эле-ментов iij Еьжоды KOjOr: fcD : по/ хлючены к пгрво гу :ax.oiij :у..Гьла-1/ора модифиш-фованных обратньЕ : кодов., ятар.М вход которого под-гсшочен к выходу регисм-ра зэыультата, вход ко- г-йрого сиедиЕЭн с выходом сумма-сора модифицарованньЕК oбpar ьiьs. коцоВ;, вьжодьт двух младOJHX и зкажово,г-о. разряда регистра множи -. геяя подключены ,: перзй«..::, второму и т ::етьбму вхоаам бяов:а гле.;,-Г г;и1-о управяе ,:Ш:Ц:. к -летвертому вход/ Eoiijp;}i-o лодклку-Аена шина . :yVuHCi.:i;u; K:.:.i, -оьаюиы блока местяоГЗ укравлаштя подключены ко вторы./5

входам первого и в гор-ого элементов И, вьь ходы: SKaiioBbrx разрядов регистров множи - f,.;or-o и множителя через sneNjeHT не авно - знЁг-шости и соответствующий элемент И, к дру1-«ому входу которого подключена шина сигнала подготовки, подключены к входу тркг-гера знака.

Однако такое устройство, производящее умножение чисел в обратных кодах с точно,-г,н

ю

.где и ра;: ядность мантиссы

onspai-n ОБ с фиксированной перед знаковым разрядом занятой), достаточно сложно, так как. и нем и.С1юяьззЮт сук матор разрядно - СУМ (2 и -fl).. Эго jBH3aHo с тем, что при псц-ученик очередного частного произведе :чий ВОЗМОЖНО изменение знака частного гфоиаведени-я и для формирования в этом слуЧае -иравильног-о результата необходимо перегкигнение из знакового прибав яя1-fc к младшему разряду остатка, учитывая ШЕ этом знак переполнения и остатка.

Цель Е-зрбретения - упрощение устройст- B.:i за счет уменьшения числа разрядов сумматора до (и +2).. 35 Для этого гфедпагаемое устроЁсг.-во со -- держит дополнительные элементы И, агеемен ты ИЛИ, элемент задержкн, шину свсгваяа коррекции, причем нупевсй выход триггера знака соединен с первыми входами первого и второго дополнительных элементов И а единичный выход - с первыми входами ips , четвертого и пятого дополнительных элементов И, шина сигнада коррекции под ключена к входам разрядов регистра множи мого и ко втсрым входам второго и qeaiiepтого дополнительных элементов И выходы которых подключены к первым входам элементов ИЛИа вторые входы КОТ( СО8ДИ нены с другими выходами блока меегного утфавпения, а выходы - со вторыми входами третьего и четвертого элементов И., шина сигнала умножения соединена со вторь ми входами первого и третьего эпе 4ентов И, выходы которых подключены к входам знаковых разрядов регистра результата шина сигнала подготовки соединена через элементы задержки со вторым входом пятого дополнительного элемента И,, выход которог подключен к входам разрядов регистра результата. На чертеже изображена блок- схема предлагаемого устройства умножения, Устройство содержит регистры многки лого 1 и множителя 2, триггер знака 3,, регистр результата 4, шину S сигнала подготовки, шины 6 и 7 сигналов знаковых разрядов множителя и множимого, элемен7 карав нозначности 8, элементы ИЭ,, 14, 16, 18, 19, 22, 23, 32 и 33, элемент 1О задержки, шину сигнала умножения 12, шину 13 нулевого плеча триггера 3, шину 15 единичного плеча триггера 3, местное устройство управления 17, элементы ИЛИ 20 и 21, шины 24 и 25 сигналов младших разрядов множителя вход 26 cyiviiviaTopa мо дифишфованных обратных кодов, суммат-ор 27 модифицированных обратных кодов, вы ход 28 сумматора модифи11ированнь х обратных кодов, шины 29 и 30 передачи значе НИИ сдвигаемых младших разрядов регистра 4 и старшие разряды регистра 2, шину 31 сигнала коррекхши. В исходном состоянии множимое и множитель записаны соответственно в регистры 1 и 2, ариггер знака 3 и регистр результа та 4 находятся в нулевом состоянитя, В подготовительном цикле операция умно жения возбуждается шина 5, Если при этом информация на шинах 6 и 7 будет разная, то на выходе элемента неравнозна шости 8 сформируется уровень, разрешакаиий прохож™ дение сигнала шины 5 через элемент И 9., 8 Г одго1озж1-аггьно « цчжкь aps t 5:pE:;:E iii.v;,.:;:OM а.Наже ПрОЯЗЗеДбЖЗЮ: rpiSTT Sp t 2Ю; Д ТгЦКг}; я едшюачксе ео& 1оявже, Svyf же о;21.й:ал Hocijie иролюзйдешан элемента а-адержш: ILO sftffiy - пает на эяемент И 1.1 и щш o:ipHi:fai« :-iHct.;: анаже щюкавелсения фнсваиваеГ всем paapt-да л регисгра 4 едвгн}й:ч:ные аначеьш,е, 3:й.Ж .чина задержки элемента Ю лонашкл бкгь больше времена: срабатъиани ©Kej:ifs:iv:a И Э и триггера 3, В далЕ.. s кахщог.; }а«же чуйЖ;еЬ; йижле умножений,, на yc-yipoSiuiao xic.iiusirrcs: СЛГНал шины 1 2,, ЛХ Л .О-КЭрОМ, а) Щ5И камвгшдк сл гнйяа на . , Kiio cooiBeTdsye-i- з,.;з к :йаг:(е,а&1но лу а)вй-л.:/ .а . ведэниЯа О1 а:р:ывае/ся eJifciueH-i И ,. А ;,:, ,;;;::.- -. рйД :&эреиоиие41 йн рег-я с; :ра 4 са в единиЩ се сос ой-якев в .| ро;::;;,енод« будет возбуждена л:шн;а лба ; и ;г ;:ен): ЧГо JipHBeu&r ж fijspexoji-iy р ааряда перепаиыеааи з н,ужй,б.:;з i-:-jCM-ij,.r-s.-; 6) tibicK мес. ,;/г)раБле й1::;1 j, / кьщает сшивам Кча aaejtiSHVru -i lS н .,, с, ,v3 п:е рез схемы ИЛИ 2С: :-. . . ксл ,; -Л. 22 и 23, СйО/1 ЯЯ; :|;;Jjp.,C4,:-:,:0-..0;E: дШ ::..СРООЗе анализа жнфор /:.::;;Да ;; i::a шяне 6 о i;:j;.: ;:iu -.гнс йитепя к cv-f,:b«bi ло Lv-;oc:jHKj 4 ..вух г-глад -ШИ5 : ра;зрядс:э 1.{:й.ожигекя 1шг:н:ы 2. . 261 с переносом т аканогичного а/юженкл :(;р8дь5д; ш ;е го шжла, 3 табл., 2 правее ено coeTos ние элементов и 1.8. 19,, 22, 23 и соот Бвтству}оадйя 8тим cociOB.Hiieiv; .1й.фо|Эма1а5;Я на Бхсде 26 cyyMMartipa 2V iSpK ур,,звожении чисел а ь.:..;«| ишфованньгх обк)атньзх кодах, С3формираси;.;:.::л;ая s реаульуаге этого cyivi- ма передаеа-ся с выхода 28 cyiv MaTopa .27 El регистр 4; гд с,цзйгается на два В1фаво. сж:и п нечетновз то с, в 1 оследнем шшяе гсро :аеоди;Сй на один ра&РЯЯ, Выпадающие за {трепать.; разрг;дио €:ет. ки регистр.а 4 разряды {астшэ/О чпойзваде--. RHS по uJHJiav 29 и 30 ,иэкУг на вход ет арших раэрйдов puSiiCkpa ..-е;/:55 2. с)тЕ разращь:; бьши освобождены ири 1;дВИлч ri/rnOMK-re,. на двс. рсэряда впрзвС r.iiytH рэз-ряд в последнем цгжле,, eos и яечшт ое). Быпсууыегшом одновре 1 енко с сум1йЯ::: - ани-ем в cyiviiviaTope. Поскеднитх нихдом jr.o oxeHJis: яЕгжется цккг; коррекции старшей чагтк прсиава сеыия. К оррекиия состоит .з .цо&БленуК .st стариией чаеги гк о й звепенкя кода обрбзовакнот1 «к-: вэрсией двоичншо здсяо { 7 ); ве.гяйГ й - на равна сумме no6aB,::fiBfiy;.i:;i. Е lipO Я8СС8 умножения к регистру laci -ьж лхроязведений четырех ь;;.жнн(Ц с .есоь.,&.ш козй филшентамй,, уч тьшаи1шимк: ..:. о.:,...:Г--. /:кмщ-5& 5224 ;;М::-нг GOBivi-ecTHo с обраоовазшюлиса частн№ « проявй.еаенжймй, J, Г S О i-i i l.,.,. fl йрк n нечетном i ,4,,6s..o j n iipH -n четном. ot.-j/тдествкения жчрреккии ка устфой-::Во пс«д--,.е7ся сигнал по шине 31,, запись iasxuB7i и per-MG-fp 1 жорректирунзщий код Ю 5

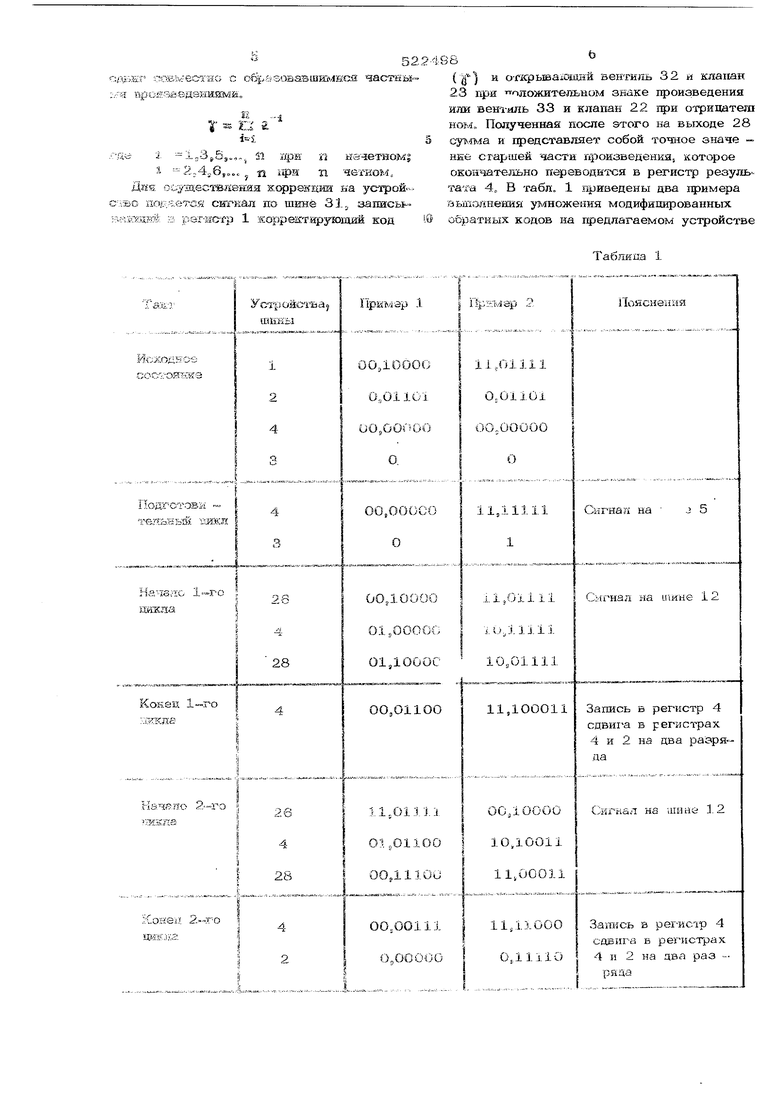

Таблица 1 8° (ц) и о-гкрьшахищш вентиль 32 и клапан 2.3 при положительном знаке произведения или вентиль 33 и клапан 22 при охрицатеш HOMc. Полученная после этого на выходе 28 cy.tMa и представляет собой точное аначе - вике старшей части произведенхш, которое окончательно переводвтся в регистр результата 4, В табл. 1 нриведены два примера вьшсмнения у11/1(ножения модифицированных обратных кодов на предлагаемом устройстве

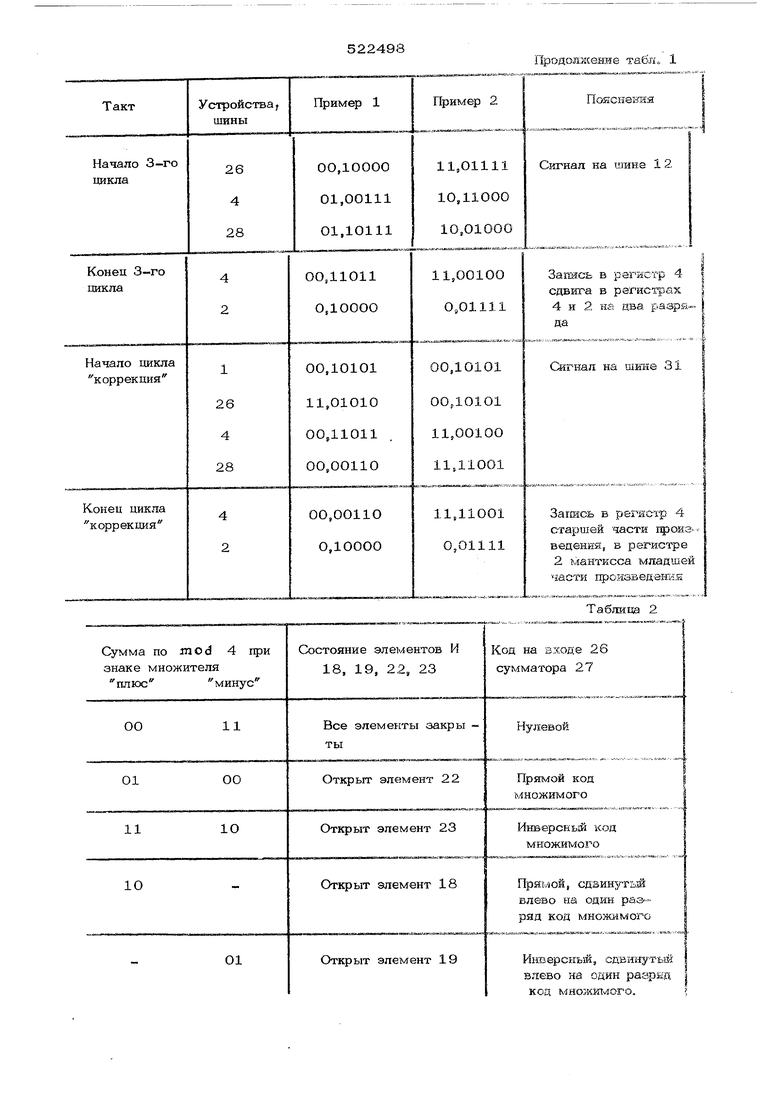

Состояние эле1./1ентов И 18, 19, 22, 23

ОО

11

Все элементы аакры ты

00

О1

Открыт элемент 22

11

10

Открыт элемент 23

10

Открыт элемент 18

01

Открыт элемент 19

Пояснеш я

Сигнал на шине 12

Закись в регистр 4 | сдвига в регистрах 4 и 2 на два paaps,да

Сигнал на шине 31

ЗагЕись в регистр 4 старшей части произ ведения, в регистре 2 мантисса младшей части npoKSBeaeffiiS

Таблица 2

Код на входе 26 сумматора 27

Нулевой

Прямой код множимого

Инверсный код множимого

Прямой, сдвинутьш влево на один раэряд код мно:«имого

Инверсный, сдвииут-ьж влево на один разряд

код MHOjKKTvIorO. Формула изобретения Устройство для ycKqpeHHoro умножения двоичных чисел, Едредставленных в обратном коде, содержащее сумматор модифицировавных обратных кодов, регистры множимого, множителя и результата, блок местного управления, элементы И, элемент неравнозначности, триггер знака, шины сигналов нодготовки и умно женан, причем выходы регистра множимого подключены к первым входам соответствующих элементов И, выходы которых подключены к первому входу сумматсра модифиаированных офатных кодов, второй вход которого подключен к выходу регистра результа та. вход котсрого соединен с вызсодом сумматора модифицированных обратных кодов, выходы двух мпадишх и знакового разрядов регистра множителя подключены к первому, svopouy и третьему входам блока местного угфавления, к четвертому входу которого подключена шина сигнала умножения, выходы блока местного управления подключены ко вторым входам первого и второго элементов И, выходы знаковых рагфядов регист роз множимого и множителя через элемент неравнозначности и соответствующий эле мент И, к другому входу которого подключена шина сигнала подготовки, подключены к входу триггера знака, отличающееся тем, что, с целью упрощения устройства, оно содержит дополнительные элементы И, элементы ИЛИ, элемент задержки, шину сигнала коррекции, лричем нуле - вой выход знака соединен с первыми входами первого и второго дополни - тельных элементов И, а единичный выход с первыми входами третьего, четвертого и пятого дополнительных элементов И, шина сигнала коррекции подключена к входам разрядов регистра множимого и ко вторым входам второго и четвертого дополнитель ных элементов И, выходы которых подключены к первым входам элементов ИЛИ, вторые входы которых соединены с другими выходами блока местного ухфавления, а выходы - со вторыми входами третьего и четвертого элементов И, шина сигнала умножения соединена со вторыми входами первого и третьего элементов И, выходы которых подключены к входам знаковых регистра результата, шина сигнала подготовки соединена через элементы задержки со вторым входом пятого дополнительного элемента И, выход которого подключен к входам разрядов регистра результата.

Авторы

Даты

1976-07-25—Публикация

1974-04-09—Подача