Изобретение относится к области вычислительной техники.

Известны устройства для обработки запросов в цифровой вычислительной системе, содержащие схемы приоритетов запросов, регистры, управляющие триггеры, логические схемы, щифратор, схемы сравнения, схемы управления.

В известных устройствах при занятости блоков памяти, соответствующих старшему по приоритету запросу от каналов и одному из запросов от центрального вычислителя, обращение к памяти задерживается на время, необходимое для освобождения одного из этих блоков памяти. Это обстоятельство нрепятствует обработке младщих но приоритету запросов, которые могут обращаться в свободные блоки основной памяти. Для повышения быстродействия работы устройства введены блок признаков нездовлетворенных запросов, схема приоритета выборки из блока признаков неудовлетворенных запросов, схема занятости блока признаков неудовлетворенных запросов и схема формирования повторного запроса, соединенная с первым входом схемы приоритета обобщенных запросов, второй и третий входы которой подключены к схеме приоритета запросов от каналов и схеме приоритета

запросов от центрального вычислителя соответственно, четвертый вход соединен с выходом схемы занятостп блока признаков неудовлетворенных запросов, а пятый вход через триггер блокировки обобщенных запросов подключен к ее первому выходу, второй выход схемы приоритета обобщенных запросов подсоединен к первому входу схемы вызова запросного слова от каналов, другие входы которой связаны со схемой приоритета запросов от каналов, схемой формирования повторного занроса, а ее выход соединен через щифратор номера запроса с первым входом первого регистра блока признаков неудовлетворенных

запросов, другие входы которого связаны с источником номера блока основной памяти в адресе и источником сигнала сопровождения запросного слова, выходы всех регистров блока признаков неудовлетворенных запросов

подключены к соответствующим входам схемы выборки из блока признаков неудовлетворенных запросов, схемам сравнения п схеме занятости блока признаков неудовлетворенных запросов, выход схемы выборки подключен к

входу схемы формирования повторного запроса, другие выходы каждой схемы сравнения подключены к щпне номера блока основной памяти, а их выходы соединены со входами схемы приоритета выборки из блока признаков неудовлетворенных запросов.

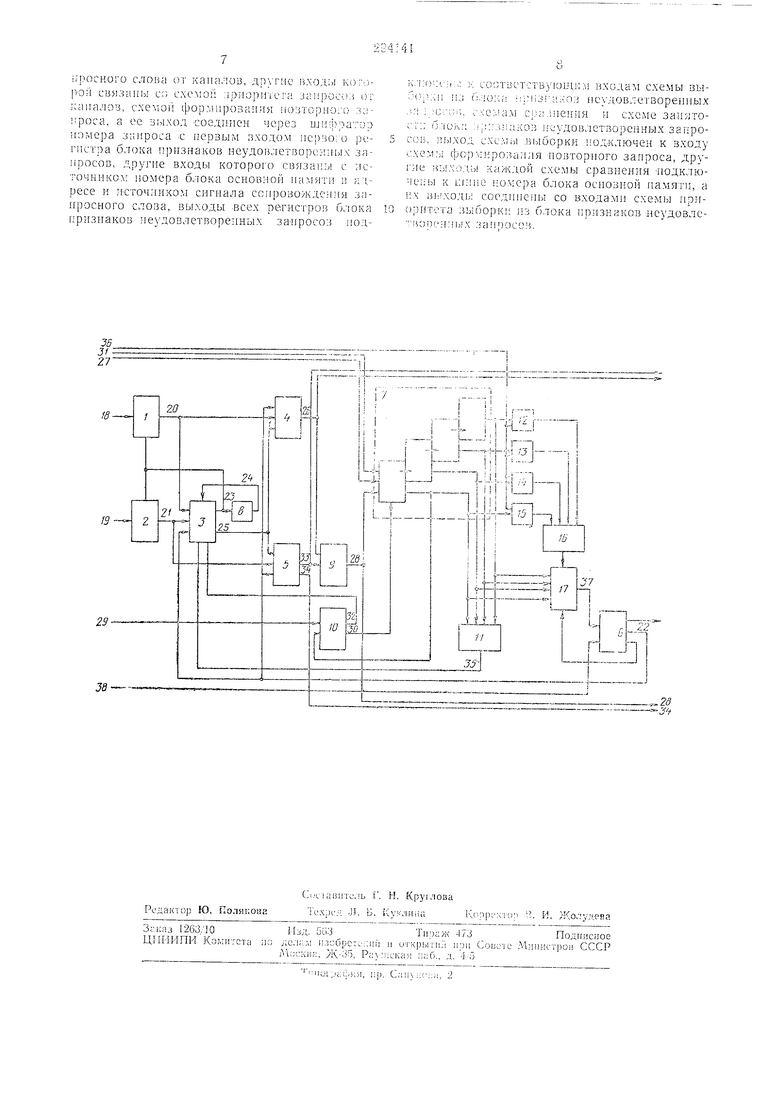

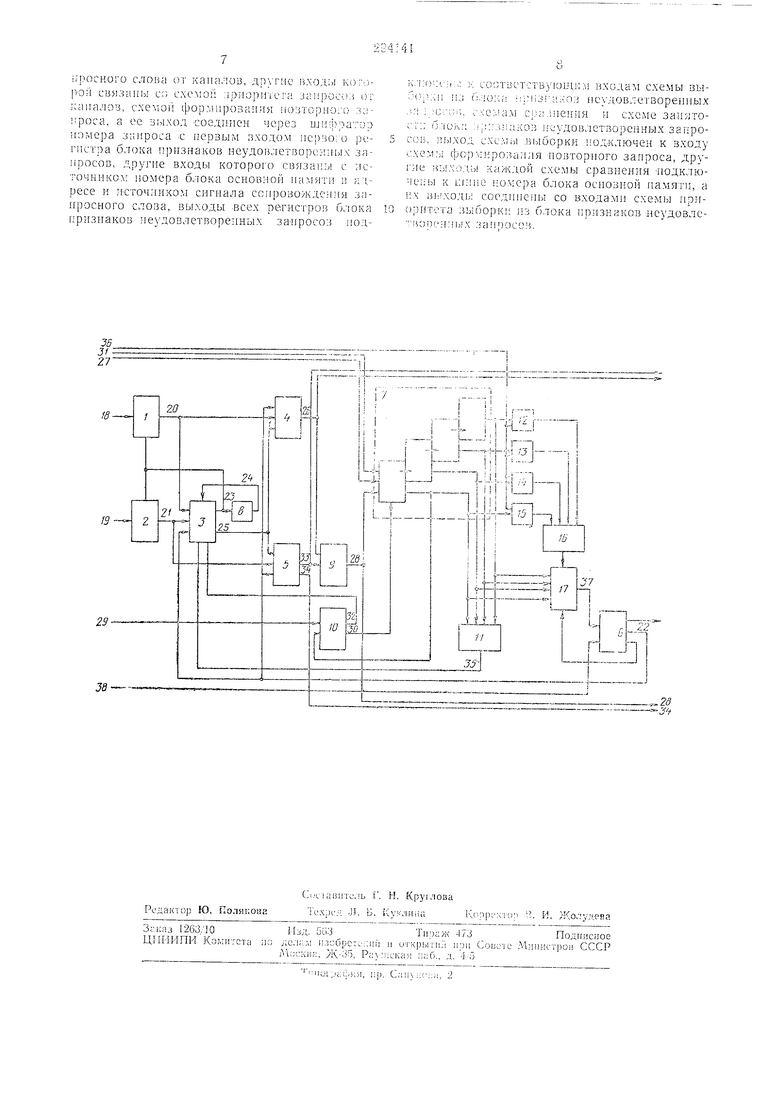

Па чертеже представлена блок-ехема устройства для обработки запросов в цифровой вычислительной системе.

Устройство для обработки заиросов содержит схему / приоритета запросов от каналов, схему 2 ириоритета запросов от центрального вычислнтеля, схему t приоритета обобщенных запросов, схему 4 вызова заиросного слова от капалов, схему 5 вызова заироспого слова от центрального вычислителя, схему 6 формировапия 1 овтори1з1х запросов, блок 7 иризиаков пеудовлствореииых запросов, триггер 8 блокировки обоби1ен1и)1х заиросов, шифратор 9 померг запроса, схему 10 управлеппя записью в блок, схему // запятостп блока, схемы 12- 15 сравнения, схему 16 приоритета выборки из блока, схему 17 выборки.

При обращеиии в основную память каналы ввода-вывода и центральный вычислитель посылают запросы в устройство обработки запросов. Ввиду того, что несколько запросов могут постуиать одновременно, необходимо обрабатывать нх в иорядке приоритета. Запросы от селекторных каналов (в состав вычислительной системы могут входить до шести таких каналов) и мультиплексного канала цринимаготся па схему / приоритета запросов от каналов по линии 18. Старший приоритет имеет запрос от первого селекторного канала. Приоритетность запросов от селекторных каналов уменьшается с увеличением номера канала. Низший приоритет имеют запросы от мультиплсксиого канала. Запросы от цеитральцого вычислителя цршшмаются на схему 2 приоритета заиросов от центрального вычислителя по линии 19. Центральный вычислитель может обращаться в основную память на запись и чтение слова состояния программы, на запись и чтение операнда и на чтение команды. Старший приоритет среди этих занросов имеет запрос на запись и чтение слова состояния программы. Далее по приоритету поставлены запросы: на запись операнда, чтение операида и чтение команды.

При наличии хотя бы одного запроса от каналов на выходе схемы / вырабатывается сигнал обобш.енного запроса, который по линии 20 передается на схему 5, Старший ио ириоритету запрос с выхода схемы 1 по линии 20 иередается на схему 4 вызова запросного елова каналов. Аналогично на выходе схемы 2 ириорнтета запросов от центрального вычислителя формируется сигнал обобщеи}юго запроса, который ио линии 21 иостуиает на схему 3 и на схему 5 вызова запросного слова от центрального вычислителя.

Кроме иеречнсленных сигиалов на схему 3 по линни 22 ноступает запрос со схемы 6, который является старшим из обобш,ен}1ых запросов. Это обусловлено тем, что в блоке 7 признаков неудовлетворенных запросов, связанном со схемой 6 хранятся признаки заиросов, которые поступили раньше, обрабатываемого запроса. Следовательно, для ускорения обработки неудовлетворенных запросов но мере освобождения соответствующих пм блоков ос ювпой памяти необходимо, чтобы запросы со схемы 6 имели высший приоритет. Это обстоятельство особегпо важио для обработки заиросов от каиалов. Поскольку приоритетность селекторных каналов условн;; (все шесть каналов идентичны по скорости работы), то в первую очередь по мере освобождеиия блоков пам}гги должны удовлетворяться те запросы, которые поступили по времени раньше. При паличпи хотя бы одного обобщенного запроса, на выходе схемы , формируется сигнал 2., котор1)1Й блокирует прием запросов на схему / схему 2. Этот же сигнал устанавли15ает в «1 триггер 8 блокировки обобщоппых заиросов. Выход триггера 8 блокирует прием обобщенных заиросов схемой 3 на липпи 24. Такпм образом повые запросы не будут приниматься на схемы приоритетов /, 2 и 3 до тех пор, пока полностью не обработается предыдущий заирос.

Если старшим по приорнтету в данный момент является запрос от канала, то на выходе схемЕ 1 3 (на лпнии 25 вырабатывается сигнал, который постуиает на схему 4 вызова запросного слова капалов. Этот сигнал совместно с сигналом по линии 20 от схемы / образует заирос цо линии 26 с выхода схемы 4 вызова запросного слова капалов. При наличии сигпала на липии 26 соответствующий капал выставляет свое запросное слово па входпые шииы устройства управлеппя осповной памятью. В запросное слово входят; адрес, информапня, маркеры, ключ защпты п признак режима памяти ( запись или чтепие). Запросное слово принимается па соответствуюпдие триггеры и регистры устройства анализа запроспых слов и коммутации щип осповпой иа.мяти.

Пз принятого адреса с учетом коэффгищепта расслоения основной в устройстве анализа занросных слов и коммутации шин основной иамяти выделяется код номера блока. Этот код 110 лпшш 27 поступает па первый регпстр блока 7 признаков иеудов,:1етворенпь Х запросов. Сигнал 26 с выхода схемы 4, соответствующий старгнему ио приоритету запросу от каиалов, преобразуется па шифраторе 9 номера запроса в двоичный код. Код номера запроса с выхода шифратора 9 поступает но линии 28 и а вход первого регистра блока 7 и в устройство ком.мутац Ц- считанных из основной иамяти данных.

Г1слп блок основной иамяти, соответствуюпи1Й принято.му адресу, запят, то устройство анализа запроспых слов и коммутации шии памяти посылает унравляюпдий сигиал иа вход схемы 10 управления заиисью в блок признаков неудовлетворенных запросов по липи 29. Па выходе этой схемы формируется сигиал 30, который разрешает загщсь признаков запроса (код номера запроса, код номера блока основной памяти и признак занятости) в первый регистр блока 7 признаков неудовлетворенных запросов. ripi 3iiaK запятостп поступает по линии 31 из устройства анализа запроспых слов и коммутации шин основной памяти. Одновременно с разрешением заииси на выходе схемы 10 формируется сигнал 32, который нроизводит сброс схемы 3 нрноритета обобшенных запросов. При этом иа выходе схемы 3 снимается сигнал 23 блокировки схемы 1 приоритета запросов от каналов и схемы 2 приоритета запросов от центрального вычислителя. Кроме того, сигнал 23 сбрасывает триггер 8 блокировки обобщенных запросов. При этом снимается сигнал блокировки на линии 24 схемы 3 приоритета обобщенных запросов. Таким образом, устройство подготовлено к приему и анализу следующих но нриоритету запросов. Запросы от центрального вычислителя обрабатываются аналогично запросам от каналов, за исключением того, что схема 5 формирует признак записи и чтения. Сигналы вызова запросного слова по линии 33 и признака записи или чтения по линии 34 поступают в устройство анализа запросных слов и коммутации шин основной памяти. 14аличие блока 7 дает возможность обрабатывать следующие но приоритету запросы от каналов центрального вычислителя и запускать соответствующие им блоки памяти при условии, что эти блоки свободны. Это увеличивает пропускную способность блока управления основной памятью, поскольку за время, необходимое для освобождения соответствующего старшему запросу блока памяти, успевают обработаться несколько следующих за ним запросов. Признаки, записанные в первый регистр блока 7, передаются во второй регистр, затем в третий и так далее при условии, что регистр со старщим номером не занят. Таким образом, запросы, записанные в блоке, выстраиваются в нем в порядке их поступления. При заполнении блока 7 схема // формирует сигнал 35, который блокирует прием запросов от каналов и центрального вычислителя на схему 5 приоритета обобщенных запросов. Поэтому, иока не освободнтся хотя бы один регистр блока 7, схема // занятости блока разрешает прием и обработку только повторных запросов со схемы 6. Коды номеров блоков основной памяти, записанные в каждом занятом регистре блока, сравниваются на соответствующих схемах сравнения 12-15 с кодом номера того блока памяти, который должен освободр1ться в первую очередь. Этото код поступает на схемы сравнения 12-15 по линии 36 из устройства

коммутации считанных из основной памяти данных.

Если код номера освобождающегося блока памяти совпадает с кодами, записаннымн в регистрах блока, то на выходах схем сравнения (на которых зафиксировано совпадение) формируются сигналы на схему 16. При наличии овпадения этих кодов установлен следующий приоритет выборки из блока 7 иризиаков неудовлетворенных - просов.

входы которой подключены к схеме нриоритета заиросов от каналов и схеме прпоритета запросов от центрального вычнслителя соответственно, четвертый вход соедпнен с выходом схемы занятости блока признаков неудовлетворенных запросов, а пятый вход через триггер блокировки обобщениых зап.росов подключен к ее первому выходу, второй выход схемы приоритета обобщенных запросов подсоединен к нервому входу схемы вызова за1.Если в какольлпбо pcritcrpe блока записаны признаки неудовлетворенного запроса от канала, а в другом (или других) признаки неудовлетворенных запросов от центрального вычислителя, то в первую очередь выбираются признаки запроса от канала независимо от того, в каком регистре блока они записаны. 2.Если в нескольких perncTjiax блока 7 записаны признаки неудовлетворенных запросов только от каналов или только от центрального вычислителя, то в нервую очередь выбираются нризнаки из того регистра, который имеет большой иомер. Это связано с тем, что в регистре с большим иомером записаны признаки неудовлетворенного запроса, поступившего раньше других. Общее правило выборки из блока признаков неудовлетворенных запросов: в первую очередь выбираются признакн запросов от каналов; если таких признаков несколько, то в первую очередь, выбираются признаки из регистра с больщим номером. Считывание признаков из блока 7 осуществляет схема 17 выборки. Считанные нрнзиаки по линии 57 поступают на схему 6 формирования новторных запросов. На этой схеме производится расщифровка кода номера запроса. При наличии сигнала «Конец цикла но линии 58 от освобол дающегося блока основной намяти на выходе схемы 6 формирования новторных запросов образуется сигнал на линии 22. Этот сигнал передается на схему 5 нриоритета обобщенных запросов. Если сигнал по лииии 22 является иовторным занросом от канала, то он передается на схему 4 вызова запросного слова от канала, если от центрального вычислителя - на схему 5 запросного слова от центрального вычислителя. Предмет изобретения Устройство для обработки запросов в цифровой вычислительной системе, содерм ащее регистры, унравляющне триггеры, логические схемы, схемы прноритетов запросов, шифратор, схемы сравнения, схемы управления, отличающееся тем, что, с целью повыщения быстродействия системы, в него введены блок признаков неудовлетворенных запросов, схема приоритета выборки из блока призиаков неудовлетворенных запросов, схема занятости блока нризкаков неудовлетворенных запросов и схема формирования повторного запроса, соединенная с первым входом схемы приоритета обобщенных запросов, второй и третий

irpocHoro слова от каналов, дпхтме когорой связашз с:) схелюй )1пега jaiipocc i i)r , схемой формпрозапля нозторного яаifpoca, а ее змход Соединен через 1инф;а:оэ иоме)а згдфоса с первым входом нерзого )егнстра блока трпзнаков неудовлетворенных заlipocos, другие входы которого связан.л с нс точником номера блока основной намятн в ачреее н ИСточннком сигнала сонрово кде;.ня за,нросного слова, выходы зсех регнстров блока прнзнаков неудовлетворенных заиросоз нодj г:ло:-;г ::;;пз:д|хоз неудовлетворвнных ;. cxe;,iaM с ;:аз1 ення и занято;; : ;:;::;маков ;еудовлетворенных запроод схем;, выборки подключен к входу орл: -;ро;;ання ногзторного занроеа, дру;;.ы каждой схемы сравнення подклюднне iiOMepa блока основ1юй памяти, а д,ь: соедн11е1Нл со входами схемы нрнз яборки }л б.тока прнзнагсов неудовле)ix занросов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛАТЕНТНО-УЕХиЛ-ГКАЯ,БИБЛИОТЕКА | 1970 |

|

SU283685A1 |

| УСТРОЙСТВО КОММУТАЦИИ | 1971 |

|

SU294139A1 |

| Устройство для сопряжения каналов ввода-вывода с устройством управления оперативной памятью | 1984 |

|

SU1265788A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСГСО | 1970 |

|

SU287123A1 |

| Устройство для сопряжения каналов ввода-вывода | 1975 |

|

SU559234A1 |

| Устройство для сопряжения каналовВВОдА-ВыВОдА C уСТРОйСТВОМ упРАВлЕНияОпЕРАТиВНОй пАМяТью МНОгОпРОцЕССОР-НОй ВычиСлиТЕльНОй МАшиНы | 1979 |

|

SU822168A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

Авторы

Даты

1971-01-01—Публикация