Изобретение относится к области вычислительной техники и может найти применение при конструировании высокопроизводительных цифровых интегрируюпдих машин (ЦИМ).

Известны устройства для умножения, состоящие из сумматоров, регистров, линий задержки и логических элементов, используемые для умножения кода подынтегральной функции у на различном образом представленные коды приращения Ах независимой неременной.

Предлагаемое устройство отличается таким соединением составляющих его элементов, которое нозволяет производить умножение кода подынтегральной функции на код комбинированного приращения независимой неременной, принимающей свои значения из набора

А;с {О, 1, 2, ... , 2- - 1, , . . . , , где РЬ Pz,---, Рт - целые,

, а п - число разрядов в коде подынтегральной функции. Это приводит к положительному эффекту, заключающемуся в значительном улучшении динамических и надежностных характеристик ЦИМ в целом.

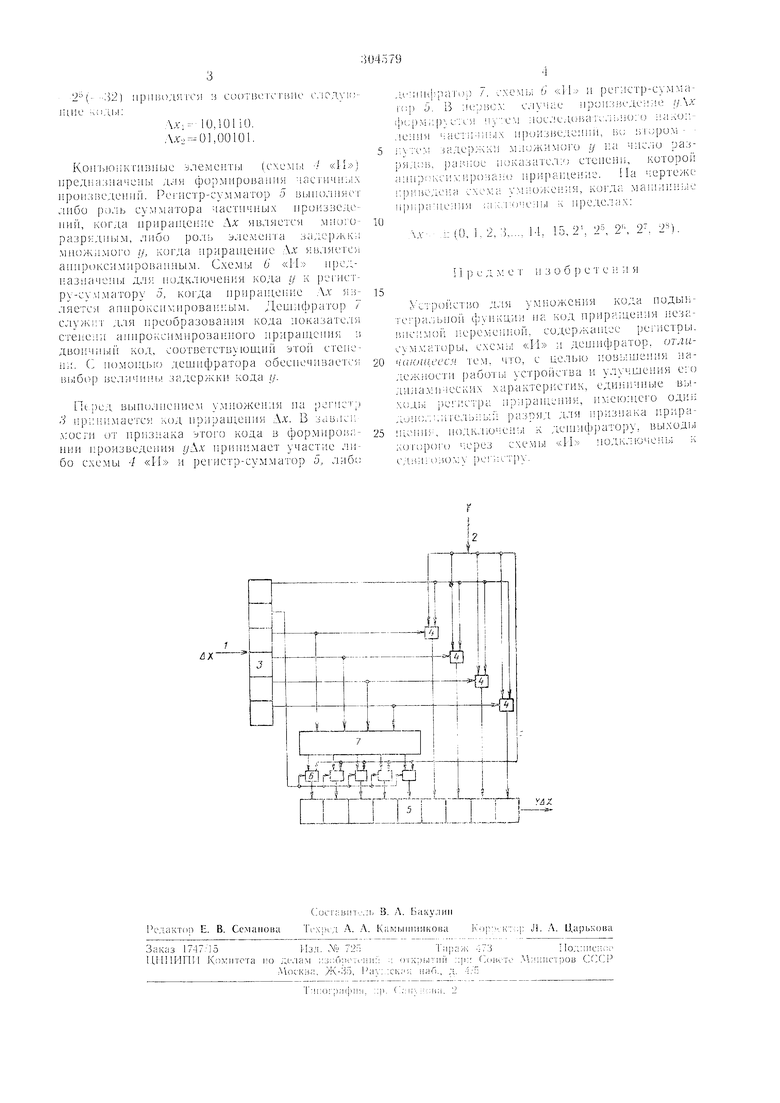

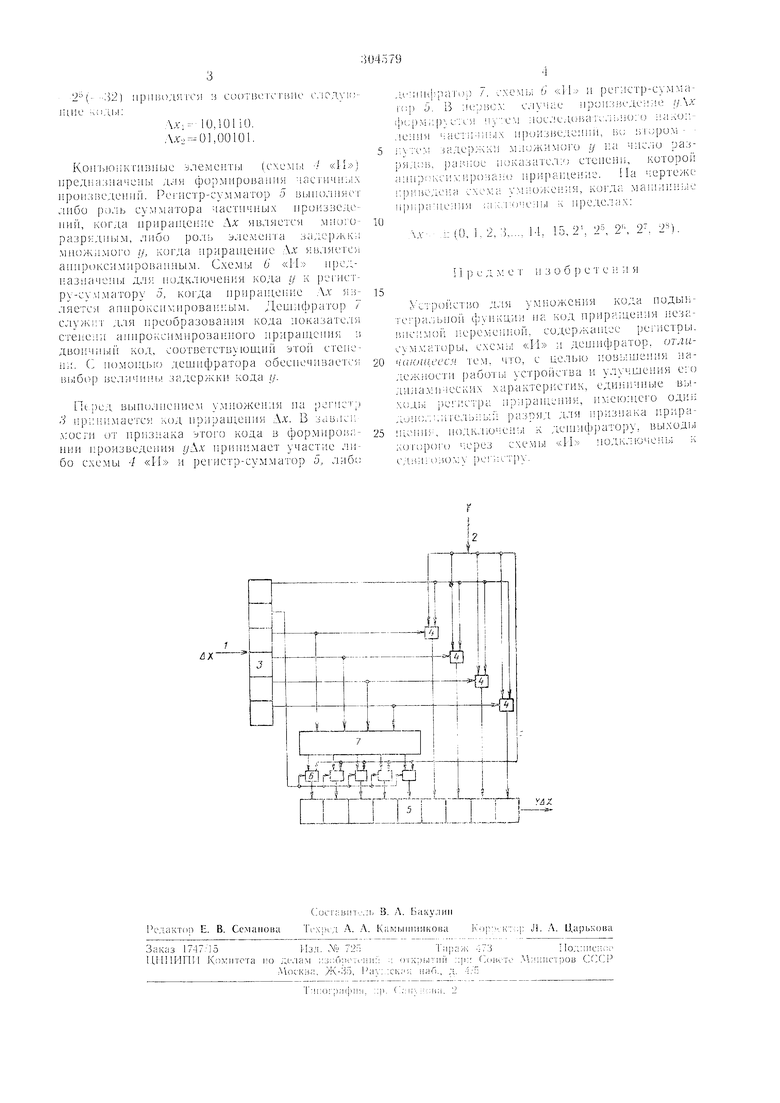

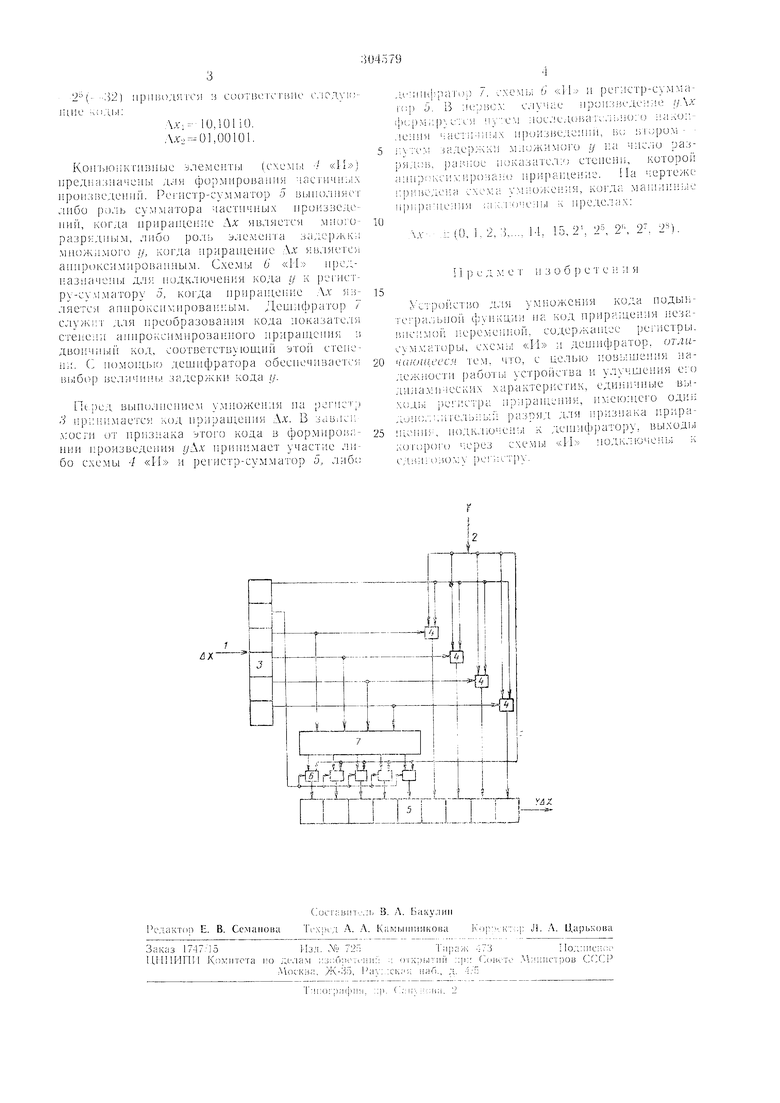

Оно содержит кодовые щипы /, кодовую щину 2, регистр 3 приращения, схе.л1ы 4 «И, регистр-сумматор 5, схе.мы 6 «П и дешифратор 7.

Кодовые щпны 7 служат дл5т приема параллельным кодом прпращенпя .л . По кодовой шипе 2 последовательным кодом па схему умножения поступает значение подынтегральной

функции у. Регистр 3 служит для приема п временного хранетщя кода приращения A.v. У.меньщение количества разрядов регистра 3 достигается за счет специального метода кодирования аппроксимированных нрпращений.

CyniecTBo этого метода состоит в том, что аипроксимироваипые приращеиня представляются кодом показателя стеиотп двойки. Например, нриращеппе Д..2 представляется кодом 00, liO. в котором первый разряд перед запятой является знаковым. Поскольку код. представляющий многоразрядное приращение, может совпадать с кодом, представляющим ампроксимпрованиое прираИ1ение, предлагаетея эти коды сопровождать

специальными признаками, для чего требуется один дополнительный разряд. В данном примере таки.м разрядом является старший. При таком методе кодирования многоразрядному приращеник) A.vi + 101 0(-|-22) п ап,V:.- 10,10110. ;U.-01,00101. ир(Л1;5Всдени11. 1чгиетр-суммагор о 151) г либо )оль сумматора частичных иро(з: сдгнип, когда ирира1де1 ие х яв.дяетгя мисяо- ю разр/;д1п 1м, либо роль элемента задер/ккл миожимого //, когда ирирашеиие Лл: И1ктя1гся аиироксимироваииым. Схемы 6 «11: и)едиазиачеиы для иодключения кода // к )егиструч:умматору 5, когда ирираи еиие .Лл: я:-;- 15 ляется аицроксилдфованиым. Дешифратор 7 елу/к;;т для иреобразоваиия кода доказателн Сгеиел; аиироксимирозанпого ирира1И,е|1ия и двоичи1 п код, соогвет-ствующи iToii етеисии. С дешифратора обесиечиваетея 20 )) 1)е,тичии| з; держки хОда //. Пк)ид вьитилиеиием умножения иа регистр i принимается АОД нрираи;е11ия Лл;, 13 завлси л;ос1Ч1 от прнзнака TOix) кода в формиро ;;:- 25 нни нроизведения уДл принимает участие либо схемв 4 «И и регистр-сумматор 5, либ;.; .11-:111|фратор 7. oxcMiii о «ll. и регистр-с ммаi(;p 5. l :к;:;1и;л; vMViac ii)oii3jK;u;::;ie //A;c )л,;р L; i.s ;1осл1;ди иИ .); о :ia;4(j;i лсини часГ Миыл приизисл иии, В;; ;и;;)омj: :(. ia;iep KK:i мл и/к им о го у на число разрял.;:и, paiMioe клчазагсл:) степени, IiUTOpoii тегра.;ьио (рушщди на код ирираи|е; ия ije3a ;иеимс)1 иеремеииой, содер/кащее ре1иетрв1. е м.:атч)ры, схе.мь «И и деиикрратор. отли4(i(JtUiccf тем. что, е повышении иаде/киоети работи устройетва и улучшения е; о динамических характериетнк, единичные выходь регистра ирираихииия, нмек)И1его дии(;,-ллиел1):;ы;1 разряд для признака ириранкчпИ, иодлдючены к ден1ифратору. вв1ход1)1 кокцзо е.чзи ре истр

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАТОР ДЛЯ ПАРАЛЛЕЛЬНОЙ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ МАШИНЫ С ЭЛЕКТРОННОЙ КОММУТАЦИЕЙ | 1973 |

|

SU388278A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1971 |

|

SU302002A1 |

| Цифровой интегратор | 1977 |

|

SU732920A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

ЛХ

Ш гр гЙгС-Ш i

- I I

JIEtlll..

} YA

Даты

1971-01-01—Публикация