Изобретение относится к области вычислительной техники.

Известны селекторные каналы, в состав которых входят блок управления, схема соответствия, регистр флажков и ряд других регистров. Однако пропускная способность этих каналов и всей системы в целом из-за использования микропрограммного управления в режиме передачи данных низка. Кроме того, обращение к оперативной памяти требует обслуживания со стороны центрального обрабатывающего устройства.

Целью изобретения является повышение скорости передачи данных и обеспечение возможности автономного обращения к оперативной памяти.

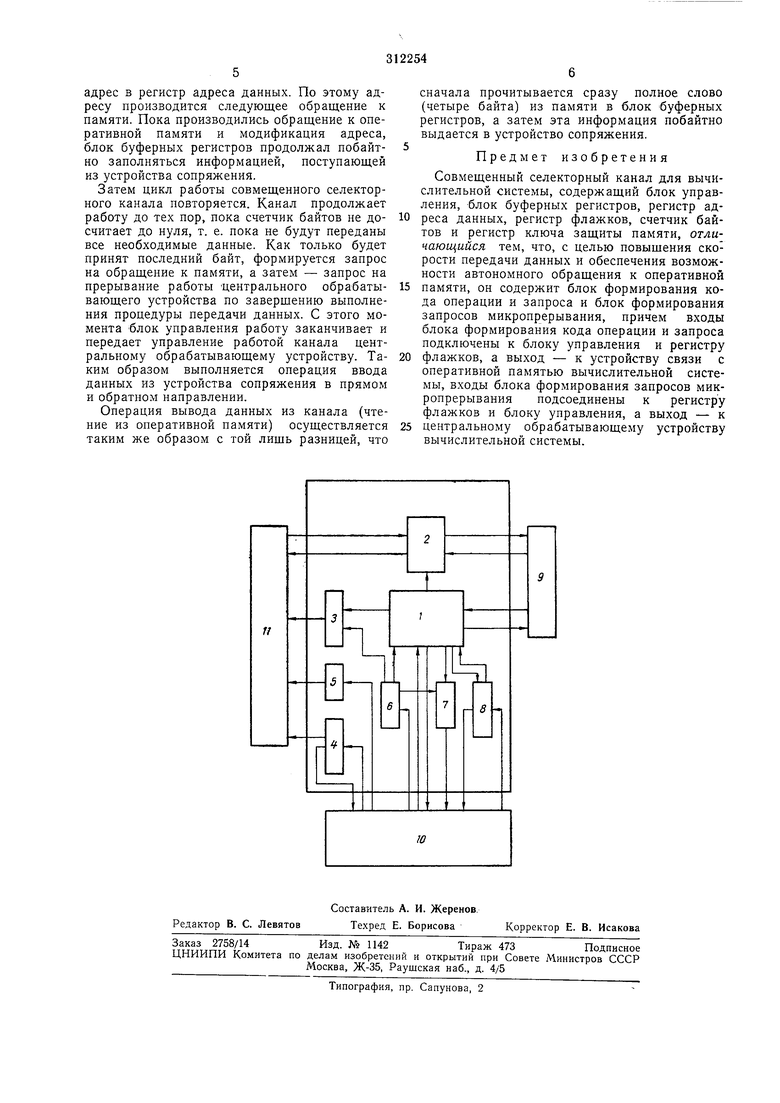

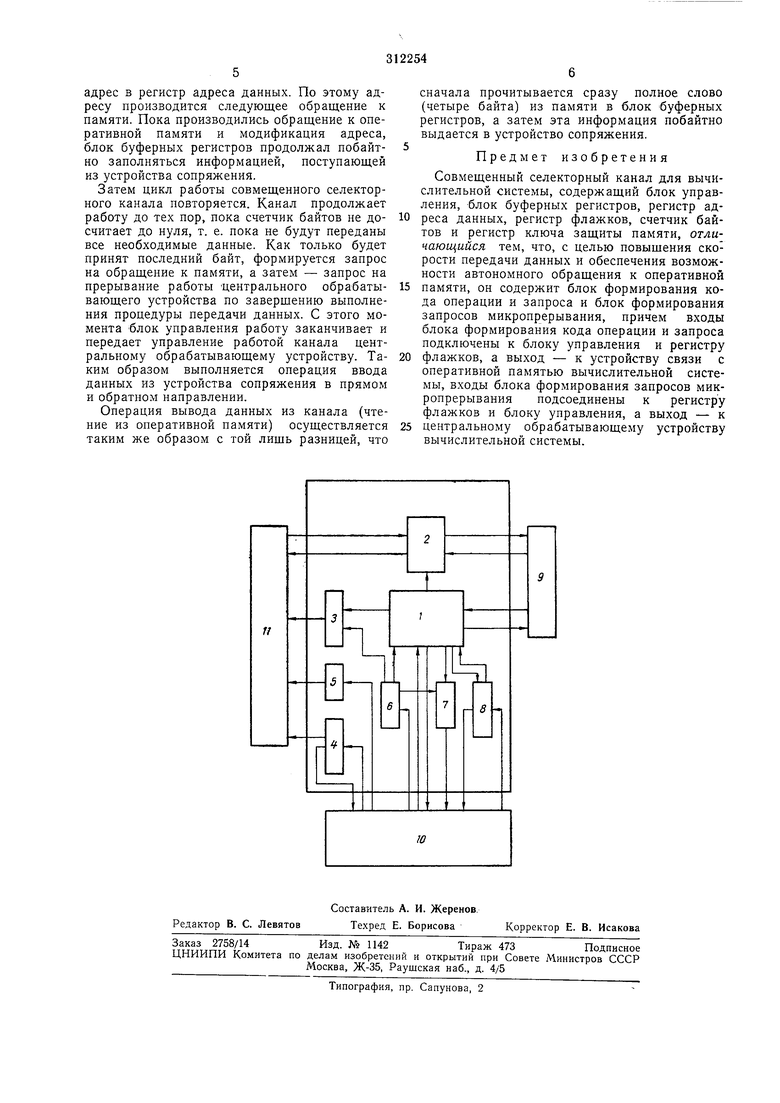

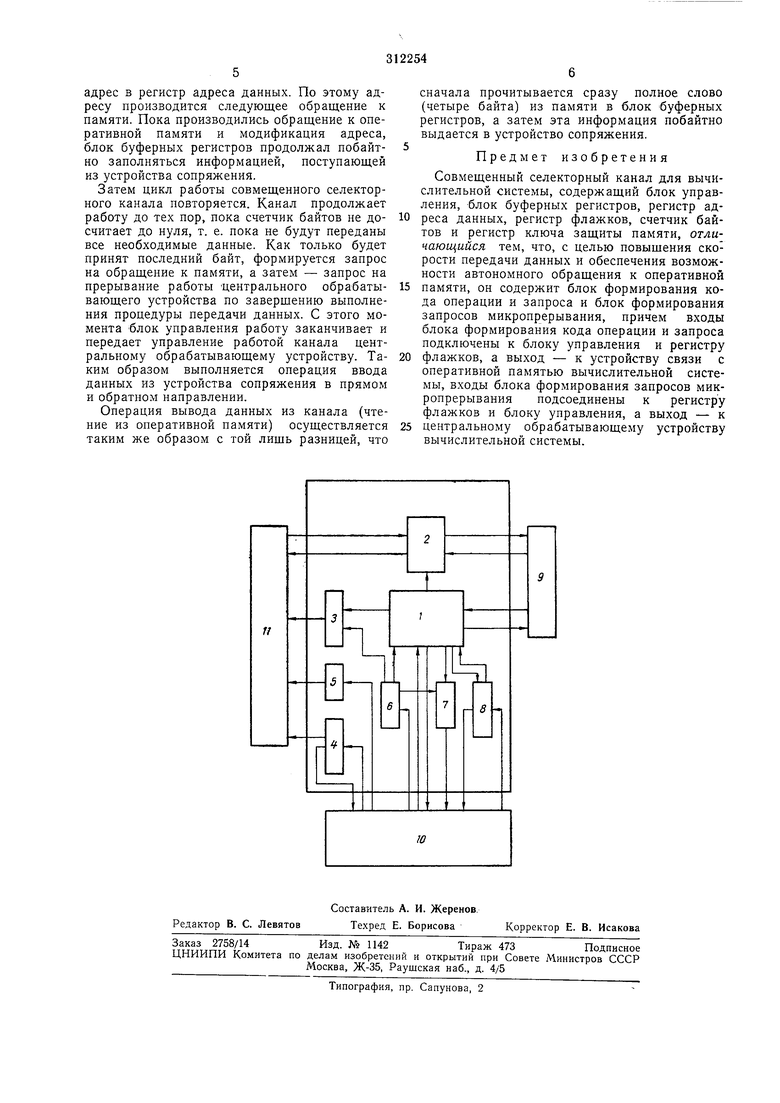

Сущность изобретения заключается в том, что совмещенный селекторный канал содержит блок формирования кода операции и запроса и блок формирования запросов микропрерывания. Входы блока формирования кода операции и запроса подключены к блоку управления и регистру флажков, а выход - к устройству связи с оперативной памятью. Входы блока формирования запросов микропрерывания подсоединены к регистру флажков и блоку управления, а выход - к центральному обрабатывающему устройству.

Канал содержит блок управления /, блок буферных регистров 2, блок формирования кода операции и запроса 3, регистр адреса данных 4, регистр ключа защиты памяти 5,

регистр флажков 6, блок формирования запросов микропрерывания 7, счетчик байтов 8. Блок управления служит для формирования управляющих сигналов для устройства сопряжения 9, блока буферных регистров, блока формирования запросов микропрерывания, счетчика байтов и для центрального обрабатывающего устройства 10 (информации о состоянии канала, контроля автономного оборудования канала). Входы блока управления

подсоединены к устройству сопряжения, счетчику байтов, регистру флажков и центральному обрабатывающему устройству.

Блок буферных регистров служит для промежуточного хранения информации, поступающей как из устройства связи с оперативной памятью //, так и из устройства сопряжения, с которыми он имеет двусторонние связи. Управление блоком буферных регистров осуществляется через блок управления.

Блок формирования кода операции и запроса вырабатывает для оперативной памяти запрос на обращение, команды чтения или записи, а также управляющую информацию о количестве байтов данных, которые должны

мять. Блок связан с блоком управления и регистром флажков.

, Регистр адреса данных служит для хранения адреса данных, которые должны читаться или записываться в оперативную память. Регистр 4 связан двусторонней связью с центральным обрабатывающим устройством и другим выходом с устройством связи с оперативной памятью. Связь регистра 4 с центральным обрабатывающим устройством через выход предназначена для передачи информации из данного регистра в центральное обрабатывающее устройство при модификации адреса.

Регистр ключа защиты памяти осуществляет хранение защитного ключа, предохраняющего ячейки оперативной памяти от проникновения посторонней информации. Регистр 5 имеет связь со стороны входа с центральным обрабатывающим устройством, а со стороны выхода - с устройством связи с оперативной памятью.

Регистр флажков предназначен для хранения кода операции совмещенного селекторного канала (ввод в прямом либо обратном направлении или вывод) и специальных флажков, указывающих на специфические условия операций ввода-вывода (цепочка данных, пропуск данных, остановка ввода-вывода по программе, подавление неправильной длины данных). Регистр 6 связан своим входом с центральным обрабатывающим устройством, а выходом с блоком формирования кода операции и запроса, блоком управления и блоком формирования запросов микропрерывания.

Блок формирования запросов микропрерывания вырабатывает запросы на выполнение прерывания микропрограммы блока микропрограммного управления центрального обрабатывающего устройства при необходимости выполнения модификации адреса данных, при рбработке цепочки данных, при завершении операций ввода-вывода или цепочки команд, при обнаружении ощибок в устройстве сопряжения. При этом управление работой совмещенного селекторного канала передается центральному обрабатывающему устройству. Блок 7 связан с регистром флажков, блоком управления и с центральным управляющим устройством.

Счетчик байтов хранит информацию, которая указывает, какое количество байтов данных нужно принять в канал или выдать из канала. Информационные входы и выходы счетчика 8 подключены к центральному обрабатывающему устройству, а управляющие - к блоку управления.

Работает совмещенный селекторный канал следующим образом.

Установка первоначальной связи с устройством ввода-вывода, подключенным к устройству сопряжения, производится с помощью блока микропрограммного управления центрального обрабатывающего устройства. Если

312254

окалсется, что необходимое устройство вводайывода -свободно, то по той же микропрограмме происходит заполнение информацией из центрального обрабатывающего устройства регистров адреса данных, ключа защиты памяти, флажков 7 и счетчика байтов. После этого из центрального обрабатывающего устройства поступает сигнал «Начать работу совмещенного селекторного канала, и запускается блок управления. С этого момента канал начинает работу автономно, а центральное обрабатывающее устройство переходит к выполнению микропрограмм, не связанных с работой канала. Блок управления вырабатывает управляющие -сигналы, которые поступают в устройство сопряжения и далее в усто ойство ввода-вывода. Работа с устройствами ввода-вывода осуществляется по принципу: запрос-ответ. В ответ на запрос блока управления из устройства сопряжения приходит первый байт данных, который записывается в блок буферных регистров. При этом содержимое счетчика байтов уменьшается на «единицу. Таким же образом происходит запись еще трех байтов данных. Как только в блоке 2 будет накоплено четыре байта данных (слово), из блока 3 выдается запрос на обращение к оперативной памяти. Устройство связи с оперативной памятью, приняв запрос, производит запись данных, хранящихся в блоке буферных регистров, по адресу, записанному в регистре адреса данных в соответствии с кодом операции, сформированным в блоке 3. Одновременно в оперативную память передается ключ защиты памяти из регистра ключа защиты памяти. Ключ защиты памяти осуществляет защиту содержимого определенных областей памяти от разрушения из-за ошибочных засылок информации.

После удовлетворения запроса на обращение к памяти блок управления вырабатывает управляющий сигнал, поступающий в блок формирования запросов микропрерывания, где формируется запрос на прерывание работы центрального обрабатывающего устройства для выполнения модификации адреса данных. Существует два запроса для выполнения модификации адреса: первый запрос формируется при вводе данных в канал в прямом направлении из устройства сопряжения и при выводе данных из капала в устройство сопряжения, второй запрос - при вводе данных в капал в обратном направлении из устройства сопряжения. Первый запрос, прервав работу центрального обрабатывающего устройства, выводит на микропрограмму модификации адреса, при которой происходит увеличение следующего адреса данных. Второй запрос приводит к тому, что следующий адрес данных будет уменьшен. Какой из этих двух запросов будет сфор.мирован, зависит от кода операции канала, хранящегося в регистре флажков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1977 |

|

SU690472A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Селекторный канал | 1978 |

|

SU798779A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Встроенный мультиплексный канал | 1977 |

|

SU734649A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| Блок-мультиплексный канал | 1977 |

|

SU691841A1 |

| Селекторный канал | 1974 |

|

SU525081A1 |

Даты

1971-01-01—Публикация