В настоящее время в вычислительной технике широкое распространение получили параллельные сумматоры.

Известные сумматоры, как правило, имеют недостатки: либо сравнительно низкое быстродействие, либо повышенное использование оборудования.

Предложенное устройство путем создания сумматора с управляемыми элементами памяти (регистрами), способными на время получения промежуточных результатов и суммы образовывать элементы кодово-позиционной схемы сумматора, а затем снова переключаться в элементы памяти для фиксации промел уточных результатов и суммы, позволяет устранить эти недостатки. Достигается это тем, что в нем «единичные и «нулевые входы регистров частной суммы и переноса объединены и подключены к обш;ей шине, блокируюш,ей перекрестные обратные связи. «Единичный и «нулевой входы регистра полной суммы или объединены и связаны с шиной, блокируюш,ей перекрестные обратные связи, или подключены к управляюш,им шинам первоначальной установки, а выходы этого регистра соединены со входами регистров частной суммы и переноса.

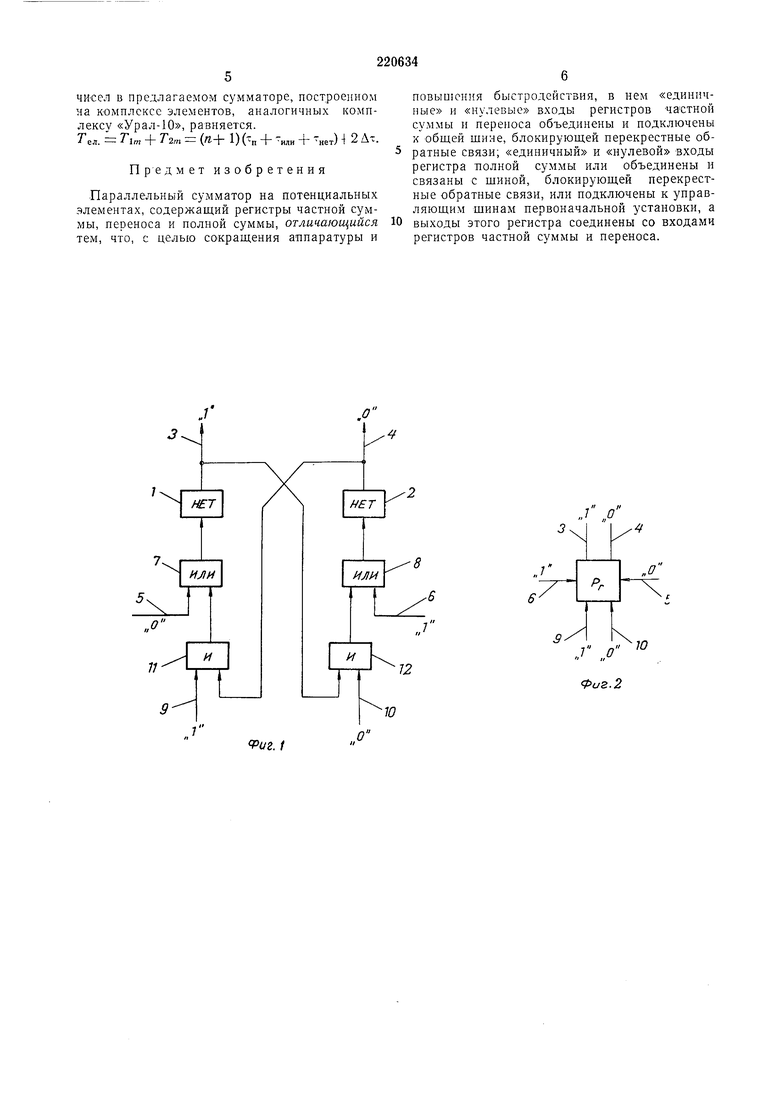

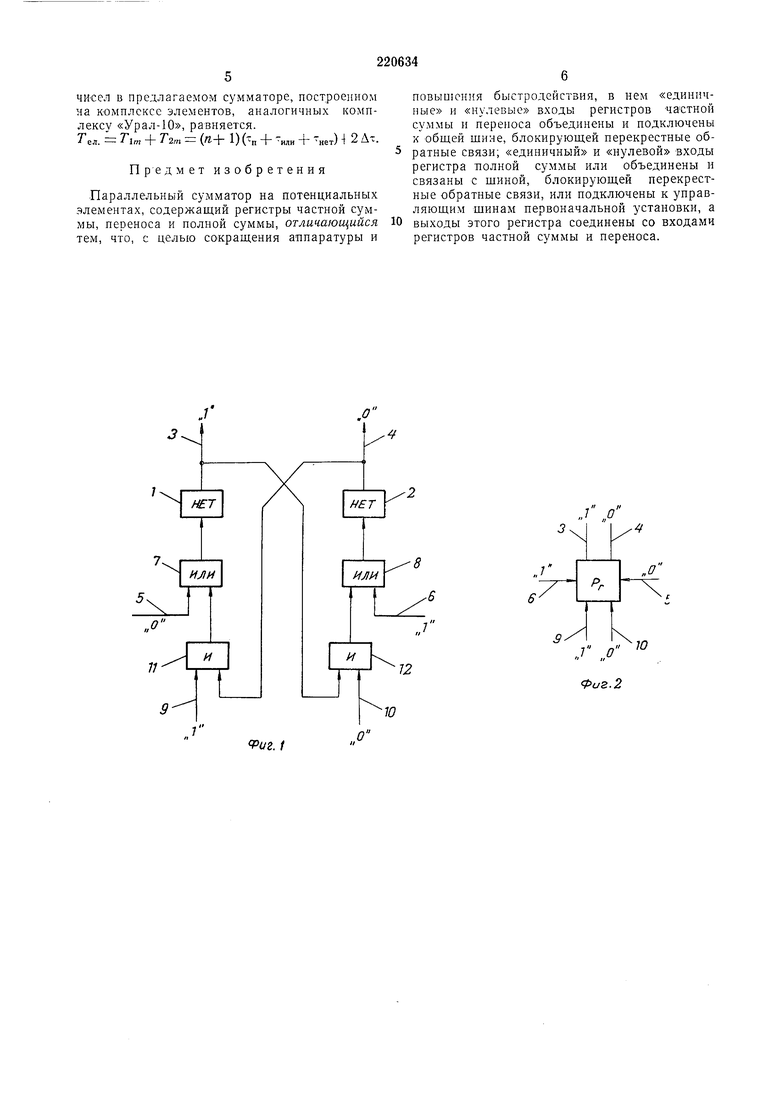

фиг. 3 - функциональная схема сумматора.

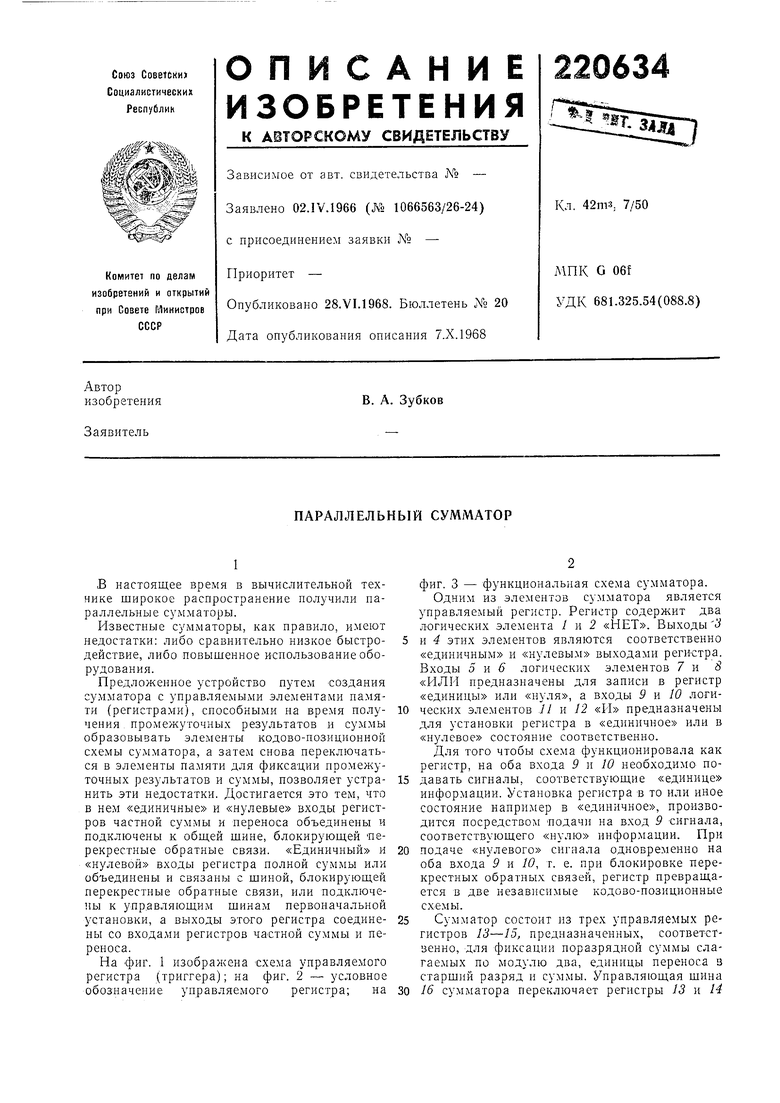

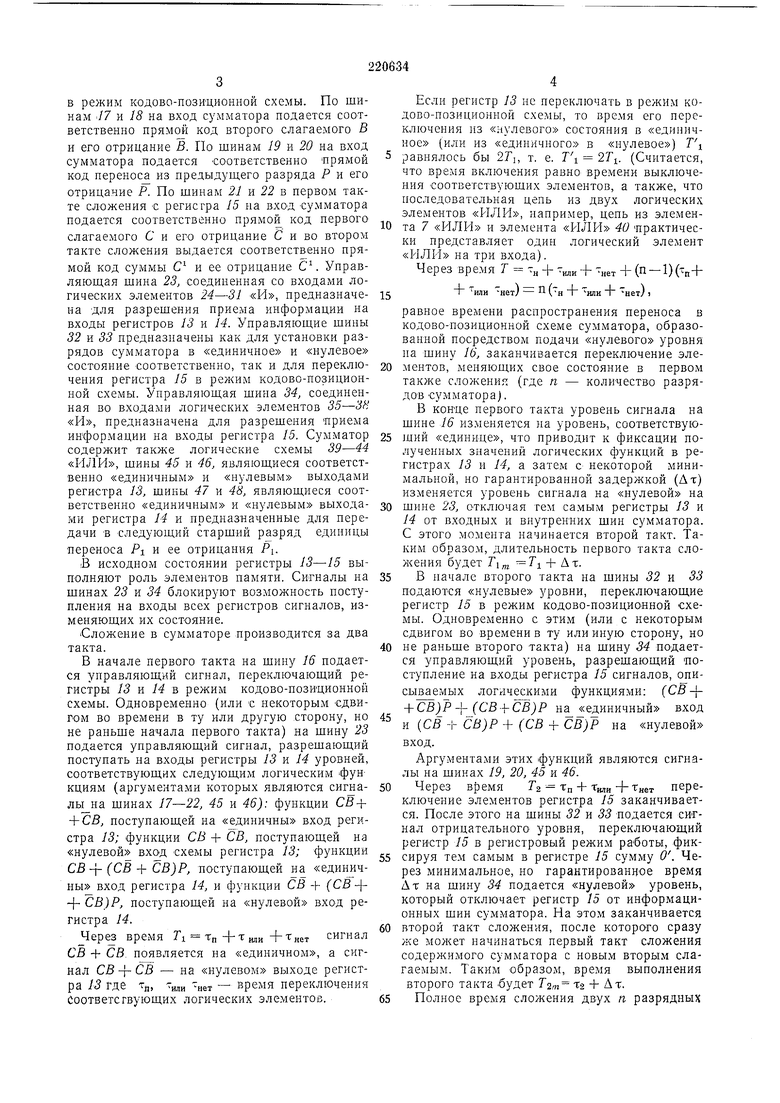

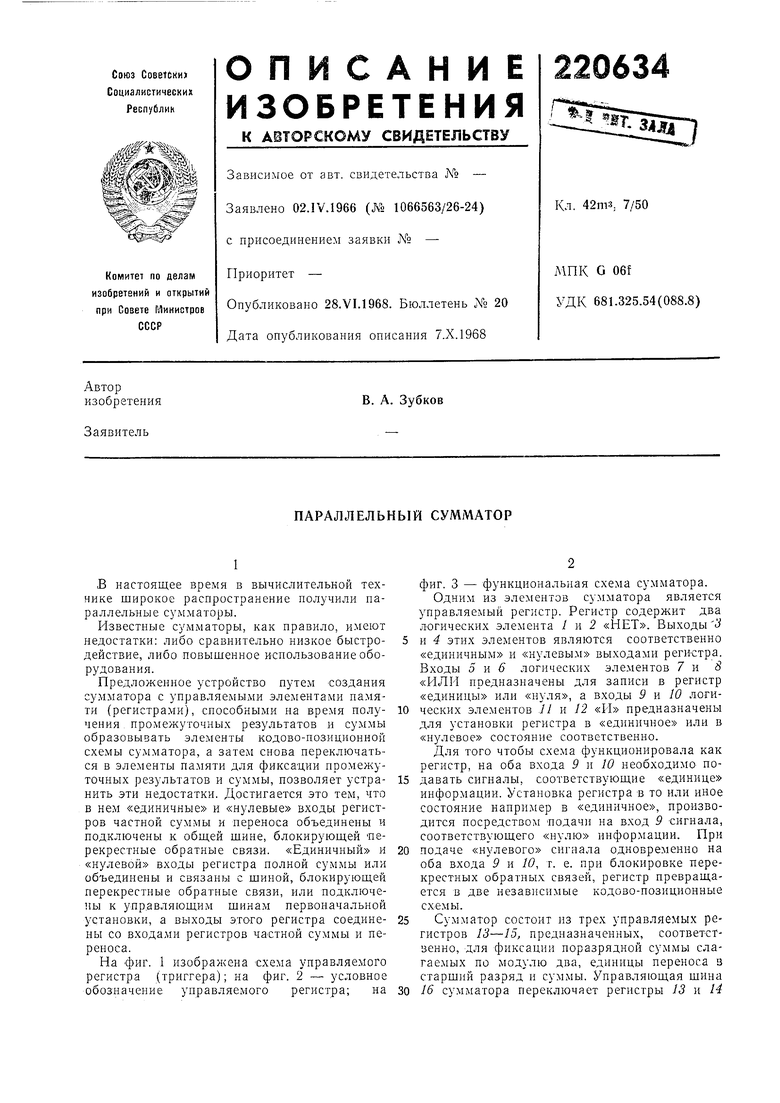

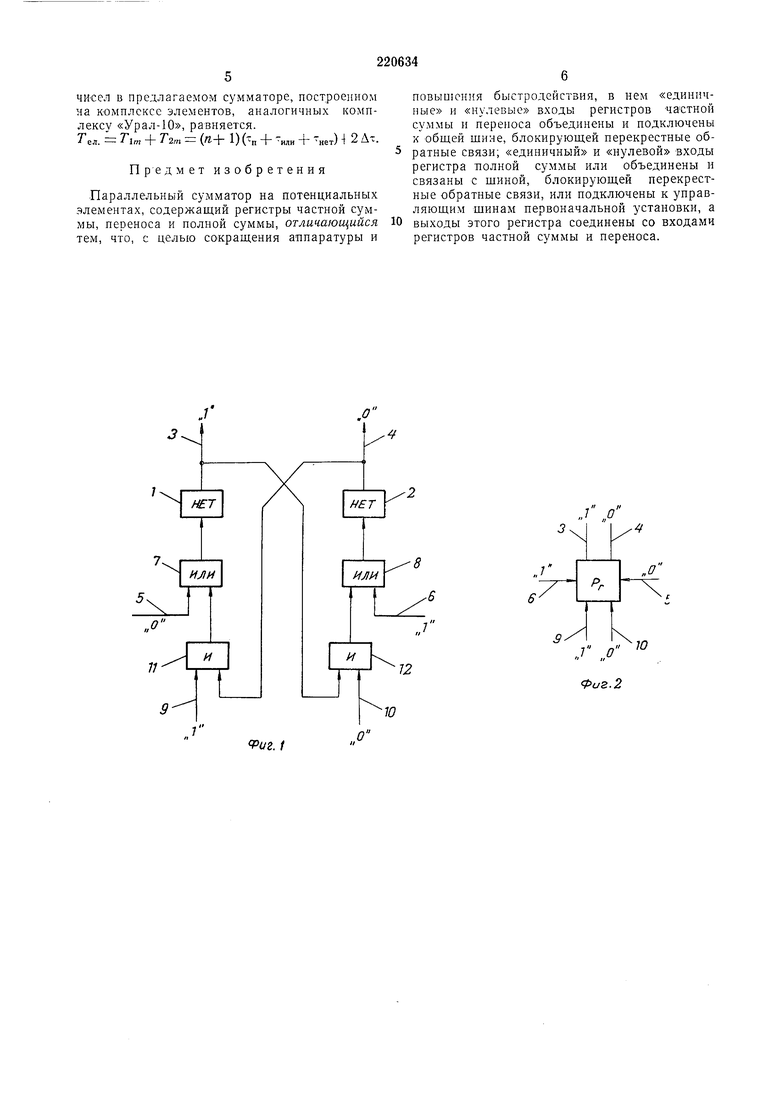

Одним из элементов сумматора является управляемый регистр. Регистр содержит два логических элемента 1 и 2 «НЕТ. Выходы 3 и 4 этих элементов являются соответственно «единичным и «нулевым выходами регистра. Входы 5 и 6 логических элементов 7 и 8 «ИЛИ предназначены для записи в регистр «единицы или «нуля, а входы 9 и 10 логических элементов .// и 12 «И предназначены для установки регистра в «единичное или в «нулевое состояние соответственно.

Для того чтобы схема функционировала как регистр, на оба входа 9 и 10 необходимо подавать сигналы, соответствующие «единице информации. Установка регистра в то или иное состояние например в «единичное, производится посредством подачи на вход 9 сигнала, соответствующего «нулю информации. При

подаче «нулевого сигнала одновременно на оба входа 9 и 10, т. е. при блокировке перекрестных обратных связей, регистр превращается в две независимые кодово-позиционные схемы.

Сумматор состоит из трех управляемых регистров 13-15, предназначенных, соответственно, для фиксации поразрядной суммы слагаемых по модулю два, единицы переноса в старший разряд и суммы. Управляющая шина

в режим кодово-позиционной схемы. По шинам -17 и 18 на вход сумматора подается соответственно прямой код второго слагаемого В и его отрицание В. По шинам 19 и 20 на вход сумматора подается соответственно прямой код переноса из предыдуш,его разряда Р и его отрицание Р. По шинам 21 и 22 в первом такте сложения с регистра 15 на вход сумматора подается соответственно прямой код первого слагаемого С и его отрицание С и во втором такте сложения выдается соответственно прямой код суммы С и ее отрицание С. Управляющая шина 23, соединенная со входами логических элементов 24-31 «И, предназначена для разрешения приема информации на входы регистров 13 и 14. Управляющие шины 32 и 33 предназначены как для установки разрядов сумматора в «единичное и «нулевое состояние соответственно, так и для переключения регистра 15 в режим кодово-позиционной схемы. Управляющая шина 34, соединенная во входами логических элементов 35-ЗН «И, предназначена для разрешения приема информации на входы регистра 15. Сумматор содержит также логические схемы 39-44 «ИЛИ, шины 45 и 46, являюшиеся соответственно «единичным и «нулевым выходами регистра 13, шины 47 и 48, являющиеся соответственно «единичным и «нулевым выходами регистра 14 и предназначенные для передачи в следующий старший разряд единицы переноса Р и ее отрицания РЬ

В исходном состоянии регистры 13-15 выполняют роль элементов памяти. Сигналы на шинах 23 и 34 блокируют возможность поступления на входы всех регистров сигналов, изменяющих их состояние.

Сложение в сумматоре производится за два такта.

В начале первого такта на шину 16 подается управляющий сигнал, переключающий регистры 13 и 14 ъ режим КОДОВО-ПОЗИЦИОННОЙ схемы. Одновременно (или с некоторым сдвигом во времени в ту или другую сторону, но не раньше начала первого такта) на щину 23 подается управляющий сигнал, разрешающий поступать на входы регистры 13 и 14 уровней, соответствующих следующим логическим фун кциям (аргументами которых являются сигналь1 на шинах 17-22, 45 и 46): функции СВ + + СВ, поступающей на «единичны вход регистра 13; функции СВ + СВ, поступающей на «нулевой вход схемы регистра 13; функции СВ-}- (СВ + СВ)Р, поступающей на «единичны вход регистра 14, и функции СВ + ( СВ)Р, поступающей на «нулевой вход регистра 14.

Через время Tt Тп+т „ли +TI

сигнал

Если регистр 13 не переключать в режим кодово-позиционной схемы, то время его переключения i3 «нулевого состояния в «единичное (или из «единичного в «нулевое) Т равнялось бы 2Г, т. е. Т 2Т. (Считается, что время включения равно времени выключения соответствующих элементов, а также, что последовательная цепь из двух логических элементов «ИЛР1, например, цепь из элемента 7 «ИЛИ и элемента «ИЛИ 40 практически представляет один логический элемент «ИЛИ на три входа).

Через время Г т„ + ш,и + нет + (п -1)(п+

т или -нет) П (н Г или l нет) i

равное времени распространения переноса в кодово-позиционной схеме сумматора, образованной посредством подачи «нулевого уровня на шину 16, заканчивается переключение элементов, меняющих свое состояние в первом также сложение: (где п - количество разрядов сумматора).

В конце первого такта уровень сигнала на шине 16 изменяется на уровень, соответствуюший «единице, что приводит к фиксации полученных значений логических функций в регистрах 13 и 14, а затем с некоторой минимальной, но гарантированной задержкой (Дт) изменяется уровень сигнала на «нулевой на

шине 23, отключая тем самым регистры 13 и 14 от входных и внутренних шин сумматора. С этого момента начинается второй такт. Таким образом, длительность первого такта сложения будет TI 7i -f AT.

В начале второго такта на шины 32 и 33 подаются «нулевые уровни, переключающие регистр 15 в режим кодово-позиционной Схемы. Одновременно с этим (или с некоторым сдвигом Во времени в ту или иную сторону, но

не раньше второго такта) на шину 34 подается управляющий уровень, разрешающий поступление на входы регистра 15 сигналов, опксываемых логическими функциями: (СВ + CS)P + (СВ + СВ)Р на единичный вход и (СВ -г )Р + (СВ + СВ)Р на «нулевой вход.

Аргументами этих функций являются сигналы на шинах 19, 20, 45 и 46.

Через время Тд + Тили + Тнет переключение элементов регистра 15 заканчивается. После этого на шины 32 и 33 подается СИГнал отрицательного уровня, переключающий регистр 15 в регистровый режим работы, фиксируя тем самым в регистре 15 сумму О . Через минимальное, но гарантированное время Дт на шину 34 подается «нулевой уровень, который отключает регистр 15 от информационных шин сумматора. Иа этом заканчивается

второй такт сложения, после которого сразу же может начинаться первый такт сложения содержимого сумматора с новым вторым слагаемым. Таким образом, время выполнения второго такта будет то -f- Д т.

чисел в предлагаемом сумматоре, построенном на комплексе элементов, аналогичных комплексу «Урал-10, равняется.

Тел. Т1„ + Т2т (fl+ 1) (т„ + или + нет) i 2 Дт.

Предмет изобретения

Параллельный сумматор на потенциальных элементах, содержащий регистры частной суммы, переноса и полной суммы, отличающийся тем, что, с целью сокращения аппаратуры и

повышения быстродействия, в нем «единичные и «нулевые входы регистров частной суммы и переноса объединены и подключены к общей шине, блокирующей перекрестные обратные связи; «единичный и «нулевой входы регистра полной суммы или объединены и связаны с шиной, блокирующей перекрестные обратные связи, или подключены к управляющим шинам первоначальной установки, а выходы этого регистра соединены со входами регистров частной суммы и переноса.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР | 1971 |

|

SU314746A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОСТАТКА ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ ОТ ЧИСЛА | 1992 |

|

RU2012137C1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

иг. 1

J О

9аг.З

Даты

1968-01-01—Публикация