Изобретение относится к области вычислительной техники и может найти применение при аппаратном вычислении элементарных функций в цифровых вычислительных ManjHнах с плавающей запятой.

Известно устройство для получения псевдочастпого при вычислении элементарной функции arctg :, содержащее регистры, сумматор и счетчик.

Недостатком такого устройства является низкая точность вычисления функции arctg х. С ростом модуля отрицательного порядка аргумента элементарной функции arctg х псевдочастное получается денормализованным, а количество нулей в старших разрядах равно модулю порядка.

Целью изобретения является устранение указанного недостатка, т. е. получение псевдочастного сразу в нормализованном виде без увеличения разрядности операционных регистров.

Поставленная цель достигается введением в схему счетчика сдвигов модификатора для получения нсевдочастного. В случае положительного порядка аргумента выполняется обратное псевдоделение и получается нормализованное псевдочастное для дополнительного

отрицательного порядка.

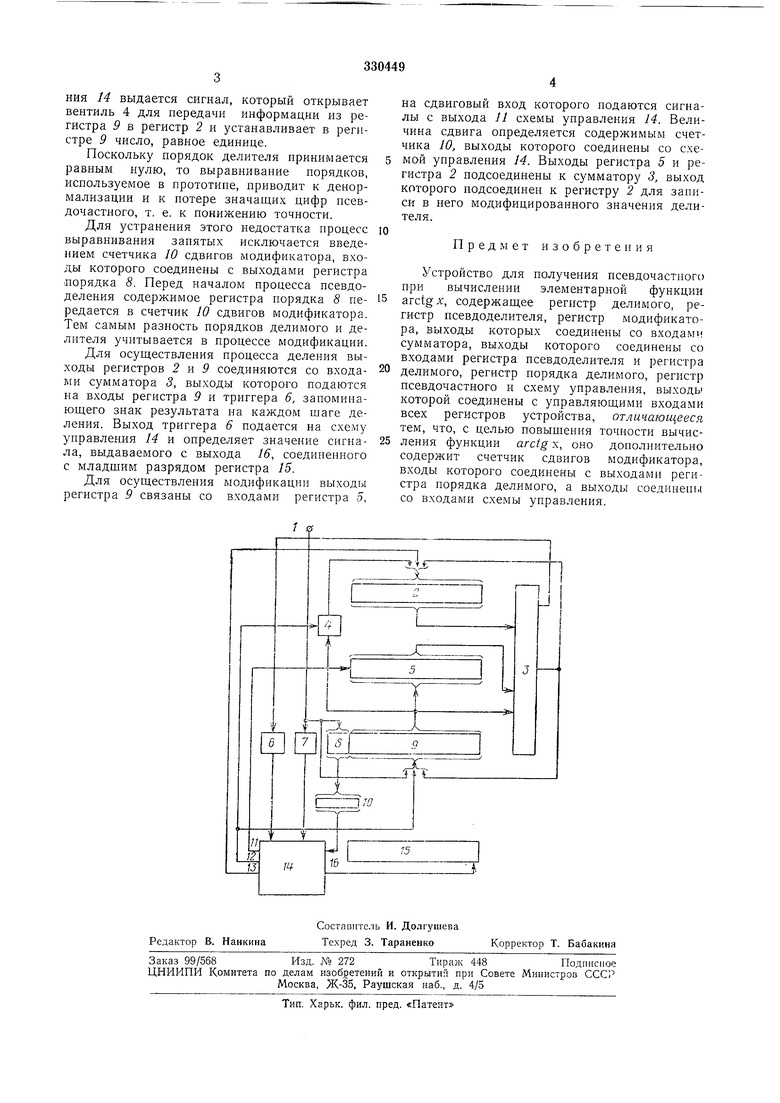

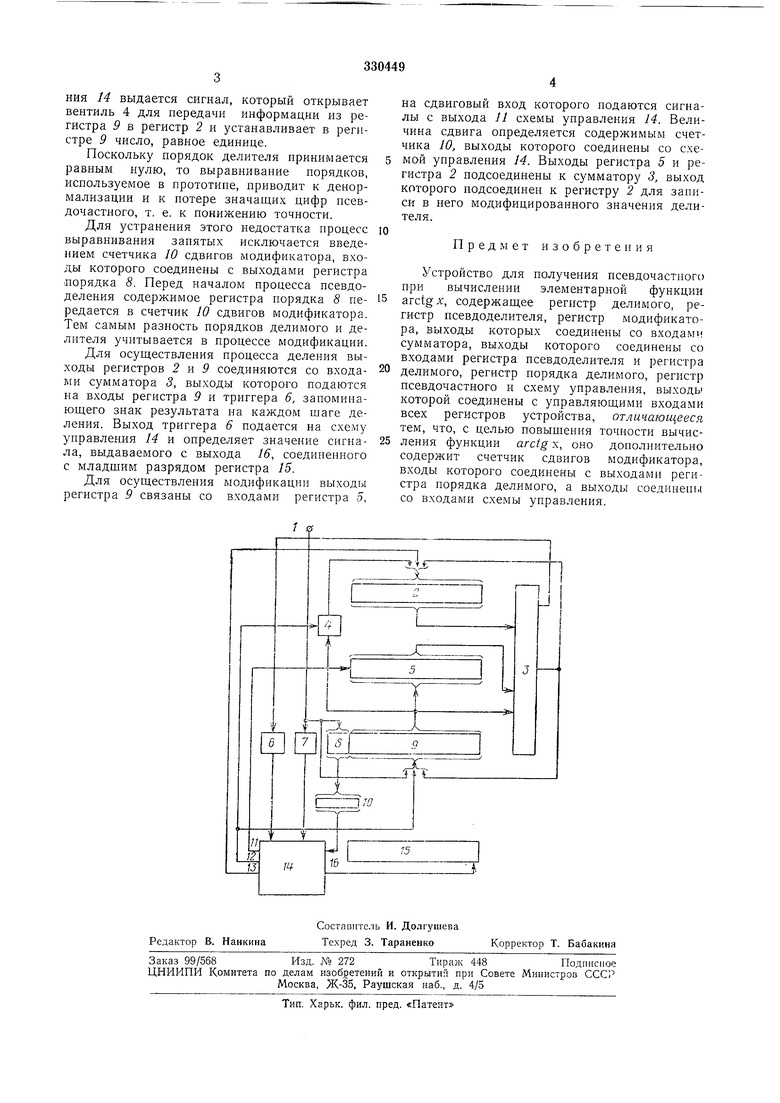

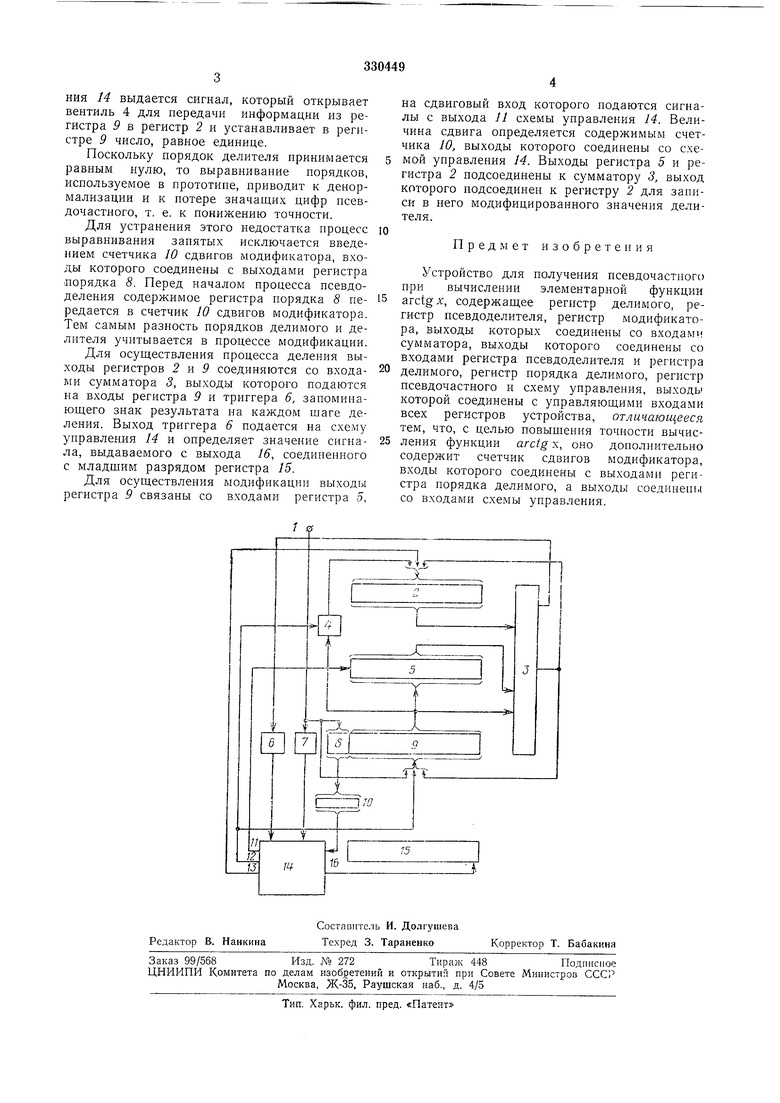

На чертеже представлена блок-схема устройства для получения псевдочастного при вычислении элементарной функции arctg х, где:

/ - числовой вход для записи мантиссы и порядка аргумента; 2 - регистр псевдоделителя; 3 - сумматор; 4 - вентиль передачи в регистр 2; 5 - регистр модификатора; 6 - триггер знака делимого; 7 - триггер знака порядка делимого; 8 - регистр порядка делимого; 9 - регистр делимого; 10 - счетчик сдвигов модификатора; 11 - выход схемы управления для передачи сигнала сдвига регистра модификатора 5; 12 - выход схемы управления для передачи из регистра 9 в регистр 2 и записи «1 в регистр 9; 13 - выход схемы управления для записи «1 в регистр 2; 14 - схема управления; 15 - регисто

0 псевдочастного; 16 - выход схемы управления для занесения информации в регистр.

Мантисса и порядок аргумента элементарной функции arctg Л , поступающие на вход /,

- записываются в регистры 8 и 9, знак порядка аргумента записывается в триггер 7. Если знак порядка отрицательный, то с выхода 13 схемы управления 14 выдается сигнал, который записывает в регистр 2 число, равное единице. При положительном значении порядка аргумента с выхода 12 схемы управле

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1973 |

|

SU546890A1 |

| Устройство для вычисления элементарных функций | 1974 |

|

SU560229A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU911519A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

| Цифровой генератор функций | 1984 |

|

SU1168921A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

Даты

1972-01-01—Публикация