Изобретение относится к области вычислительной техники и предназначено для суммирования двоичных кодов с обнаружением ошибок вычислений в коде 12222.

Известны сумматоры, обнаружение ошибок в которых осуществляется контролем по модулю или проверкой но четности.

Предложенное устройство отличается тем, что счетный вход его триггера контрольного знака соединен с выходом входной схемы «ИЛИ, входы этой схемы-с выходами схем «И переноса и нечетности обоих слагаемых, с шинами приема контрольного разряда второго слагаемого, сигнала управления и переноса с младшего десятичного разряда, выходы триггера контрольного знака связаны с входами схемы несовпадения, соединенной по входу также с выходом схемы свертки, а выходы схемы несовпадения и схем «И фиксации комбинаций «01 - с входами выходной схемы «ИЛИ.

Это позволяет упростить схему устройства при суммировании с обнаружением ошибок.

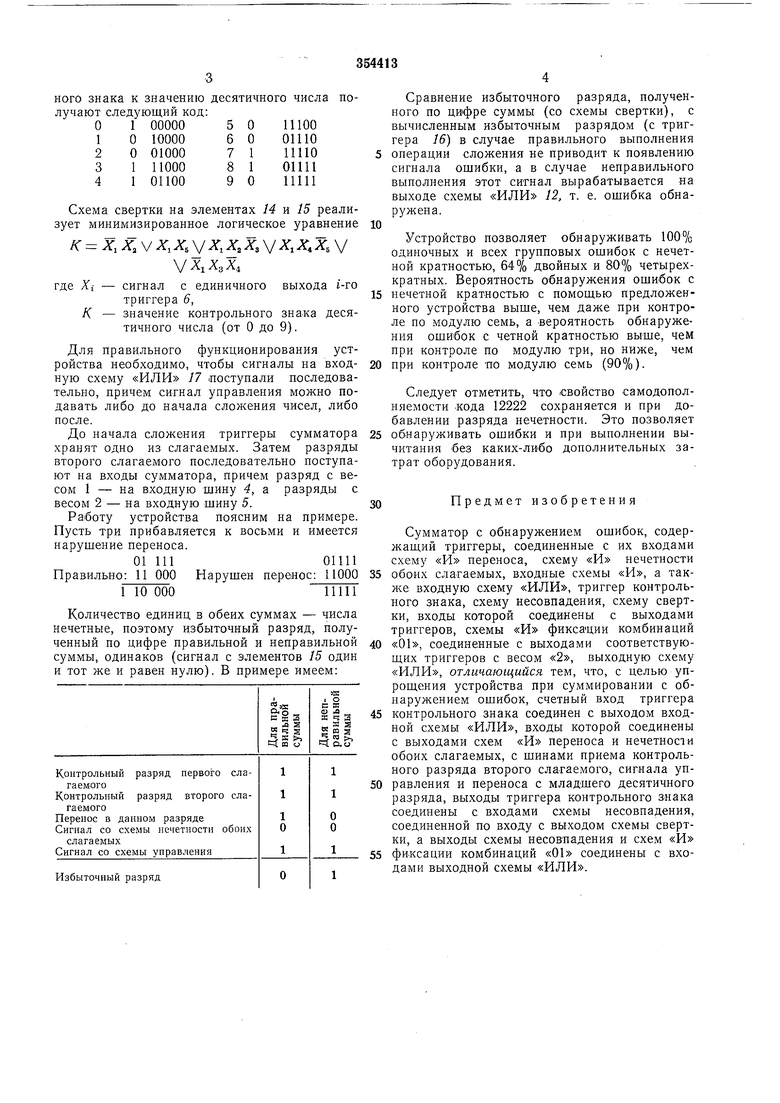

Схема устройства (для одного десятичного разряда) показана на чертеже.

Устройство включает собственно сумматор /, работаюший в коде 12222 и содержащий в свою очередь схему «И 2 переноса (из данного десятичного разряда), схему «И 5 нечетцости обоих слагаемых, шины 4 и 5 приема разрядов второго слагаемого, триггеры 6, входные схемы «И 7 и схему «ИЛИ 8. Устройство содержит также шины Я 0 и // нриема контрольного разряда второго слагаемого, сигнала управления и переноса с младшего десятичного разряда соответственно, выходную схему «ИЛИ 12, схемы «И 13 фиксации комбинаций «01, схему свертки (схему выработки контрольного знака су.ммы) на

элементах конъюнкции 14 и дизъюнкции 15, триггер 16 контрольного знака (первого слагаемого и суммы), входную схему «ИЛИ 17, схему 18 несовпадения на элементах «ИЛИ- ПЕ 19, 20 и «НЕ 21.

В предложенном устройстве для обнаружения ошибок используют метод контроля на нечетность, при котором к коду числа добавляют контрольный знак. Значение этого знака («О или «1) выбирают таким образом, чтобы общее число единиц было всегда нечетным. Тогда любая кодовая комбинация, о том числе и изображающая нуль, имеет хотя бы одну единицу (контрольный знак). Это дает возможность отличить полное отсутствие информации от передачи нуля, если едииица изображается в машине наличием электрического сигнала, а нуль - отсутствием его.

ого знака к значению десятичного числа поучают следующий код:

11100

О 1 2 3 4

00000

О О 1 1 О

ото 10000

О О

11110 01000

7 8 9 01111 11000 01100

11111

Схема свертки на элементах 14 и 15 реализует минимизированное логическое уравнение

,X,V X,X,/X,X,X,JX,X,X, V ,

где Xi - сигнал с единичноговыхода i-ro

триггера 6,

/( - значение контрольногозна.ка десятичного числа (от О до9).

Для правильного функционирования устройства необходимо, чтобы сигналы на входную схему «ИЛИ 17 поступали последовательно, причем сигнал управления можно подавать либо до начала сложения чисел, либо после.

До начала сложения триггеры сумматора хранят одно из слагаемых. Затем разряды второго слагаемого последовательно поступают на входы сумматора, причем разряд с весом 1 - на входную шину 4, а разряды с весом 2 - на входную шину 5.

Работу устройства поясним на примере. Пусть три прибавляется к восьми и имеется нарушение переноса.

01 11101111

Правильно: 11 000 Нарушен перенос: 11000

1 10 00011111

Количество единиц в обеих суммах - числа нечетные, поэтому избыточный разряд, полученный по цифре правильной и неправильной суммы, одинаков (сигнал с элементов 15 один и тот же и равен нулю). В примере имеем:

Сравнение избыточного разряда, полученного по цифре суммы (со схемы свертки), с вычисленным избыточным разрядом (с триггера 16} в случае правильного выполнения операции сложения не приводит к появлению сигнала ошибки, а в случае неправильного выполнения этот сигнал вырабатывается на выходе схемы «ИЛИ 12, т. е. ошибка обнаружена.

Устройство позволяет обнаруживать 100% одиночных и всех групповых ошибок с нечетной кратностью, 64% двойных и 80% четырехкратных. Вероятность обнаружения ошибок с

нечетной кратностью с помошью предложенного устройства выше, чем даже при контроле по модулю семь, а -вероятность обнаружения ошибок с четной кратностью выше, чем при контроле по модулю три, но ниже, чем

при контроле по модулю семь (90%).

Следует отметить, что свойство самодополняемости Кода 12222 сохраняется и при добавлении разряда нечетности. Это позволяет обнаруживать ошибки и при выполнении вычитания без каких-либо дополнительных затрат оборудования.

Предмет изобретения

Сумматор с обнаружением ошибок, содержащий триггеры, соединенные с их входами схему «И переноса, схему «И нечетности

обоих слагаемых, входные схемы «И, а такл ;е входную схему «ИЛИ, триггер контрольного знака, схему несовпадения, схему свертки, входы которой соединены с выходами триггеров, схемы «И фиксации комбинаций

«01, соединенные с выходами соответствующих триггеров с весом «2, выходную схему «ИЛИ, отличающийся тем, что, с целью упрощения устройства при суммировании с обнаружением ошибок, счетный вход триггера

контрольного знака соединен с выходом входной схемы «ИЛИ, входы которой соединены с выходами схем «И переноса и нечетности обоих слагаемых, с шинами приема контрольного разряда второго слагаемого, сигнала управления и переноса с младшего десятичного разряда, выходы триггера контрольного знака соединены с входами схемы несовпадения, соединенной по входу с выходом схемы свертки, а выходы схемы несовпадения и схем «И

фиксации комбинаций «01 соединены с входами выходной схемы «ИЛИ.

/8l I

3 0 цЭ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для преобразования двоично-десятичных чисел в двоичные | 1988 |

|

SU1557680A2 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1424060A1 |

| Распределитель импульсов с контролем | 1985 |

|

SU1265993A1 |

| Пирамидальная свертка по модулю три | 1989 |

|

SU1695308A2 |

| Устройство для деления | 1989 |

|

SU1667077A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Устройство для умножения | 1989 |

|

SU1689946A1 |

| УСТРОЙСТВО ДЛЯ СВЕРТКИ ПО МОДУЛЮ ТРИ | 1991 |

|

RU2011215C1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Параллельный комбинационный сумматор | 1981 |

|

SU1005038A1 |

Даты

1972-01-01—Публикация