Предлагаемое изобретение может быть использовано в электронных вычислительных машинах для ускоренного формирования контрольного разряда регистров, работающих в режиме простых или реверсивных счетчиков.

Обычно для формирования контрольного разряда регистров, счетчиков используется та же, что и для контроля, схема «свертки, которая суммирует по модулю два содержимое счетчика и в зависимости от получившейся суммы устанавливает значение контрольного разряда. Запуск схемы на формирование контрольного разряда производится после окончания модификации, т. е. после того, как в счетчике окончательно установится новое значение числа.

Кроме того, «свертка присваивает повое значение контрольному разряду только в зависимости от содержимого счетчика, т. е. и при неверной модификации контрольный разряд, сформированный «сверткой, будет соответствовать неверному значению счетчика, что не позволяет проверить правильность модификации.

Предлагаемое устройство позволяет устанавливать контрольный разряд одновре.менно с окончанием модификации, причем его значение соответствует содержимому счетчика, которое должно быть при правильной модификации.

Применение предлагаемого устройства не только уменьшает время формирования контрольного разряда, но и позволяет проверить правильность выполпения модификации.

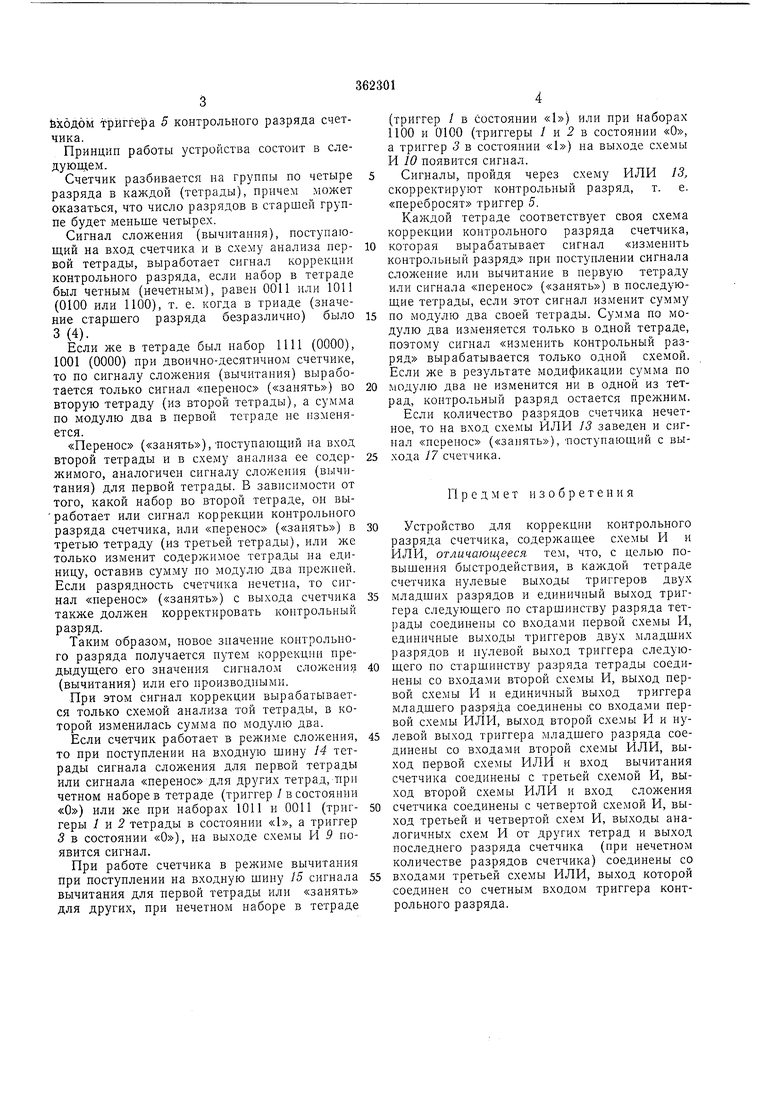

На чертеже ноказана блок-схема предлагаемого устройства.

Устройство содержит триггеры /-4, триггер 5 контрольного разряда регистра 6, работающего в режиме реверсивного двоичного или двоичпо-десятичного счетчика, с.хемы И 7-10 и схемы ИЛП 11-}3.

Нулевые выходы триггеров / и 2 и единичный выход триггера 3 соединены с входами с.хемы И 7, другие же вы.ходы этих триггеров соединены с входами схемы И 8. Выход схе.мы И 7 и единичный выход триггера / соединены со входами с.хемы ИЛН 12, а выход схемы Н 8 и пулевой выход триггера / - с в.ходами схемы ПЛИ //. Сигналы с выходов схем ИЛИ 1} и 12 поступают па входы соответственно схем И 9 и W, вторые входы которых соединены с в.ходной шиной 14 сложения («перенос) и входной щиной 15 вычитания (или «занять).

Выходы схем И 9 и W соединены со входами схемы ИЛИ 13, остальные входы которой соединены с выходами 16 аналогичных схем от других тетрад и при нечетном количестве разрядов счетчика - с выходом 17 счетчика, а выход схемы ИЛИ 13 соедтшен со счетным

Ёходдм триггера 5 контрольного разряда счетчика.

Принцип работы устройства состоит в следующем.

Счетчик разбивается на группы по четыре разряда в каждой (тетрады), причем может оказаться, что число разрядов в старшей группе будет меньше четырех.

Сигнал сложения (вычитания), поступающий на вход счетчика и в схему анализа первой тетрады, выработает сигнал коррекции контрольного разряда, если набор в тетраде был четным (нечетным), равен ООН или 1011 (0100 или 1100), т. е. когда в триаде (значение старшего разряда безразлично) было 3 (4).

Если же в тетраде был набор 1111 (0000), 1001 (0000) при двоично-десятичном счетчике, то по сигналу сложения (вычитания) выработается только сигнал «перенос («занять) во вторую тетраду (из второй тетрады), а сумма по модулю два в первой тетраде не изменяется.

«Перенос («занять),поступающий на вход второй тетрады и в схему анализа ее содержимого, аналогичен сигналу сложения (вычитания) для первой тетрады. В зависимости от того, какой набор во второй тетраде, он выработает или сигнал коррекции контрольного разряда счетчика, или «перенос («занять) в третью тетраду (из третьей тетрады), или же только изменит содержимое тетрады на единицу, оставив сумму ио модулю два прежней. Если разрядность счетчика нечетна, то сигнал «перенос («занять) с выхода счетчика также должен корректировать контрольный разряд.

Таким Образом, новое значение контрольного разряда получается путем коррекции предыдущего его значения сигналом cлoжeни J (вычитания) или его производными.

При этом сигнал коррекции вырабатывается только схемой анализа той тетрады, в которой изменилась сумма ио модулю два.

Если счетчик работает в режиме сложеиия, то при поступлении на входную шину 14 тетрады сигнала сложения для первой тетрады или сигнала «перенос для других тетрад,при четном наборе в тетраде (триггер / в состоянии «О) или же при наборах 1011 и ООН (триггеры 1 н 2 тетрады в состоянии «1, а триггер 3 в состоянии «о), на выходе схемы И 9 появится сигнал.

При работе счетчика в режиме вычитания при поступлении на входную шипу 15 сигнала вычитания для первой тетрады или «занять для других, при нечетном наборе в тетраде

(триггер / в состоянии «1) или при наборах 1100 и 0100 (триггеры / и 2 в состоянии «О, а триггер 3 в состоянии «1) на выходе схемы И 10 появится сигнал.

Сигналы, пройдя через схему ИЛИ 13, скорректируют контрольный разряд, т. е. «перебросят триггер 5.

Каждой тетраде соответствует своя схема коррекции контрольного разряда счетчика,

которая вырабатывает сигнал «изменить контрольный разряд при поступлении сигнала сложение или вычитание в первую тетраду или сигнала «перенос («занять) в последующие тетрады, если этот сигнал изменит сумму

по модулю два своей тетрады. Сумма по модулю два изменяется только в одной тетраде, поэтому сигнал «изменить контрольный разряд вырабатывается только одной схемой. Если же в результате модификации сумма по

модулю два не изменится ни в одной из тетрад, контрольный разряд остается прежним. Если количество разрядов счетчика нечетное, то на вход схемы ИЛИ 13 заведен и сигпал «перенос («занять), поступаюш.ий с выхода 17 счетчика.

Предмет изобретения

Устройство для коррекции контрольного разряда счетчика, содержаигее схемы И и ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в каждой тетраде счетчика нулевые выходы триггеров двух

младших разрядов и единичный выход триггера следующего по старшинству разряда тетрады соединены со входами первой схемы И, единичные выходы триггеров двух младших разрядов и нулевой выход триггера следуюшего по старшинству разряда тетрады соединены со входами второй схемы И, выход первой схемы И и единичный выход триггера младшего разряДа соединены со входами первой схемы ИЛИ, выход второй схемы И и нулевой выход триггера младшего разряда соединены со входами второй схемы ИЛИ, выход первой схемы ИЛИ и вход вычитания счетчика соединены с третьей схемой И, выход второй схемы ИЛИ и вход сложения

счетчика соединены с четвертой схемой И, выход третьей и четвертой схем И, выходы аналогичных схем И от других тетрад и выход последнего разряда счетчика (при нечетном количестве разрядов счетчика) соединены со

входами третьей схемы ИЛИ, выход которой соединен со счетным входом триггера контрольного разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции контрольного разряда счетчика | 1978 |

|

SU785868A2 |

| Устройство для контроля двухтактного двоичного счетчика | 1975 |

|

SU607221A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| ДВОИЧНО-ДЕСЯТИЧНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО | 1968 |

|

SU220631A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

| УСТРОЙСТВО для СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1972 |

|

SU332459A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1336011A2 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для возведения в квадрат | 1988 |

|

SU1534458A2 |

| Устройство для контроля двухтактного двоичного счетчика | 1981 |

|

SU970375A1 |

Авторы

Даты

1973-01-01—Публикация