Изобретение относится к цифровой технике и может быть использовано для контроля счетчиков. По основному авт.св. № 362301 известно устройство, содержсвдее в каждой тетраде счетчика четыре элемента И, три элемента ИЛИ, триггер контрольного раэряда З, Недостатком устройства является то, что оно не осуществляет контрол текущего кода информации, так как для этого необходимо дополнительное оборудование для сравнения четности кода и сформированного контрольного разряда. Целью изобретения является расши рение функциональных возможностей устройства, заключающееся в контрол по mod 2 кода счетчика. Поставленная цель достигается тем что в устройство, каждая тетрада счетчика которого содержит четыре элемента И, три элемента ИЛИ, триггер контрольного разряда, входы первого элемента И соединены с нулевым и единичным выходами соответственно третьего и второго разрядов тетрады единичный и нулевой выходы которых соединены с входами второго элементу И, выходы первого и второго элементов и соединены соответственно с первыми входами первого и второго эле,ментов ИЛИ, вторые входы которых соединены соответственно с единичным и нулевш1 выходом первого разряда тетра,цы счетчика, а выходы - соответственно с первыми входами третьего и . четвертого элемента И, вторые входы которых соединены соответственно с входом сложения и вычитания тетрады счетчика, а выходы, а также выходы аналогичных элементов И других тетрад счетчика, соединены с входами третьего элемента ИЛИ, выход которого соединен со счетным входом триггера контрольного разряда, для каждой тетрады счетчика введены триггер ошибки/ два элемента задержки, дополнительный элемент И и два дополнительных элемента ИЛИ, входы сложения и вычитания тетрады счетчика соединены соответс венно с входами первого и второго элементов Зсщержки и первыми входами первого и второго дополнительных элементов ИЛИ, вторые входы которых соединены соответственно с выходами второго и первого элементов задержки, а выходы - со вторыми входами соответственно третьего и четвертого элементов И, первый вход дополнительного элемента И соединен с вы-ч ходом третьего элемента ИЛИ и счетнь входом триггера ошибки, второй вход с управляющим входом устройства, а выход - со счетнЕлм входом триггера контрольного разряда.

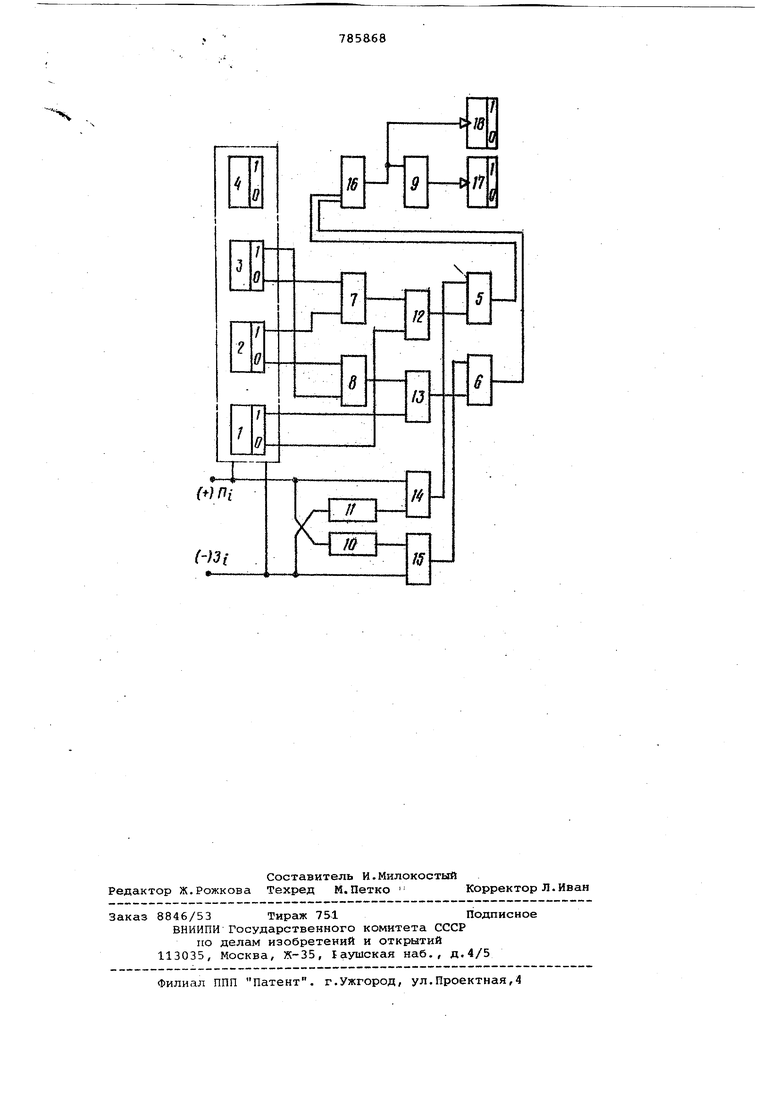

Структурная схема устройства представлена на чертеже.

Устройство содержит триггеры 14, элементы И 5-9, элементы задержки 10 и 11, элементы ИЛИ 12-16, триггер 17 контрольного разряда, триггер 18 ошибки.

Устройство работает следующим образом.

Как и в прототипе, значение контрольного разряда счетчика в очередном такте формируется путем коррекции контрольного разряда в текущем такте на основе анализа (в момент поступления сигнала модификации) значений разрядов счетчика-в текущем такте, Для первой тетрады сигналами модификации являются сигналы сложения или вычитания, а для тетрады ( )..сигнал переноса () из(|-1)-ой тетрады (при сложении) или сигнала займа ( ) в (i-l)-yro тетраду. Причем сигнал вырабатывается только при единичных, а сигнал 3 только при нулевых значениях всех разрядов во всех предшествующих (l,2,...i-l) тетрадах.

Сигнал коррекции вырабатывается одним из узлов коррекции при сложении или при вычитании той тетрады, в которой при модификации должна измениться сумма по mod 2 набора значений разрядов. При каждой модификации изменение суммы по mod 2 возможно только в одной (i-ой) тетргще. Сигна коррекции в этой тетраде при сложени формируется, если в тетраду поступил сигнал переноса (П..) и набор тетрады удовлятворяет одному из следующих требований:

-значения младшего (первого) разряда (х) равно нулю;

-значение второго {х,,) и третьего (xj) разрядов равны 1 и О соответственно,

т.е. если выполняется условие:

Пц ( VxJ 1 (1) Аналогично, при вычитании сигнал коррекции формируется в i-ой тетраде если выполняется условие

3 ( х ) 1 (2) Если при модификации сумма по mod 2 не изменяется ни в одной тет рс1де, то сигнал коррекции не вырабатывается ни в оддной тетраде, и значение контрольного разряда в очередном такте не изменяется.

Пусть, например, при выполнении сложения (вычитания) набор значений разрядов 1-ой тетрады был равен 1011 (1100) и на вход тетрады поступил сигнал переноса П(займа , т.е. выполняется условие (1) при сложении

(условие (2) при вычитании). Тогда в момент поступления сигнала n(3i) на. выходе узла коррекции при сложении (узла коррекции при вычитании) этой тетрады формируется сигнал коррекции контрольного разряда. С выхода элемента И 5 (и 6) он поступает через элемент ИЛИ 16, второй вход элемента И 9 (на первый вход элемента И 9 в это время поступает сигнал сложения (вычитания) счетчика на счетный вход триггера контрольного разряда 17 и изменяет его состояние,

Таким образом, по значению разрядов тетрады 1011 (1100) в текущем такте сформировано значение контрольного разряда счетчика в очередном такте для набора 1100 при сложении (1011 при вычитании), которое вместе с содержимым счетчика может пересылаться в другие узлы или устройства ЭВМ для контроля правильности пересылки.

Принцип контроля счетчика заключается в следующем.

Если при сложении (вычитании) по модификации, т.е. в текущем такте, в i-ой тетраде выполняется условие (1)(условие (2) при вычитании), то после модификации для этой же тетрады будет выполняться условие:

х Х,,УХ 1 при сложении, (3)

х XjjVx 1 при вычитании.

Если теперь после модификации сформировать и подать при сложении на вход узла коррекции при вычитании (при вычитании - на вход узла коррекции при сложении) сигнал 3 ( ) , то для этой же тетрады будет выполняться при сложении условие (.} (при вычитании - условие (1) . Сигнал () представляет собой задержанный элементом задержки на время, равное времени модификации тетрады счетчика сигнал П- () .

Таким образом, в каждом такте работы счетчика при изменении суммы по mod 2 сигнал коррекции вырабатывается дважды: при сложении (вычитании) сначала узлом коррекции при сложении (узлом коррекции при вычитании) по текущему значению разрядов тетрады, а после модификации - узлом коррекции при вычитании (узлом коррекции при сложении) по очередному (сформированному в результате модификации) значению разрядов тетрады. При правильной работе счетчика возможны 2 случая:

-если сумма по mod 2 значений разрядов счетчика после модификаций не изменяется, то ни один из узлов коррекции при сложении и при вычитании не формирует сигнала коррекции

ни до модификации, ни после модификации ;

-если же сумма по mod 2 изменяется после модификации, то каждый узел коррекции той тетрады, в которой изменяется сумма, формирует один сигнал коррекции. Причем эти сигналы по времени разнесены на интервал, равный времени модификации тетрады счетчика Сигналы коррекции фиксируются с помощью триггера ошибки.

В исходном состоянии триггер ошибки находится в нулевом состоянии . Поэтому при правильной работе счетчика после модификации триггер ошибки всегда будет находиться в нулевом состоянии. При неправильном переходе счетчика в очередное состояние формируется только один сигнал коррекции, что является признаком обнаружения ошибки, фиксируемым единичным состоянием триггера ошибки.

Так, в рассматриваемом примере, при сложении (вычитании) первый сигнал коррекции, сформированный узлом коррекции при сложении (узлом коррекции при вычитании) в момент поступления сигнала П-(), поступает с выхода элемента И 5 (и 6) через элемент ИЛИ 16 на счетный вход триггера ошибки 18 и устанавливает его в единичное состояние. Этот же сигнал П.,-(3.) поступает через элемент задержки 10 (11 элемент ИЛИ 15 (ИЛИ 14) на второй . вход элемента И 6 (И 5) узла коррекции при вычитании (узла коррекции при сложении) к моменту окончания модификации разрядов тетрады, т.е. к моменту, когда набор тетрады установится равнь5м 1100 (1011).

При данном наборе на выходе узла коррекции при вычитании (коррекции при сложении) формируется второй сигнал коррекции, который через элемент ИЛИ 16 поступает на вход триггера 18 и устанавливает его в нулевое состояние.

Пусть, например, в результате сбоя в рассматриваемой тетраде установился набор не 1100 (1011), а набор 1110 (1001). Тогда после модификации условие (3) не выполняется, второй

сигнал коррекции не вырабатывается, и триггер ошибки к моменту очередной модификации останется в единичном сог стоянии, что свидетельствует об ошибке в работе счетчика.

Таким образом, введение указанных элементов и соответствующих связей позволяет осуществить контроль текущего кода счетчика без традиционной схемы свертки по mod 2 кода счетчика и контрольного разряда.

Формула изобретения

Устройство для коррекции контрольного разряда счетчика по авт.св. W 362301, отличающееся тем, что, с целью расширения функциональных возможностей устройства, заключающемся в контроле по mod 2 кода счетчика, между входами вычитания и сложения устройства и вторыми входами третьего и четвертого элементов И введены два дополнительных элемента ИЛИ, два элемента задержки, входы сложения и вычитания устройств соединены соответственно с входами первого и второго элементов задержки и первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены с выходами соответственно второго и первого эл&ментов задержки, а между выходом тр)ьего элемента ИЛИ и счетным входом триггера контрольного разряда введен дополнительный элемент И, первый вход которого соединен со счетным входом дополнительного триггера ошибки, а второй- вход - с управляющим входом устройства.

Источники информации, принятые- во внимание при экспертизе

1. Авторское свидетельство СССР , № 362301, кл.С 06 F 11/10, 1970.

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| ВСЕСОЮЗНАЯ ' ййТ?йТйО«т:11:;Г'е"ндп | 1973 |

|

SU362301A1 |

| Устройство для контроля двухтактного двоичного счетчика | 1975 |

|

SU607221A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Устройство цифрового интегрирования | 1986 |

|

SU1345192A1 |

| Устройство для вычисления контрольного элемента и обнаружения ошибок | 1986 |

|

SU1325483A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

Авторы

Даты

1980-12-07—Публикация

1978-12-07—Подача