1

Предлом :е:Н,ный счетчик относится к области вычислительной техники и быть использован при построении устройств преобразования дискретной информации.

Известны счетчики с регенерацией информации, содержащие делители частоты, информационные выходы которых соединены со своими установочными входаими через элементы задержки, и дешифратор.

Недостаток из1вестных счетчиков состоит в том, что они не позволяют преобразовать записанный в них код с основанием два в код с другим основанием счисления.

Цель изобретения - расширение логических возможностей известных счетчиков с регенерацией информации.

Согласно изобретению в каждый разряд счетчика введены дополнительный элемент задержки и запоминающий трансформатор, выход каждого дополнительного элемента задержки подключен к установочной обмотке запоминающего трансформатора того же разряда, другая установочная обмотка которого подключена к счетному выходу делителя частоты данного разряда, счетный вход делителя частоты соединен со счетным выходом делителя частоты предыдущего разряда и со считывающей обмоткой запоминающего трансформатора давного разряда, выходная обмотка которого подключена ко входу донолнительного элемента задержки этого же разряда.

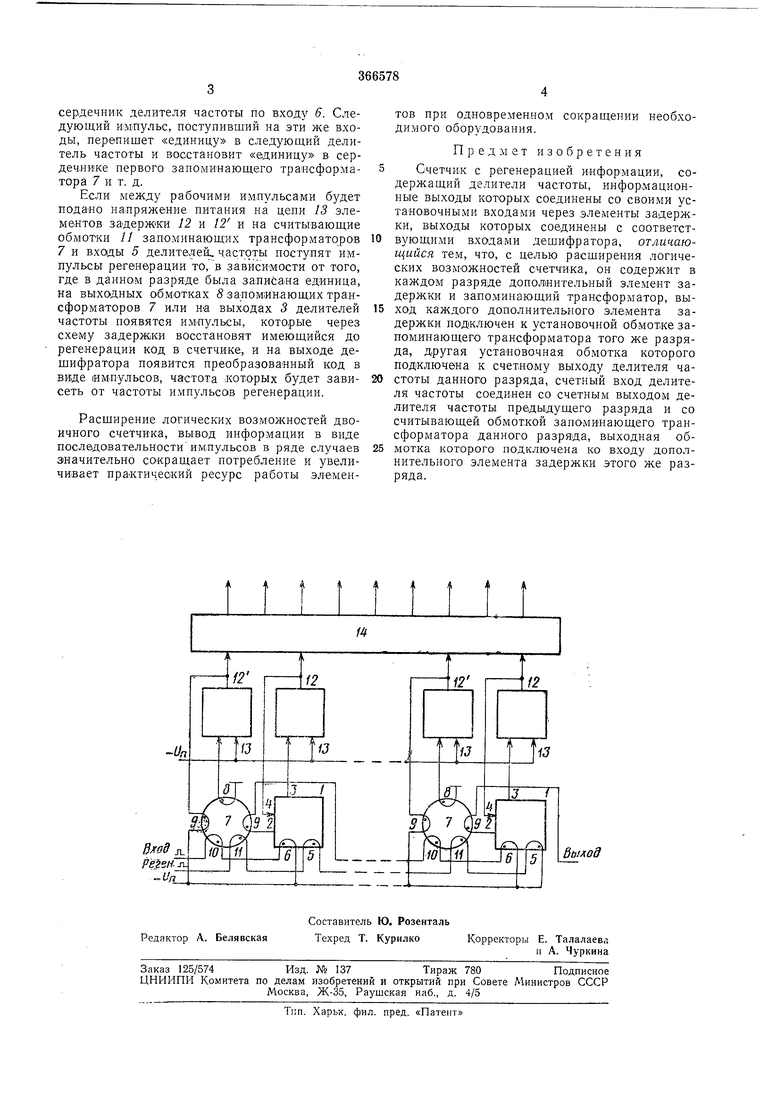

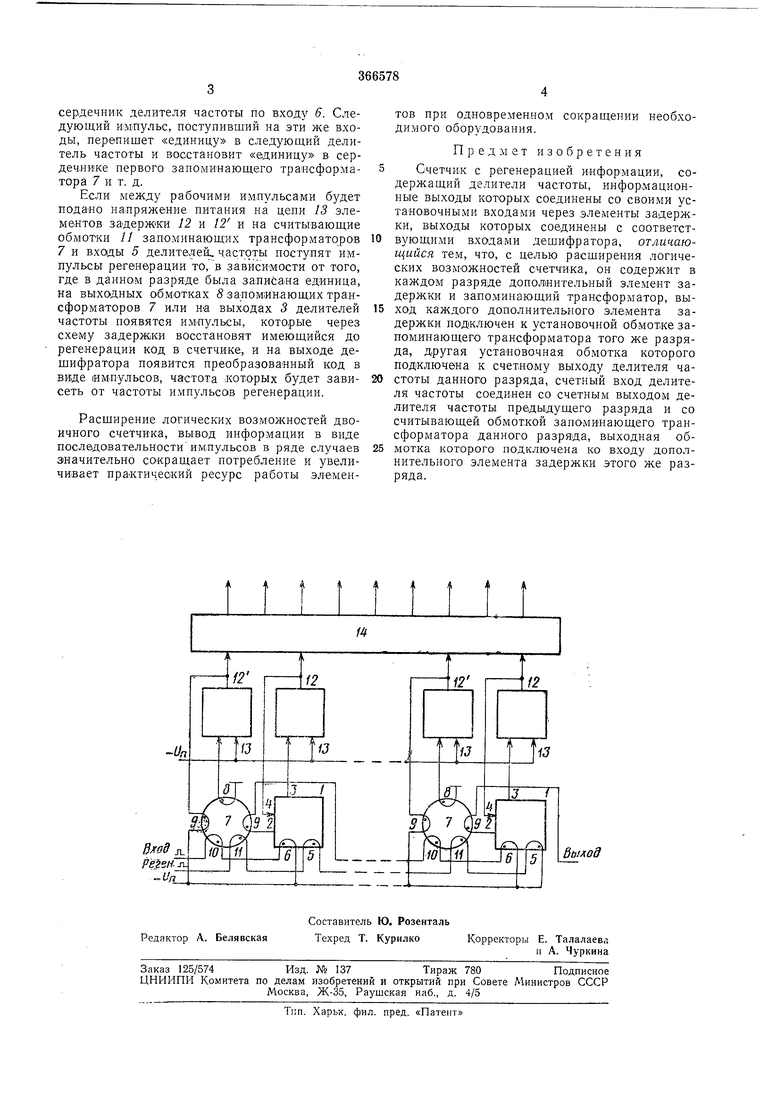

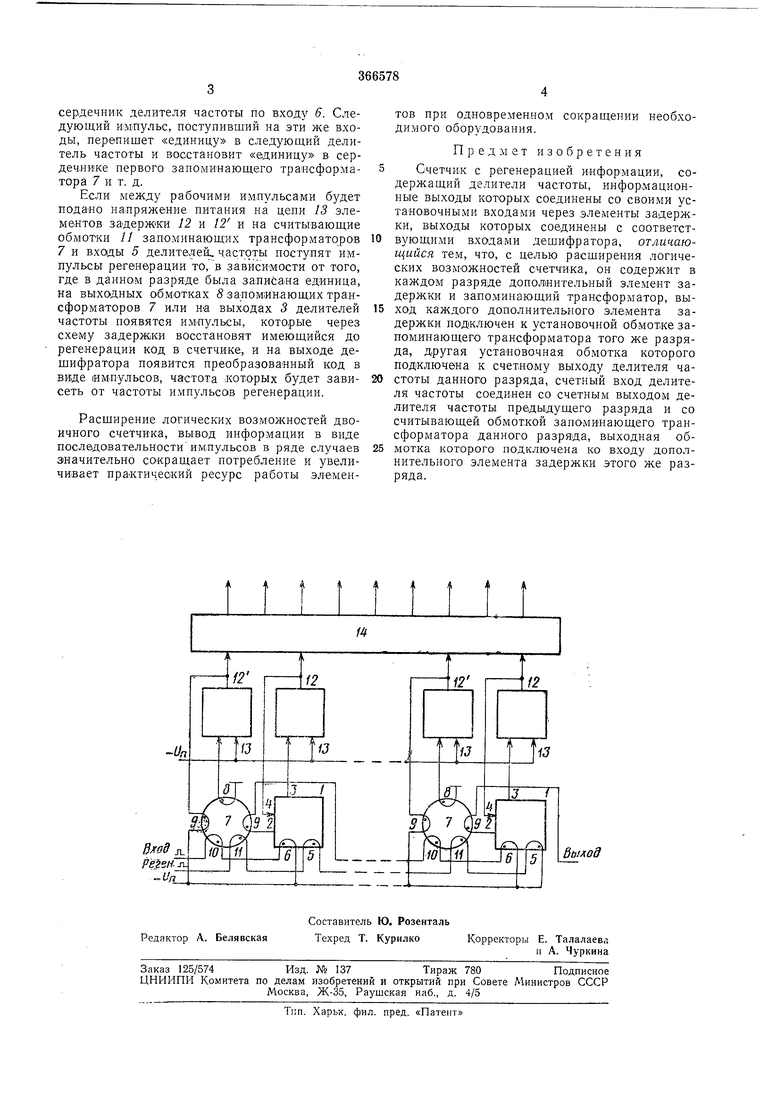

Принципиальная схема предложенного устройства изображена на чертеже. 5 Счетчик содерж 1т двоичные делители частоты / со счетным выходом 2 и информационным выходом 3, установочным входом 4, считывающим входом 5, со счетным входом 6, запоминающий трансформатор 7 с выходной 0 об.моткой 8, установочными обмотками 9 -и считывающими обмотками JO и 11, основной и дополнительный эле.менты задержки 12 и 12 с цепями питания 13 и дещифратор 14.

Работа предложенного устройства.

Питание элементов в исходном состоянии выключено. Информационные сердечники делителей частоты устанавливаются в состояние, соответствующее необходимой емкости счетчика, сердечник заноминающего трансформатора устанавливается в состояние, обратное состоянию информационного сердечника делителя частоты того же разряда.

Предположим, что в сердечник первого запоминающего трансформатора 7 была записана «единица, а в информационном сердечнике первого делителя частоты J - «нуль. Тогда импульс, постуливший на считывающую о5мотку 10 заиоминающего трансформатора 7, спищет «единицу из этого сердечника и запищет «единицу в информационный

сердечник делителя частоты по входу 6. Следующий импульс, поступивший на эти же входы, перепишет «единицу в следующий делитель частоты и восстановит «единицу в сердечниже первого запоминающего траисформатора 7 и т. д.

Если между рабочими импульсами будет подано напряжение питания на цепи 13 элементов задержки 12 и 12 и на считывающие обмотки 11 запоминающих трансформаторов 7 и входы 5 делителей., частоты поступят импульсы регенерации то, в зависимости от того, где в данном разряде была залисаиа единица, на выходных обмотках S запоминающих трансформаторов 7 или н-а выходах 3 делителей частоты появятся имлульсы, которые через схему задержки восстановят имеющийся до регенерации код в счетчике, и на выходе дешифратора появится преобразованный код в виде импульсов, частота которых будет зависеть от частоты импульсов регенерации.

Расщирение логических возможностей двоичного счетчика, вывод информации в виде послбдавательности импульсов в ряде случаев значительно сокращает потребление и увеличивает праКтический ресурс работы элементов при одновременном сокращении необходимого оборудования.

Пред.мет изобретения

Очетчик с регенерацией информации, содержащий делители частоты, информационные выходы которых соединены со своими установочными входами через элементы задержки, выходы которых соединены с соответствующими входами дешифратора, отличающийся тем, что, с целью расширения логических возможностей счетчика, он содержит в каждом разряде дополнительный элемент задержки и запо.минающий трансформатор, выход каждого дополнительного эле.мента задержки подключен к установочной обмотке запоминающего трансформатора того же разряда, другая установочная об.мотка которого подключена к счетному выходу делителя частоты данного разряда, счетный вход делителя частоты соединен со счетным выходом делителя частоты предыдущего разряда и со считывающей обмоткой запоминающего трансформатора данного разряда, выходная обмотка которого подключена ко входу дополнительного элемента задержки этого же разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Многоканальный таймер | 1979 |

|

SU813737A1 |

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Устройство для экстремальной фильтрации | 1987 |

|

SU1425651A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1001098A1 |

| Устройство для формирования кодовых последовательностей | 1983 |

|

SU1231584A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1406736A1 |

Авторы

Даты

1973-01-01—Публикация