Предлагаемый дискретный нуль-оргай Предназначен для использования в реверсивных следящих системах дискретного типа, Например , в Дискретизованных системах реверсивного следящего электропривода.

Известны дискретные нуль-органы для следящиХ систем дискретного , содержащие блок фазовой ориентации импульсов, блок коммутации ориентированных и)мпульсов и счетно-преобразовательный блок.

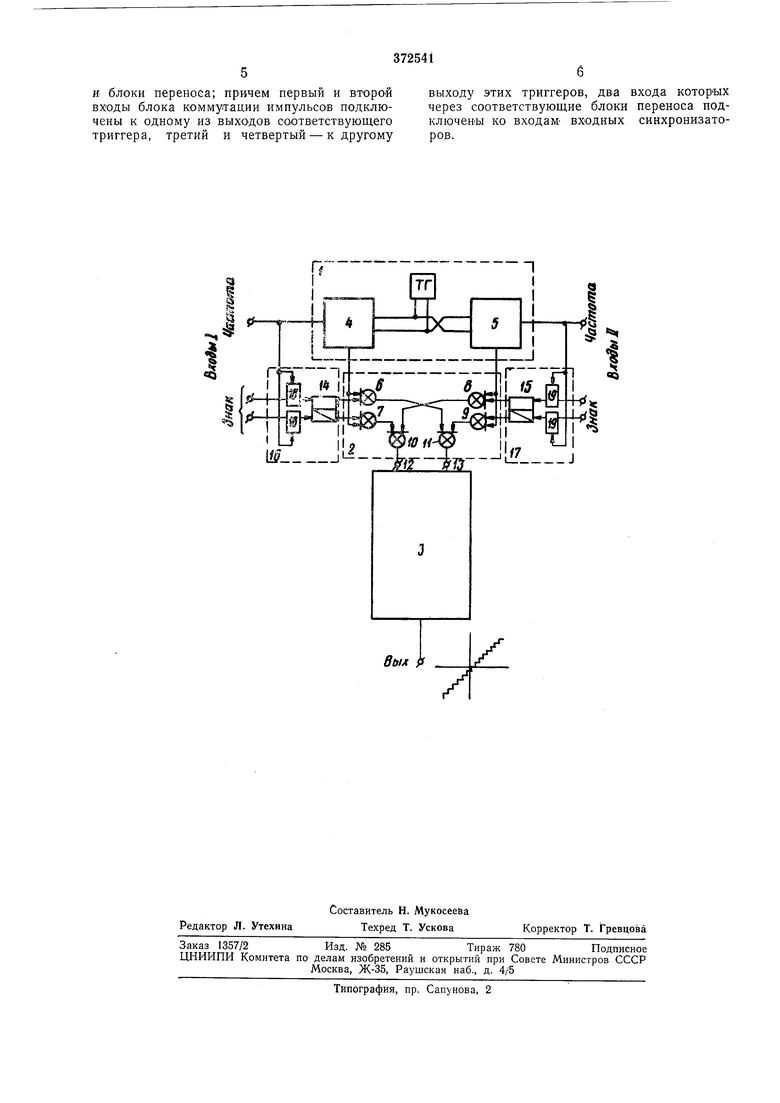

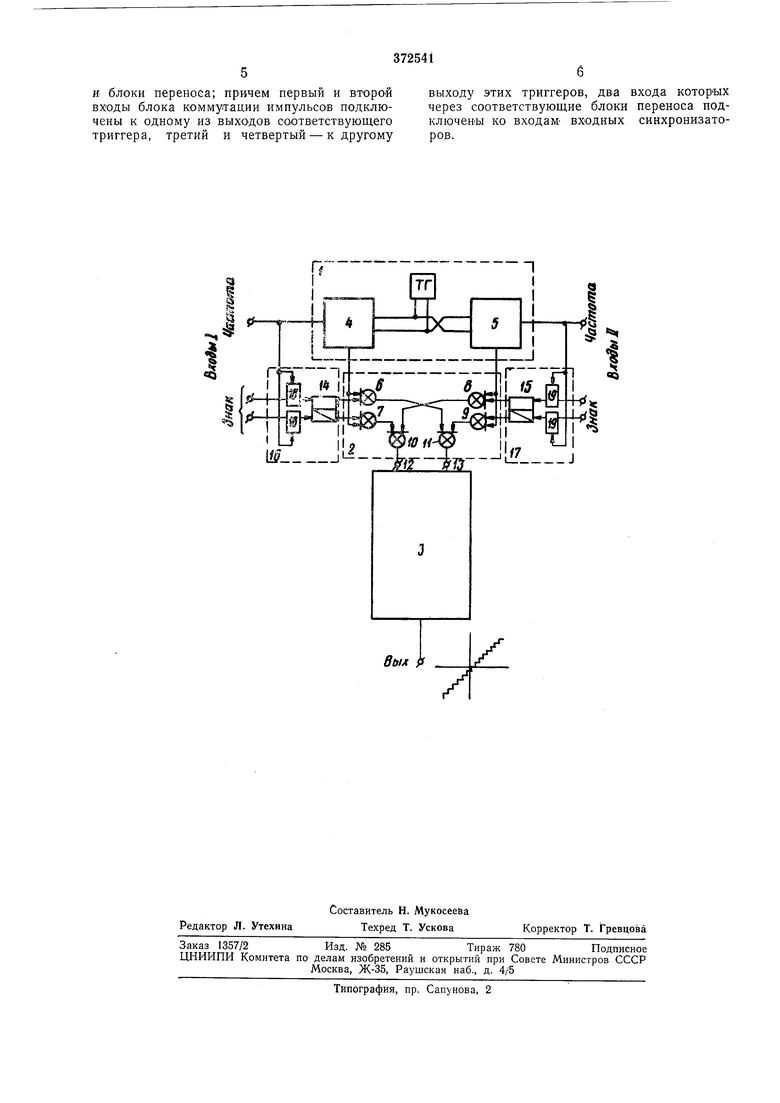

Предложенный нуль-орган отличается тем, что он содержит триггеры и блоки; переноса. Причем первый и второй входы блока коммутации- импульсов подключены к одному из выходов соответствующего триггера, третий и четвертый - к другому выходу этик триггеров, два входа которых через соответствующие блоки переноса подключены ко входам входных синхронизаторов. Это повышает точность рЗЙоты устройства. На чертеже изображена функциюнальная схем.а нуль-органа.

Нуль-орган содержит включенные функционально последовательно блок / фазовой ориентации импульсов, блок 2 коммутации импульсов, счетно-преобразовательный блок 3, выдающий в следящую систему сигнал рассогласования соответственно разности чисел импульсов и знакам задания и отработки.

Блок фазовой ориентации импульсов задания и отработки состоит из входных синхронизаторов 4 и 5, управляемых в противофазе тактовым генератором ГГ.

Выходы синхронизаторов 4 и 5 подключены ко входам бесконтактных переключателей, выполненных на логических ячейках 6-9, например «ИЛИ-НЕ. Разноименные выходы двухпОЗИционных переключателей попарно логически запараллелены посредством ячеек 10 -и 11 «ИЛИ-НЕ и подключены к суммирующему 12 и вычитающему IS входам блока 5.

Вторые выходы логических ячеек б-9 «ИЛИ-НЕ, кото.рые являются управляющими) входами двухпозиционных переключателей, подключены к выходам триггеров 14 и 15, буфферных ячеек 16 и 17 памяти. Входы переноса ячеек 16 и 17 подключены соответственно ко входам синхронизаторов 4 и 5 блока /.

Предлагаемый дискретный нуль-орган р аботает следующим образом.

Входные импульсы серий задания и отработки поступают ва входы синхронизаторов и 5 в проиввольной фазовой ориентации. На выходах этих синхронизаторов импульсы появляются с некоторым запозданием в моменты времени, соответствующие моментам 3 времени появления сдвинутых импульсов тактового генератора. Так как импульсы тактового генератора, подаваемые на соответствующие входы си«хронизаторов 4 н- 5, сдвинуты по фазе еле-5 дованин н-а 180°, импульсы задания и отработки, появляющиеся на выходах синхронизаторов, оказываются разнесенными во времени на величину, кратную половине периода частоты тактового генератора. Этим10 достигается безошибочный учет импульсов задания и отработки в блоке 3. Допустим, что в исходном состоян-ии напряжен.ие выходах синхронизаторов 4 и 5 соответствует напряжению логической еди-15 вицы логическИХ ячеек. Выходному имлульсу соответствует исчезновение напряжения на выходах преобразователей, т. е. появление логического, нуля. Логическая единица, поступающая с выхода синхронизатора 4 или20 с выхода синхронизатора 5 исключает логические единицы на выходах ячеек 6, 7 или 8, 9 «ИЛИ-НЕ. При этом существуют логические едийицы на выходах ячеек 10 ц И «ИЛИ-НЕ, подключенных ко входам 12 и25 13 блока 3. Если на выходе синхронизатора, например 4, появляется импульс, то на выходе ячейки 7«ИЛИ-НЕ, на второй вход которой поступает логический нуль с выхода триггера30 14, появляется логическая единица. Последняя исключает логическую единицу на выходе ячейки 10 «ИЛИ-НЕ, связанной с входом 12 блока. При этом в блоке 3 запесывается один импульс рассогласования со35 знаком «плюс. После появления импульса Hia входе синхронизатора 5 появляется импульс ва его выходе. Аналогично появляется логическая единица на выходе ячейки 9 «ИЛИ-НЕ, исключающая логическую еди-40 ницу на выходе ячейки // «ИЛИ-НЕ, и на вход 13 блока 3 поступает и-мпульс со знаком «минус, уменьш.ающий рассогласование на один импульс. Инвертирование сигнала знаков задания и45 отработки может производиться в произвольный м.омент времени относительно периодов следования иМПульсов задания и отработки. Пусть в некоторый момент времени знак50 задания инвертируется на противоположный. 8этот момент меняются местами логические нуль и единица на «входах I - знак. Одн,ако триггер 14 пока остается в прежнем состоянии, так как блоки переноса 18 запре-55 щают его опрокидывание. Первый импульс задания, поступающий после смены знака на вход синхронизатора 4, запоминается в нем и, кроме того, воздействует на управляющие входы блоков пере-60 носа 18, являющиеся входом переноса буфферной ячейки паМЯти 16. В этот момент на входы триггера 14 поступают инвертированные логи1ческий нуль и логическая единица и переводят триггер 14 в противополол ное65 4 состояние. Через некоторое время тактовый генератор 6 подвигает «записанный в синхронизатор 4 импульс на выход, который с учетом нового состояния триггера 14 через логические ячейки 6 и 11 «ИЛИ-НЕ «записывается на вход J3 блока 5. Дальнейшими импульсами серии задания рассогласование в данном случае быстро уменьшается до нуля, а затем возрастает, определяя в следящей системе сигнал рассогласования с противоположным знаком, С некоторым запаздыванием относительно времени, смены знака задания исполнителькое звено следящей системны изменяет знак отработки:. При этом на «входа.х И - зоак происходит инвертирование логических нуля и единицы. Аналогично описанному первый импульс, поступающий на «вход II - частота, воздействуя на управляющие входы блоков переноса 19, об51славли/вает переход триггера 15 в противоположное состояние, Появивщись на выходе синхронизатора 5 с некоторым запозданием, данный импульс с учетом нового состояния триггера 15 через ячейки 8 к 10 «ИЛИ-НЕ поступает Hia вход 12 блока 3, уменьшая в нем число ЕМпульсов рассогласования. Вследствие временной задержки прохождения импульса через синхронизаторы 4 к 5 попадание логических единиц на их выходах (на первых входах ячеек 6 и 7, а тажже, в равной степени, и па первых входах ячеек 8 и 5) происходит при состояниях триггеров 14 и 15, соответствующие знакам задания и отработки, существовавшим в моменты времени поступления данных импульсов задания и отработки на входы синхронизаторов 4 и 5. Следовательно, ориентированные по фазе импульсы задания и отра ботки, з апаздывающие во времени, безошибочно коммутируются на суммирующий 12 (вычитающий) или вычИТающий 13 (суммирующий) входы блока 5 в соответствии с истинными- знаками задания и отработки.. Изменение знакюв задания и отработки, в течение времени задержки имиульсОВ в синхронизагорах 4 w 5 благодаря ячейкам 16 и 17, входы блоков переноса которых связаны со входами синхрониваторов, не может вызвать ложного переключения входов 12 и 13 блока 3, так как триггеры 14 и: 15 находятся В прежнем состоянии до появления следуЮЩих входных импульсов, поступающих на входы синхрон заторов после учета предыдущих импульсов блока 5. Предмет изобретения Дискретный нуль-орган, содержащий два входных синхронизатора, соединенных с тактовым генератором, выходы которых через блок коммутации импульсов соединены со счетно-преобразовательным блоком, отличающийся тем, что, с целью повышения точности работы устройства, оно содержит триггеры

и блоки переноса; причем первый и второй входы блока коммутации импульсов подключены к одному из выходов соответствующего триггера, третий и четвертый - к другому

выходу этих триггеров, два входа которых через соответствующие блоки переноса подключены ко входам входных синхронизаторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Следящая система | 1982 |

|

SU1081622A1 |

| Следящая система | 1975 |

|

SU585474A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| ЦИФРОВАЯ СЛЕДЯЩАЯ СИСТЕМА | 1967 |

|

SU203033A1 |

| Число-импульсный следящий электропривод | 1983 |

|

SU1124256A1 |

| Устройство для программного управления технологическим оборудованием | 1986 |

|

SU1372277A1 |

| Устройство для автоматической центрировки линз | 1982 |

|

SU1118882A1 |

| Система передачи и приема дискретной информации | 1983 |

|

SU1119184A1 |

| Устройство для управления многофазным импульсным регулятором | 1981 |

|

SU957411A1 |

| Задающее устройство следящего электропривода | 1982 |

|

SU1056129A1 |

1 ---WJ

/L

вш

/1

Авторы

Даты

1973-01-01—Публикация