Изобретение относится к технике и предназначено для иреобразовання двоичных кодов в «оды системы остаточных классов (СОК)

Известно устройство для преобразования кодов из любой поэйциоиной Системы «мсленйя (в том числе а нз двоичной) в коды СОК, содержащее входные регистры, блоки суммирования, блоки двоичного кодирована и дешифраторы.

Предлагаемое устройство отличается от известного тем , что выход предпоследнего старшего разряда входного регистра соединен через корректирующий матричный сумматор с матричной схемой умножения промежуточного результата, выходы которой связаны с входами выходного сумматора И корректирующего матричного суниатора, вход которого подключен через матричную схему умиожеиия старшего разряда к выходу последнего старшего разряда входного регистра, выход младшего разряда которого соединен с входом выходного сумматора.

Это позволяет упростить схему устройства.

Устройство использует следующий принцип работы.

Любое {/C-f 7) - значное двоичное число может быть представлено в виде

X - -1- Лй, + ... -f ,2 + 02°.

Иначе можно заз1б са с.t (... Йй2-f )2 + ArU) 2-f ... 4-А) 2-f -f Е Al (fflod /,| :: «(mod Я/), есля

( -|-.4s-02s:A CmedP); №|ш od P/-f -2) 2 Xs..i (mod Pj);

(X (mod P) + ,) 2 -- A a 4i..u r-,,

As(modP) -f Л - , (mod ) «y(mo4 Pyb

T. e. значение чксла X в системе остаточных

классов по mod Pj образуется умножением старшего разряда иа величину основания 2, потом суммнроааннем по соответствующему модулю Pj полученного результата со зкачениеи следувощего разряда, затем умножением

иоиученного . результата на основание 2 по sirodPf. Так операции умножения и суммировашш по mod PJ производятся до тех пор. пока при суммировании не будет добавлено значение младшего разряда.

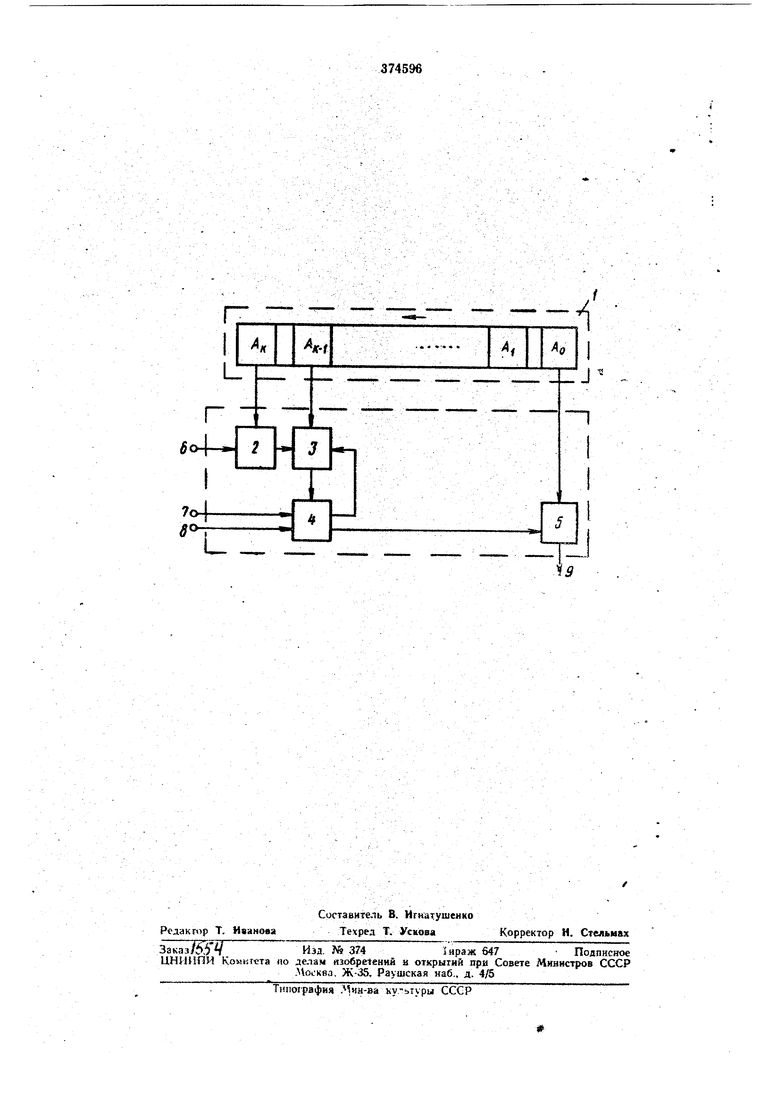

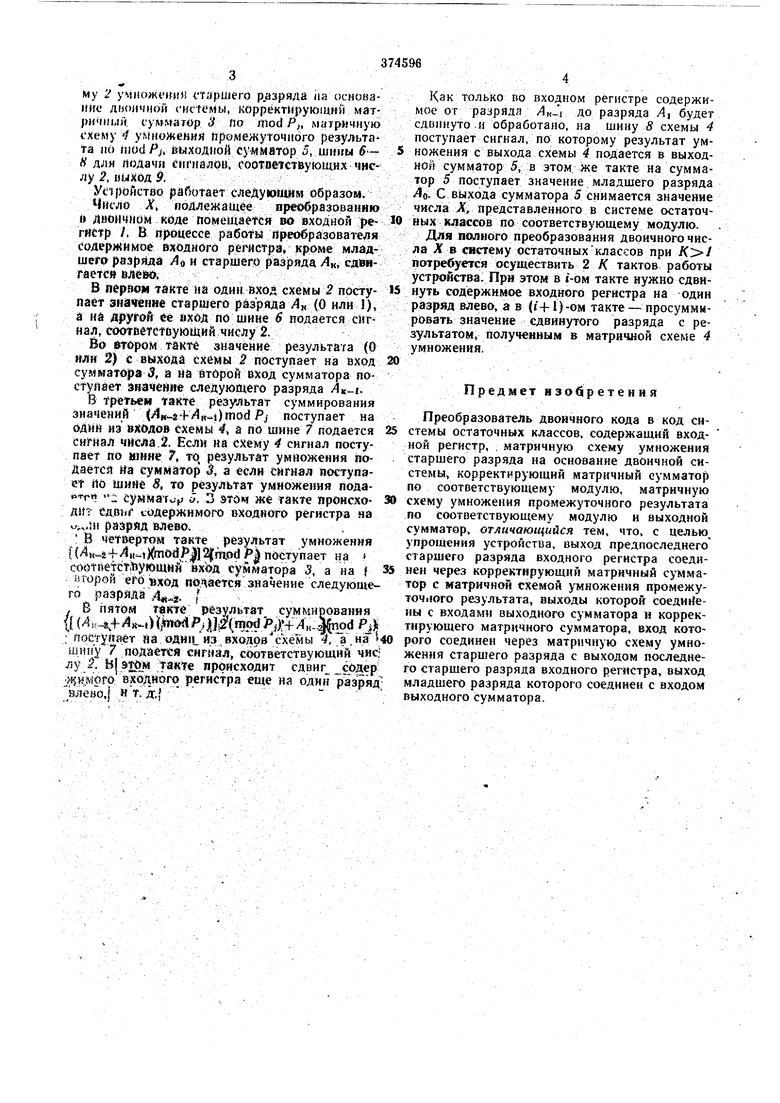

На чертеже изображена схема предлагаемого устройства для преобразования двоичного числа по одному модулю.

Устройство содержит входной регистр / для записи разрядов Ло- Лк и сдвига раарялоо

/li ... Л,-( двоичного числа, матричную схсMy I умножения старшего р.азряда iia основаififc дооичной fHcttMbi, коррёктирующнй матричный cyMNfaTOp 3 по fnodPj, матричную схему / умножения промежуточибго результа та по fiiod Я;, выходной су-мматор 5, шииы «для «одачн енгналов,1 оотве«1Вую1цих числу 2, иыход ytipOHCtao работает следующ)Ци образом. Число X, помежащее преобразованию 11 ДйОИ4 ом коде noMeuiaetc во входной j)eгметр /, В tipQuecce pa6otw йреобразователя еодери имое аходйого регистра, кроме младшег разряд АО и старшего разряда у4к, едвиfaetc , : , / ..,;, В Первом тйктё на один йход схемы i постуns r старшего разряда к (О млн Г), а Ни Другой её вход по шине 6 подается сйг нал, соответстеуюший числу 2. Во втором tSKte значение результата (О млн 2) г выхода схемы 2 поступает на вход сумматора i3, а Ма йтОрой вход сумматора поctyfiaet зна 1е}1Иб следующего разряда 8 fpeti eM такте результат суммирования значений (Ли-г-Мй-Оп ой J поступает на один нз входов схемы, а по шине 7 подается сигнал числа.2, Если на схему 4 сигнал поступает по шине , то/результат умножения по Дается а сумматор J, а если сигнал йоступаат iio шийе 5, to результат умиоження подаi: Tj4« ,.-. eyj Matvif; J, 3 ttOM же такте происход|1 сдвиг л;одержимого входного регистра яа ч/,лЛн рааряд влево В четвертом такте результат умножения l(4,,-b,,: tXmodPj|l iifiod/| поступает на сойшетстй ющнй 8хЬд суммато|ра 3, а на } йторби его вход подается значение следующего разряда 4i-z. , , В ПЯТОЙ реаультат суммироваиня (I ()()): ; ooctyftaer йаоди1 ИЗ ВХОДОВЧхёмы 4, а.н;вГ шину 7 подается сигйал, соответствующий чис л у 5. В| эшм такт происходит едвиг сод,ер .;fi }i tO№&xo iH6ro регистра еще ня оди|7 зряд влево, д-.Г Как только по входном регистре содержимое от разряда до разряда AI будет сдвинуто-н обработано, на шину 5 схемы 4 поступает сигнал, по которому результат умножения с выхода схемы подается в выходной сумматор 5, в этом, же такте на сумматор 5 поступает значение младшего разряда 0- С выхода сумматора 5 снимается значение числа Л, представленного в системе остаточных классов по соответствующему модулю. Для полного преобразования двоичного числа Л в систему остаточныхклассов при потребуется осуществить 2 К тактов работы устройства: При этом в I-OM такте нужно сдвинуть содержимое входного регистра на один разряд влево, а в (t+ 1)-ом такте - просуммировать значение сдвинутого разряда с результатом, полученным в матричной схеме 4 умножения. Предмет изобретения Преобразователь двоичного кода в код системы остаточных классов, содержащий входной регистр, матричную схему умножения старшего разряда на основание двончной системы, корректирующий матричный сумматор по соответствующему модулю, матричную схему умножения промежуточного результата по соответствующему модулю и выходной сумматор, отличающийся тем. что, с целью, упрощения устройства, выход предпоследнего старшего разряда входного регистра соединен через корректирующий матричный сумматор с матричной схемой умножения промежуточного результата, выходы которой соедийеиы с входами выходного сумматора и корректирующего матричного сумматора, вход которого соединен через матричную схему умножения старшего разряда с выходом последнего старщего разряда входного регистра, выход младшего разряда которого соединен с входом выходного сумматора.

rz

г tfo4-

r J

-::i;ii:1

j

-,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в код системы остаточных классов | 1974 |

|

SU525947A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU983701A1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1981 |

|

SU1001079A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для вычисления сумм парных произведений в полиномиальной системе классов вычетов | 2016 |

|

RU2622881C1 |

| Генератор систем базисных функций Аристова | 1988 |

|

SU1599850A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

7o 6°L

Авторы

Даты

1973-01-01—Публикация