1

Изобретение относится к системам цифровой связи.

Известно устройство фазирования параллельно-|Последо|Вательно преобразователя, содержащее подключенные к входнмм клемма.м схему фа13ирования и схему стробирования, к вьгходам которой подключены последовательно; соеди1ненные триггеры задержки, формирователи дифференциалов зад|них фронтов,, накопительный регистр и регистр сдвига, а также источник и.мпульсов проводного тракта, к одному из выходов которого последо-вательно подключены схема выделения .вого интервала радиока/нала и фазовьш дискрими.натор, присоединенный одним из входов к выходам формирователей дифференциалов заднИХ фронтов.

Однако известное устройство имеет низкую точность установ.ки задержки и Hie запоминает .величины задерЖКи при перерывах сигнала, что особеино важлю в условиях KB ра Д|Иок,анала, когда после Замирания сигнала фазовое положение импульсов радиоканала ДОЛЖ1НО уста,навлива. в то же самое место, что и ДО| заМИрания.

Предложенное устройство отличается, тем, что оно содержит дииамический триггер и последовательно включеилые триггер управле1гия, счетчик, схему задания иа.чальных условий и реверсивный счетчик, входы сложения и вычитания которого сосдине.ны с выходами фазового дискриминатора, один из вхог дов схемы задания начальных условий подключен к схемы фазирО1ва:Н1ИЯ № соединен с единичным входом триггера управления, входом схемы стробированйя и входом за.пуска ди.намического триггера, вход останоВКИ которого подключен к вьисоду триггера управления, а выход соединен со входом тактовых импульсо.в счетчика, присоедиНенного выходом к нулевым входам триггера унра.вления и триггеров задерл ки.

Это позволяет повысить помехоустойчивость.

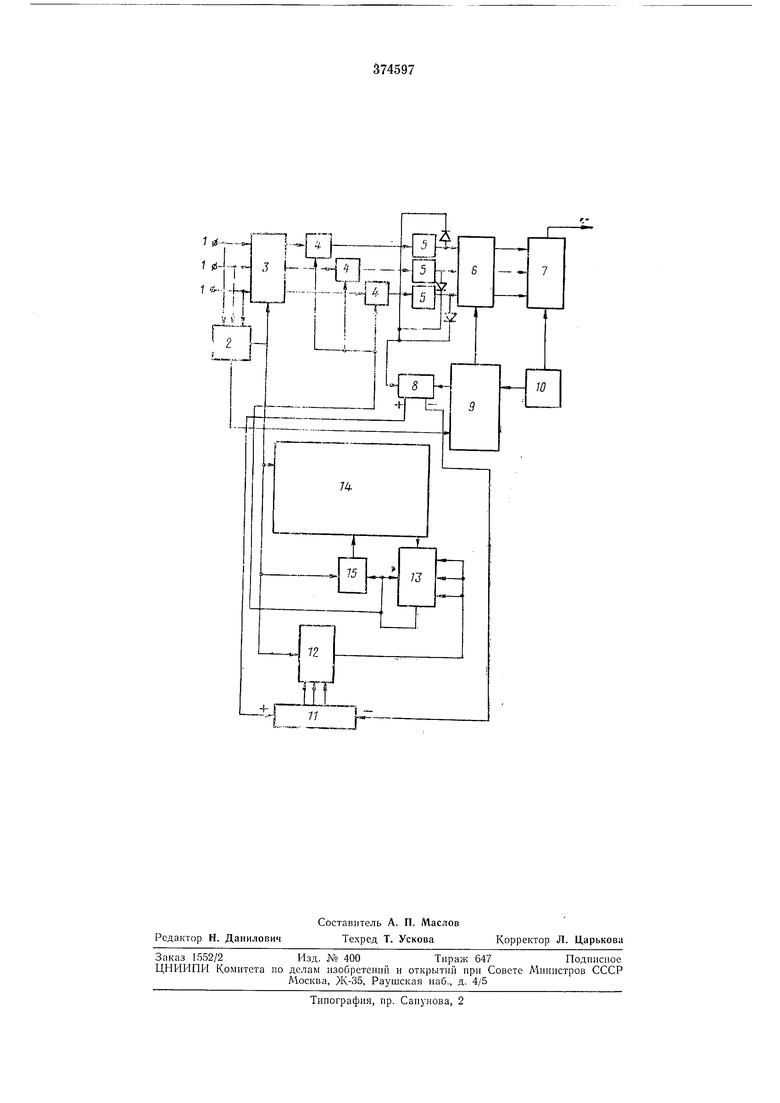

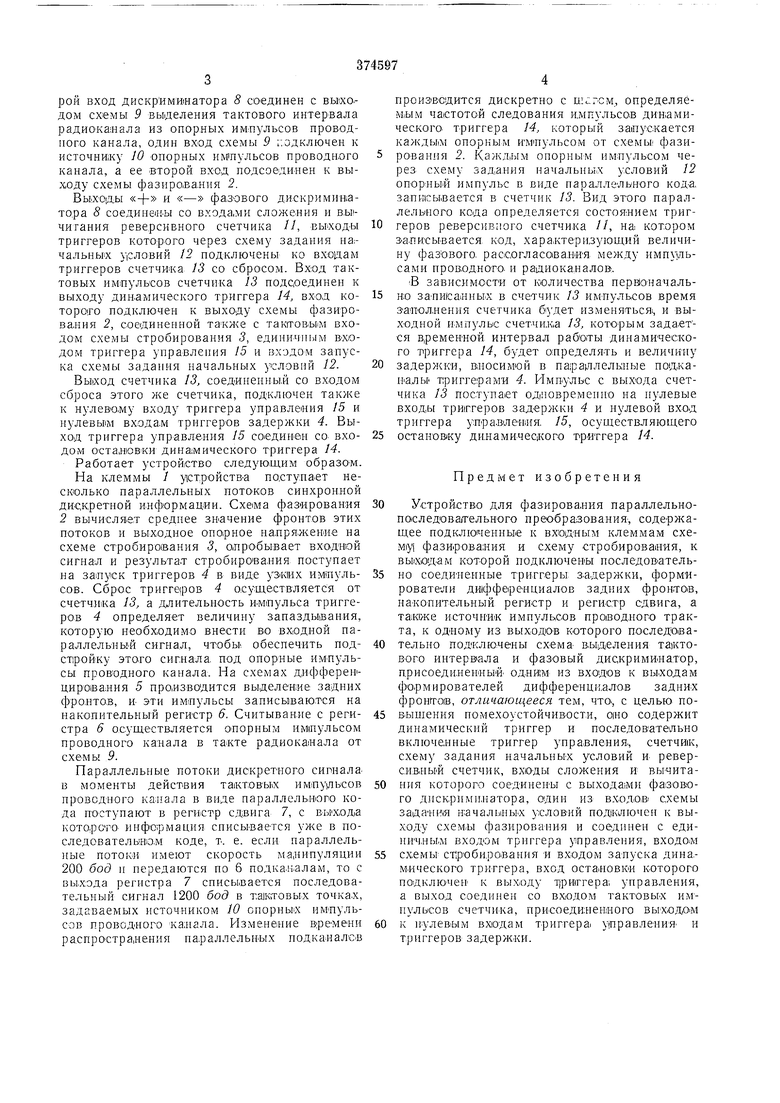

Иа чертеже приведена блок-схема устройства.

Предлагаемое устройство содержит входные клеммы / параллельных подкан.алов радиотракта, подключенные параллельно ко входам схем фазирования парашлельны,х подканалов 2 и стробирования 3. Параллельные выходы схемы стробирования 3 соединены с единичными входами триггеров задержки 4, выходы которых через формирователи дифференциалов заднего фронгга 5 подключены к информационнЫМ входам напчопительного регистра. 6, .подсоединенного к информацио.нным входам регистра сдвига 7. Информацио.нные входы регистра 6 подсоединены: к одному входу фазового дискриминатора S, второй вход дискриминатора 8 со-единен с вьихо.дом сх1емы 9 выделения тактового интервала радиоканала из опорных имлульсов проводного канала, один вход схемы 9 ;:одключе.н к источнику 10 опорных импульсов проводн.ого канала, а ее второй вход подсоединен к вых,оду схемы фазирО|Ва.ния 2.

Вы 0|Д;Ы «4- и «- фазового ди.скримивато.ра 8 соедннеШЫ со входа.ми сложения и върчигания реверсивного счетчика 1J, триггеров которого через схему задания на:чальных условий 12 подключены ко входам триггеров счетчИКа 13 со сбросом. Вход тактовых имюульсов счетчика 13 подсоединен к выходу динамического триггера 14, вход которого подключен к выходу схемы фазирования 2, соединенной также с таютовъил входом схемы стробирования 5, единичным в одом триггера управления 15 и ЕЗХЭДОМ запуска схемы задания начальных условий 12.

Выйод счетчика 13, соединенный со входом сброса этого же счетчика, подключен также к нулевому входу триггера управления 15 и нулевы1м входам триггеров задержки 4. Выход триггера управления 15 соединен со входом останювки динамического триггера 14.

Работает устройство следующим образом.

На клеммы / у1ст;ройств-а no.cTynaieT нескюлько параллельных потоков синхронной дИСкретной информации. Схема фазирования 2 вычисляет среднее зн ачение фронтов этих потоков и выходное onoipHoe напряжение на схеме стробирования 5, олрОбьшает входной сигнал и результат стробирования поступает на зануск триггеров 4 в виде узких импульсов. Сброс триггефов 4 осуществляется от счетчика 13, а длительность импульса триггеров 4 определяет величину запаздывания, которую необходимо внести во входной параллельньш сигнал, чтобьь обеспечить подстройку этого сигнала под опорные иМПульсы проводного канала. На схемах дифференцирования 5 производится выделение задних фронтов. И эти имиульсы записываются на накопительный регистр 6. Считывание с регистра 6 осуществляется опорным имтульсом проводного канала в такте радиоканала от схемы 9.

Параллельные потоки дискретного сигнала в моменты действия тактовъж импульсов проводного канала в виде параллельного кода поступают в регистр сдвига 7, с выХ,оД|а кото,рото информация списывается уже в последовательгаом коде, т. е. если параллельные потоки имеют скорость манипуляции 200 бод и передаются по 6 подкан.алам, то с вы.хода регистра 7 списывается последовательный сигнал 1200 бод в тактовых точках, задаваемых источником 10 опорныХ импульсов проводного ка:нала. Измене1ние времени распространения нараллельнъгх подканалс-в

производится дискретно с шггсм, определяеMibiM частотой следования импульсов динамического триггера 14, который запускается каждЫ|М опорным иМпульсом от схемьи фазирования 2. КажД|)Гм опорным импульсом через схему задания начальных условий 12 опорный импульс в виде параллельного кода записывается в счетчик 13. Вид этого параллельного кеда определяется состоянием триггеров реверсивного счетчика //, на котором За.писывается код, характеризующий величину фазового. рассогласо1ваБ«Я между импульсами нроводного. и радиоканалов. В зависимости от количества первюначально заПИСаниЫХ в счетчик 13 импульсов время Заатолнеиня счетчика будет измеияться1, и выходной импульс счетчи.ка 13, которым задается временной интервал работы динамического триггера 14, будет онределять и величину

задержки, вносимой в па;ра1ллель;ные подкаНалы триггерами 4. Импульс с выхода счетчика 13 поступает одновременно на нулевые входы триггеров задержки 4 и нулевой вход триггера Зиравяен1ия. 15, осуществляющего

останов1ку динамичеокого триггера 14.

Предмет изобретения

Устройство для фазирования параллельнопоследова|Тельного преобразования, содержащее подключенные к входным клеммам схеМ1 1 фазирования и схему стробировайия, к вы1. которой подключевы последовательно соединенные триггеры з.адержки, формирователи дифференциалов задних фронтов, накопительный регистр и регистр сдвига, а та:к1же источник импульсов проводного тракта, к одному из выходов которого последоеательно подключены схема выделения тажтового интерв1ала и фазовый дискриминатор, присоединенный одним из входов к выходам формирователей дифференциалов задних фронггов, отличающееся тем, что, с целью поВЫшения номехоустойчивости, оно содержит динамический триггер и последовательно включенные триггер управления., счетчИ1К, схему задания начальньгх условий и реверCHBiHbm счетчик, входы сложения и вычитання которого соединенЫ с выхода1ми фазового дискриминатора, одии из входов схемы задани1Я н:ачальны.х условий нод|ключен к выходу схемы фазирования и соединен с единич.иым входом триггера управления, входо.м

схемы стробирования и входом запуска динамического триггера, вход остановки которого подключен к выХ|Оду TjpHirrepai управления, а выход соединен со вх-одом тактовы.х имнульсов счетчика, присоеди:ненного выходом

к нллев1ым входам триггера1 управления- и триггеров задержки.

.-..-.

j -H -...,... I l nIjiJTp

I:Ii

у i

Г--1-Jl..«l ; U

.UJJ-ij

ufJl

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗИРОВАНИЯ И РЕГЕНЕРАЦИИ ДЛЯ ТРАНСФОРМАТОРА СКОРОСТИ ДИСКРЕТНЫХ СИГНАЛОВ | 1971 |

|

SU321962A1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2011 |

|

RU2485665C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство цифровой фазовой автоподстройки частоты | 1990 |

|

SU1732466A1 |

| Цифровой частотный дискриминатор | 1982 |

|

SU1131036A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ФАЗИРОВАНИЯ | 1967 |

|

SU224563A1 |

| Устройство для программного управления положением вала электродвигателя | 1977 |

|

SU708310A1 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

L-ч:

77

..-.„T

Авторы

Даты

1973-01-01—Публикация