1

Изобретение относится к области вычислительной техники и может быть использовано для проверки запоминающих устройств ЦВМ.

Известно устройство для проверки ферритовых матриц, содержащее блок управления, соединенный с блоками регистра адреса, дешифраторов, усилителей считывания -и блоком контроля, и генераторы импульсов тока, входы которых подключены к соответствующим выходам блока управления. При использовании этого устройства область хранения информации определяется с помощью плавного изменения амплитуды импульсов тока.

Недостатками известного устройства являются низкая точность определения амплитуды импульсов тока и трудность автоматизации режима проверки ферритовых матриц.

Целью изобретения является автоматизация режима проверки ферритовых матриц.

Поставленная цель достигается путем того, что предложенное устройство содержггг в каждом генераторе импульсов тока Л оконечных каскадов с амплитудой импульсов, пропорциональной 2, где п - номер каскада («., 2,....,N), переключатели и имитаторы нагрузки. Выходы оконечных каскадов соединены с нервыми входами соответствующих переключателей, вторые входы которых подключены .к блоку управления. При этом первые ВЫХОДЫ переключателей соединены со

входом блока дешифраторов, а вторые - с имитаторами нагрузки.

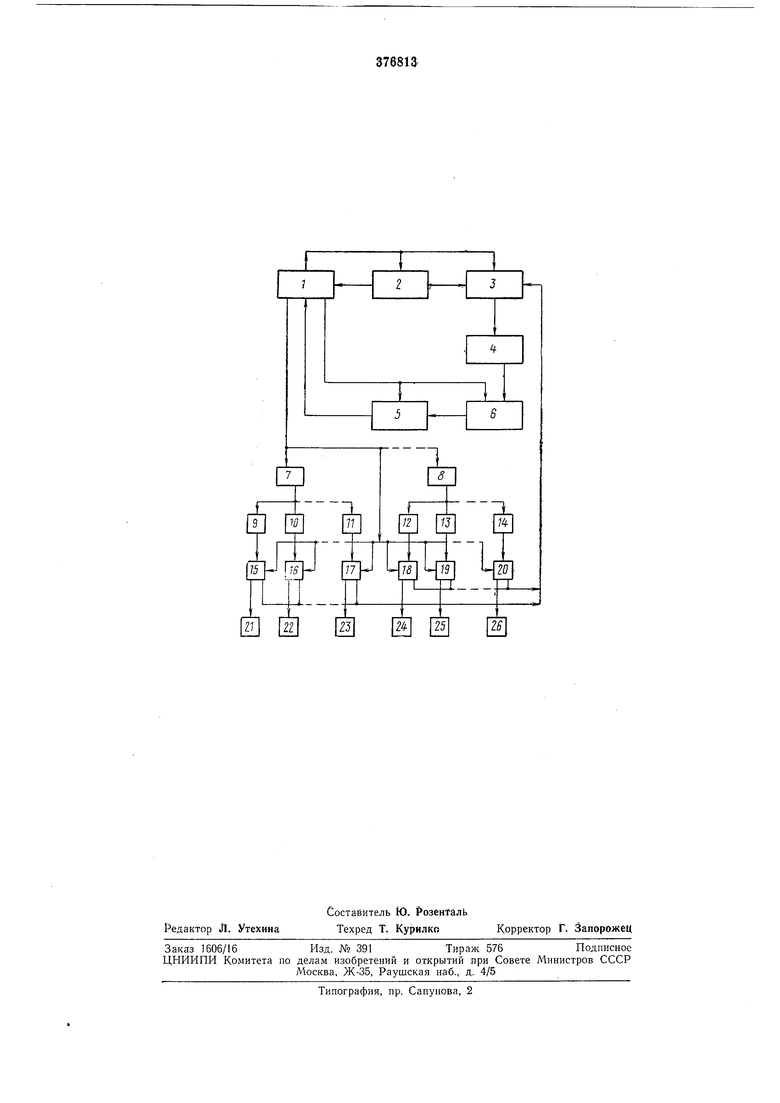

Блок-схема предложенного устройства изо бражена на чертеже.

Устройство содержит блок управления 1, блок регистра адреса 2, блок дешифраторов 3, проверяемую ферритовую матрицу 4, блок контроля 5, блок усилителей считывания 6, формирователи генераторов импульсов тока 7, 8, оконечные каскады генераторов импульсов тока 9-f-14, переключ.атели 15-н20 и имитаторы нагрузки 21-н26.

Блок управления / предназначен для выработки необходимых импульсов и потенциалов, управляющих работой остальных блоков. Блок 1 соединен с блоками 2, 3, 5, и 6, формирователями 7, 8 и вторыми входами переключателей .

Блок регистра адреса 2 предназначен для последовательного выбора обмоток проверяемой матрицы 4 и представляет собой ряд тирггеров, работающих в режиме счетчика.

Блок дешифраторов 3 предназначен для выбора соответствующей обмотки данной координаты матрицы 4. Проверяемая матрица 4 соединена с блоком усилителей считывания 6.

Блок контроля 5 предназначен для контроля соответствия записанной и считываемой

информации. Блок контроля 5 соединен с блоком 1..

Блок усилителей считывания 6 предназначен для усиления считанного сигнала и осуществления его амплитуднов|ременной селекции и соедин-ен с блоком 5.

Формирователи генераторов импульсов тока 7, 8 формируют передний и задний фронты и вершины -импульса при заданной длительности импулсьа. Выход формирователя 7 соединен со входами оконечньрх каскадов 9-11, а выход формирователя S -со входами оконечных каскадов 12-14.

Оконечные каскады 9-14 предназначены для генерир01вания стабилизированных импульсов тока, амплитуда импульсов которых пропорциональна 2, где п - номер каскада (, 2,....,N). Так-оковечные каскады 9 и 12 имеют номер 1 и генерируют импульсы с минимальной амплитудой (2 2), каскады 10 и 13 имеют номер 2 и генерируют импульсы с амплитудой, в два раза 1большей (2 4). Последние каскады 11 и 14 имеют номер N и генерируют импульсы с максимальной амплитудой (2). Число Л зависит от .необходимой точности, что определяет минимальную дискретность «а - величину амплитуды тока оконечных каскадов 9, 12, и максимальной величины амплитуды импульсов тока, которая равна сумме амплитуд всех каскадов

данного генератора тока (2 + 22 + ... + ). ,

Число генераторов тока (на чертеже условно показано два) определяется используемой системою выборки, например, в системе выборки 2,5Д их должно быть четыре и т. д.

Выходы оконеЧных каскадов Р-14 соединены с первыми входами переключателей 15-20, предназначенных для коммутации выходов оконечных каскадов 9-14, т. е. соединения их либо с соответствующими входами блока дбшфираторОБ S, либо с -имитаторами нагрузки. В качестве переключателей могут быть использованы реле. Первые выходы переключателей /5-17 объединены и соединены со входом блока дешифратора 5. Первые выходы переключателей 18-20 объединены и соединены с входом блока дещифраторов 3. Вторые выходы переключателей

соединены с -имитаторами нагрузки .

Имитаторы нагрузки предназначены для сохранения режима работы оконечных каскадов 9-г-14 при отключеиии их выходов от блока дешифраторов 3. Для сохранения режима работы формирователей импульсов 7, 8 входы око-неч«ых каскадов 9-14 присоединены к ним постоянно, поэтому для сохранения режима работы оконечных -каскадов 9-14 необходимо, чтобы и нагрузка этих каскадов также не менялась.

Устройство работает следующим образом.

При определения области хранения информации оператор с помощью набора элементов, управляющих работой переключателей , устанавл-И1вает граничные значения амп-литуд импульсов тока. При этом блок управления 1 подает управляю щие сигналы на вторые входы переключателей . Вьгбранные переключатели соединяют выходы соответствующих оконечных каскадов с входом блока дешифраторов 3, определяя тем самым амплитуду им-пульсов то-ка, которые подаются на ферритовые сердечники матрицы 4. Не выбранные переключатели соединяют выходы остальных оконечных каскадов с имитаторами нагрузки.

Предмет изобретен-и я

Устройство для проверки ферритовых матриц, содержащее блок управления, соединенный с блоками регистра адреса, дешифраторов, усилителей считывания и блоком контроля, и генераторы импульсов тока, входы которых подкл-ючены к соответствующ-им выходам блока управления, отличающееся тем, что, с целью автоматизации режима проверки матриц, оно содержит в каждом генераторе импульсов тока N оконечных каскадов с амплитудой импульсов, пропорциональной 2, тде п-номер каскада (п, 2,...,N), переключатели и имитаторы нагрузки; выходы оконечных каскадов соединены с первыми входами соответствук щих переключателей, вторые входы которых подключены к блоку управления; при этом первые выходы переключателей соединены со входом блока дешифраторов, а вторые выходы подключены к имитаторам нагрузки.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1981 |

|

SU963110A1 |

| Устройство для контроля матриц на ферритовых сердечниках | 1977 |

|

SU622177A1 |

| Устройство для контроля ферритовых матриц | 1975 |

|

SU736176A1 |

| Устройсто для проверки ферритовых матриц | 1974 |

|

SU548893A1 |

| Устройство для контроля элементовзАпОМиНАющЕй МАТРицы | 1979 |

|

SU824314A1 |

| УСТРОЙСТВО ДЛЯ ПРОВЕРКИ ФЕРРИТОВЫХ МАТРИЦ ОПЕРАТИВНЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1973 |

|

SU364030A1 |

| ИМИТАТОР ИСТОЧНИКОВ РАДИОСИГНАЛОВ | 1994 |

|

RU2094915C1 |

| Устройство для контроля матриц на ферритовых сердечниках | 1977 |

|

SU658601A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФЕРРИТОВЫХ МАТРИЦ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1972 |

|

SU435566A1 |

Авторы

Даты

1973-01-01—Публикация