1

Изобретение относится к вычислительной технике и предназначено для контроля ферритовых матриц.

Известно устройство для контроля запоминаюидах матриц оперативной памяти, содержащее блок управления, блок регистра адреса, блок дешифраторов, прижимное приспособление для проверяемой ферритовой матрицы, блок контроля, блок усилителей считывания, формирователи тока 1.

Наиболее близким техническим решением к изобретению является устройство, которое содержит блок управления, соединенный с регистрами адреса, дешифраторами, усилителями считывания, блоком сравнения, блоком многокаскадных генераторов тока, коммутаторами и блоком выполнения диагностических тестов, и шаблон для контролируемой ферритовой матрицы, соединенный с коммутаторами и усилителями считывания 2.

Однако отсутствие автоматической р ггистрации результатов контроля снижает быстродей ствие и надежность этого устройства, кроме того, оно позволяет определить область хранения информации (ОХИ) контролируемых фсрритовых матриц только по четырем точкам, что снижает качество проверки матриц.

Целью изобретения является повышение быстродействия и надежности устройства.

Это достигается тем, что устройство для контроля ферритовых матриц содержит блок задания и анализа режимов, входы которого соединены с выходом блока выполнения диагностических тестов и блока сравнетшя, а вы10ходы - с входами многокаскадных генераторов тока и блока управления, и блок регистрации результатов контроля, входы которого подключены к выходам регистра адреса блока управления, блока сравнения, блока выполне15ния диагностических тестов и к второму выходу блока задания и анализа режимов, а выход соединен с регистрируюцим прибором.

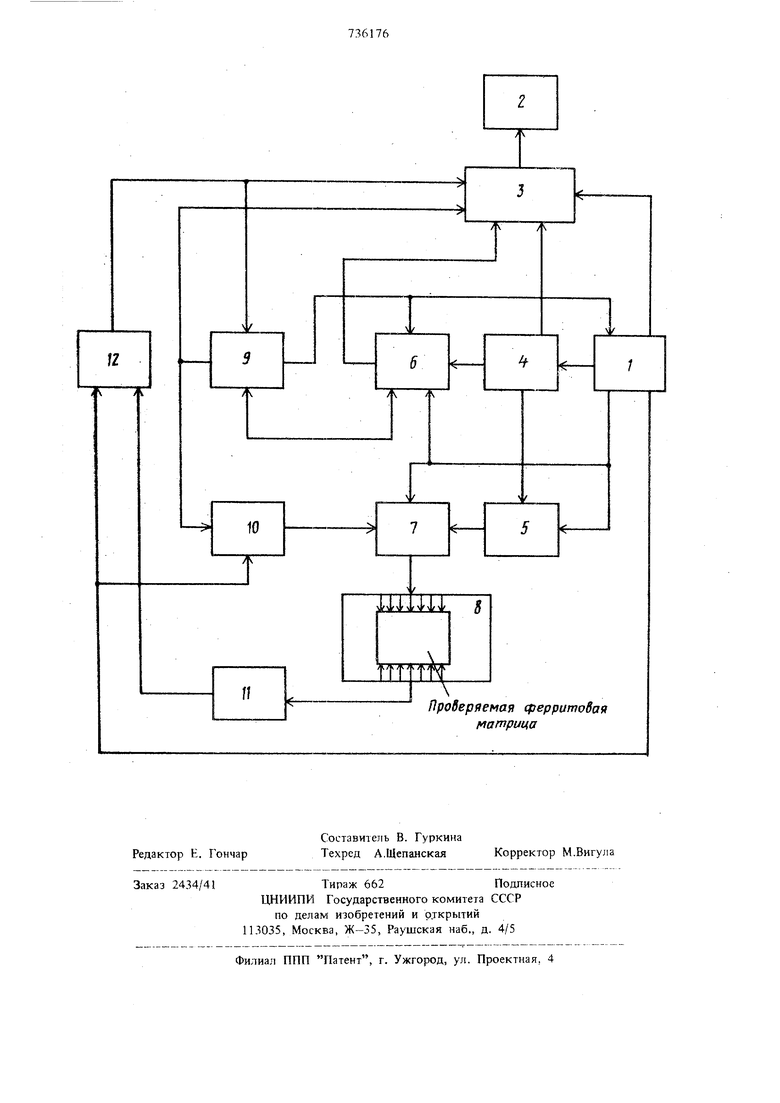

На чертеже представлена блок-схема устройства.

20

Она содержит блок управления 1, регистрирующий прибор (РП) 2, блок 3 регистрации результатов контроля, регистры адреса 4, дешифраторы 5, блок 6 выполнения диагности есКих тестов, коммутаторы 7, 1иаблои 8, б/юк 9 задания и анализа режимов, многокаскадные генераторы токов 10, усилители П считывания., блок 12 сравнения.

Устройство работает следующим образом. При определении области хранения информаили (ОХ матриц оператор на панели управления уста авливает граничные значения токов, программу проверки, вид диапюстических тестов, вид области (полная или частичная ОХИ), способ вывода результатов проверки {автоматическая печать или ручная запись) и производит пуск . устройства.

: При этом блок управления 1 вырабатывает все необходимые сигналь запуска регистров адреса 4, дешифраторов 5, блока 3 регистраЦни результатов контрюля (если он включен) блока 6 выполнения диапгостических тесгов и блока 9 задания и анализа режимов. В

Зависимости от заданного режима работь меняется уровень в блоке 9 задания и анализа режимов.

первый уровень - при выполнении рзчного режима проверки;

второй уровень - при выполнении автоматического режима снятия (определения) част№1ной области по четырем точкам;

третий уровень - при выполнении авгомашческого режима снятия (определения) полной области во всем диапазоне изменения токов.

При снятии частичной ОХИ матриц по сигналу с блока управле1 ия блок 9 задания ы аттализа режимов переходит во второр организацио1П ый уровень, в нем вырабатываются коды, определяющие значение токов для каждой из 4-х точек и последовательность их выполнения. Значения этих кодов поступают на многокаскадные генераторы тока 10, При а1ятии полной ОХИ блок 9 задания и анализа режимов переходит в третий организащотнный уровень, при этом производится запуск многокаскадных генераторов тока 10 и через коммутаторы 7, в соответствии с адресом зап минающей ячейки, в контролируемую матрицу установленную на шаблоне 8, поступают импупьсы адресных и разрядных токов, соответствующие номш)альным значениям. Одновременно в блоке 9 задания и анализа режимов по сигналу из блока 6 выполнения диагностических тестов производится анализ вьшолнелия программы при номинальных значениях токов и запись соответствующей информаиди (диагностического теста), Далее, в соответствии с программой и способом снятия области (ОХИ), запоминается код, соответствующий максимальному значению тока, при этом код номинального значения тока остается. Адресный ток соответствует максимальному значению, а разрядный ток уменьшается с Дискретностью, установленной на панели В каждом шаге изменения разрядного тока (при постоянном адресном) блок 9 анализирует информацию, поступающ ю с запоминающих ячеек проверяемой матрицы.

Если поступают ошибки из блока сравнеffflH 12, характеризующие, что данное значение тока лежит за пределами устойчивой области хранения информации (УОХИ), то в блоке вырабатываются сигналы ддя дальнейшего обхода области. Затем при максимальном 31 ачении адресного тока происходит возрастание разрядного тока до максимального с установленной дискретностью. В каждом шаге изменения тока блок 9 анализирует информа1ЩЮ с проверяемой матрицы, выделяя (если есть) значение токов, соответствующих УОХИ.

После того, как закончится один полн1:.ш шаг автоматического программного изменения и форл-шрования токов, то начинает выполняться второй и т.д. полный шаг с той лишь раз{шцей, что адресный ток уменьшается после каждого полного шага изменения разрядлого тока на ту же дискретность, установленную -с панели управления.

Процесс вьшолнения полных шагов автоматического программного изменения токов, обеспечивающий снятие полной УОХИ и ее реально существующей геометрической формы, выполняется до условия соответствия минимгум адресного тока в УОХИ. На этом процесс снятия (определения) ОХИ заканчивается.

Как в случае снятия частичтюй, так и полной зоны, код с блока 9 задания и анализа режимов поступает на многокаскадные генераторы тока 10, формирующие по коду адресный и разрядный ток, который через коммутаторы 7 действует на ферриты (запом1шающие ячейки) проверяемой матрицы. После усиления сигналов с проверяемой матрицы ус1и1ителями считывания И и анализа их блоком сравнения 12 обеспечивается обратная связь в устройстве, благодаря которой существует возможность иметь информацию о значении токов, амплитуде и форме считанного сигнала, характере ошибок с ферритов проверяемой матрицы адресов сбоев, диагностическом тесте и программе проверки.

При автоматической регистрации обеспечивается вывод всей необхо{шмой информации о значении токов, адресов сбоев и геометрической формы УОХИ на регистрирующий прибор 2.

Технико-экономический эффект, создаваемый изобретением, заключается в том, что устройство контроля ферритовых матриц позволяет повысить производительность труда при проверке, благодаря тому, что полностью авт матизирован процесс контроля ферритовых матриц, автоматическая регистрация результатов проверки позволяет повьюйть надежность и качество проверки. Формула изобретения Устройство для контроля ферритовых матриц, содержащее блок управления, соединенньш с регистрами адреса, дешифраторами усилителями считывания, блоком сравнения, блоком многокаскадных генераторов тока, коммутаторами и блоком выполнения диагностических тестов, и шаблон для контролиру мой ферритовой матрицы, соединенный с ком мутаторами и усилителями считывания, о тличающееся тем, что, с целью по66вышен 1Я быстродействия и надежности устройства, оно содержит блок задания и анализа режимов, входы которого соединены с вь ходом блока выполнения диагностических тестов и блока сравнения, а выходы с входами многокаскадных генераторов тока и блока управления, и блок регистрации результатов контроля, входы которого подключены к выходам блока регистрации адреса, блока управления, блока сравнения, блока выполнения диагностических тестов и к второму выходу блока задания и анализа их режимов, а выход соединен с регистрирующим прибором. Источ(шки информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 3811100, Ю1. G 11 С 29/00. 2.Авторское свидетельство СССР № 376813, кл. G 11 С 29/00 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля запоминающих матриц | 1979 |

|

SU875468A1 |

| Устройство для контроля ферритовых сердечников запоминающих матриц | 1984 |

|

SU1280460A1 |

| Устройство для контроля блоков оперативной памяти | 1984 |

|

SU1265859A1 |

| Устройсто для проверки ферритовых матриц | 1974 |

|

SU548893A1 |

| Устройство для контроля монтажа | 1990 |

|

SU1785001A1 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля параметров ферритовых сердечников запоминающей матрицы | 1984 |

|

SU1200346A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФЕРРИТОВЫХ МАТРИЦ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1972 |

|

SU435566A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

Авторы

Даты

1980-05-25—Публикация

1975-02-14—Подача