1

Изобретение относится к интегральным, запоминающим устройствам.

Известны запоминающие ячейки, состоящие из двухэмиттерного тиристора, коллектор которого через резистор подключен к адресной щине предварительной установки. Один эмиттер соединен с адресной шиной, а второй - с информационным входом записи-считывания. Однако параметры ячеек зависят от свойств микромощных тиристоров. Так, минимальная мощность, рассеиваемая ячейкой, определяется величиной тока выключения тиристора, потому что в открытом состоянии через четырехслойную структуру не может протекать ток, меньший тока выключения. С другой стороны, уменьшение тока выключения, необходимое для уменьщения рассеиваемой мощности, ограничено снизу требованиями помехоустойчивости. Тиристор с малым током выключения обладает очень большой чувствительностью в закрытом состоянии к различным помехам, и схемы на нем практически неработоспособны. Кроме того, получение тиристоров со стабильным и малым по величине током выключения представляет определенные технологические трудности. Таким образом, ухудшение помехоустойчивости с уменьшением величины тола выключения является препятствием для сникевия мощности, рассеиваемой запоминающей ячейкой на микромощных тиристорах.

Целью изобретения является повыщение помехоустойчивости и уменьщение рассеиваемой мощности.

Эта цель достигается тем, что в ячейку введен двухэмиттерный транзистор, база которого соединена с базой /г-типа тиристора, коллектор- с базой р-типа тиристора, вторые эмиттеры транзистора и тиристора подсоединены к щине стробирующего импульса записи, а первые эмиттеры подсоединены к информационным шинам.

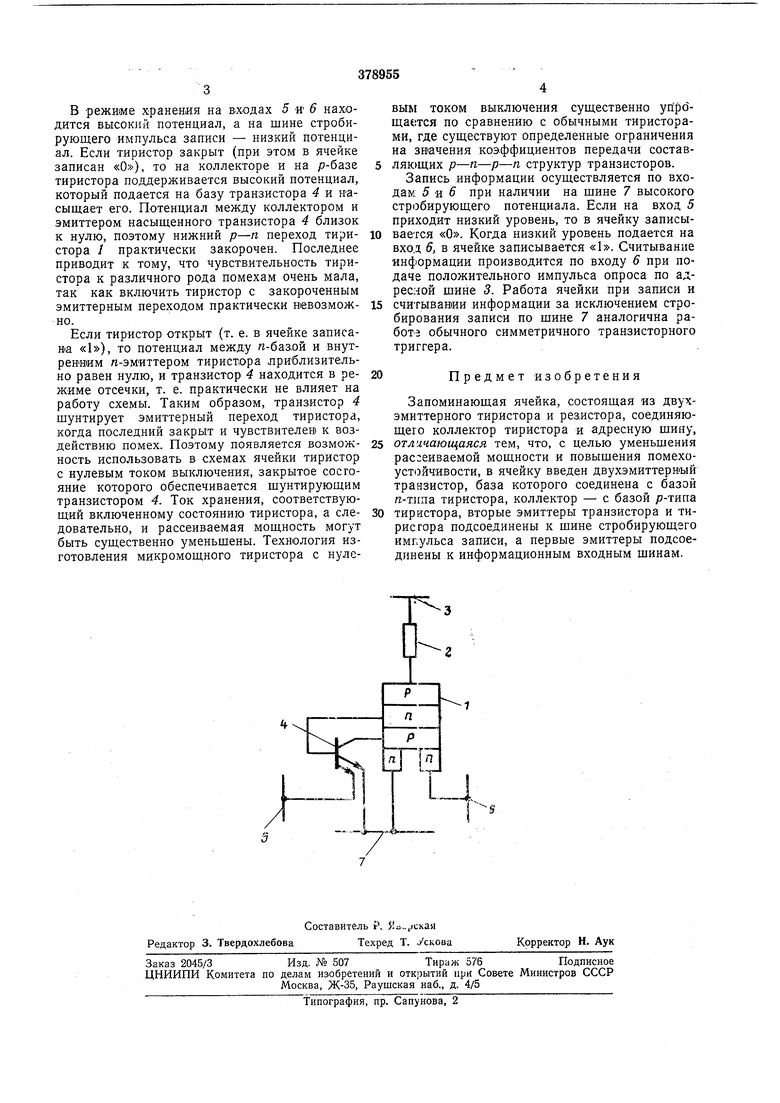

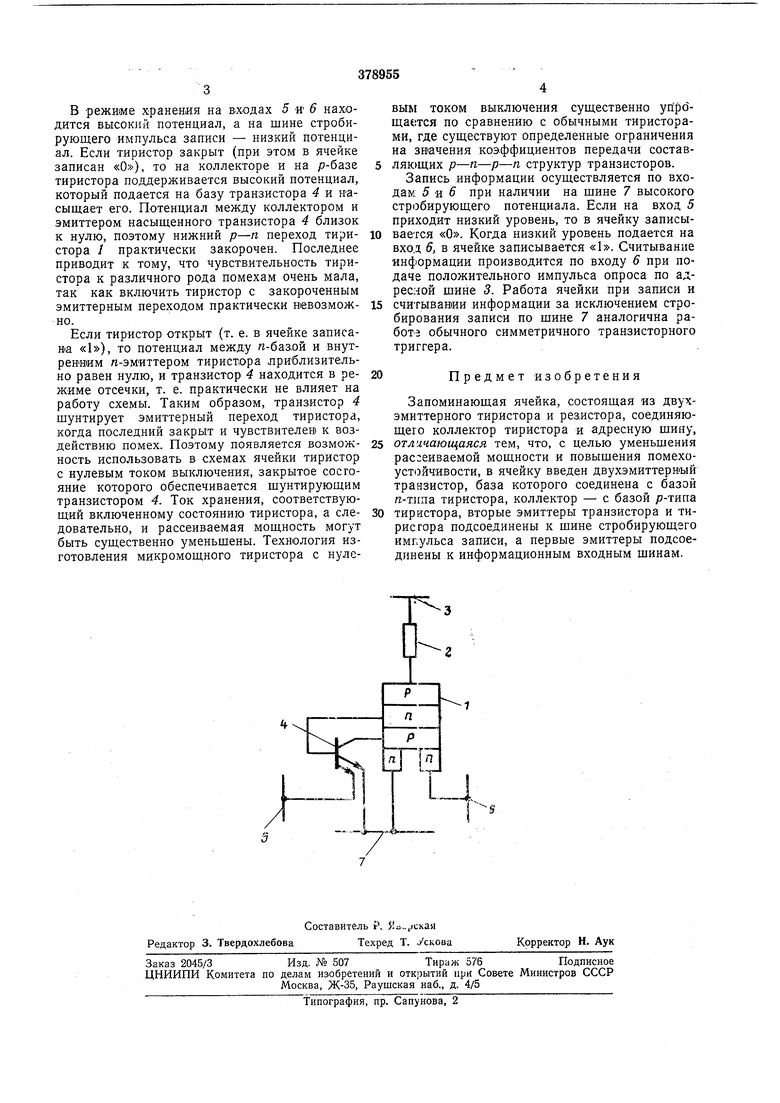

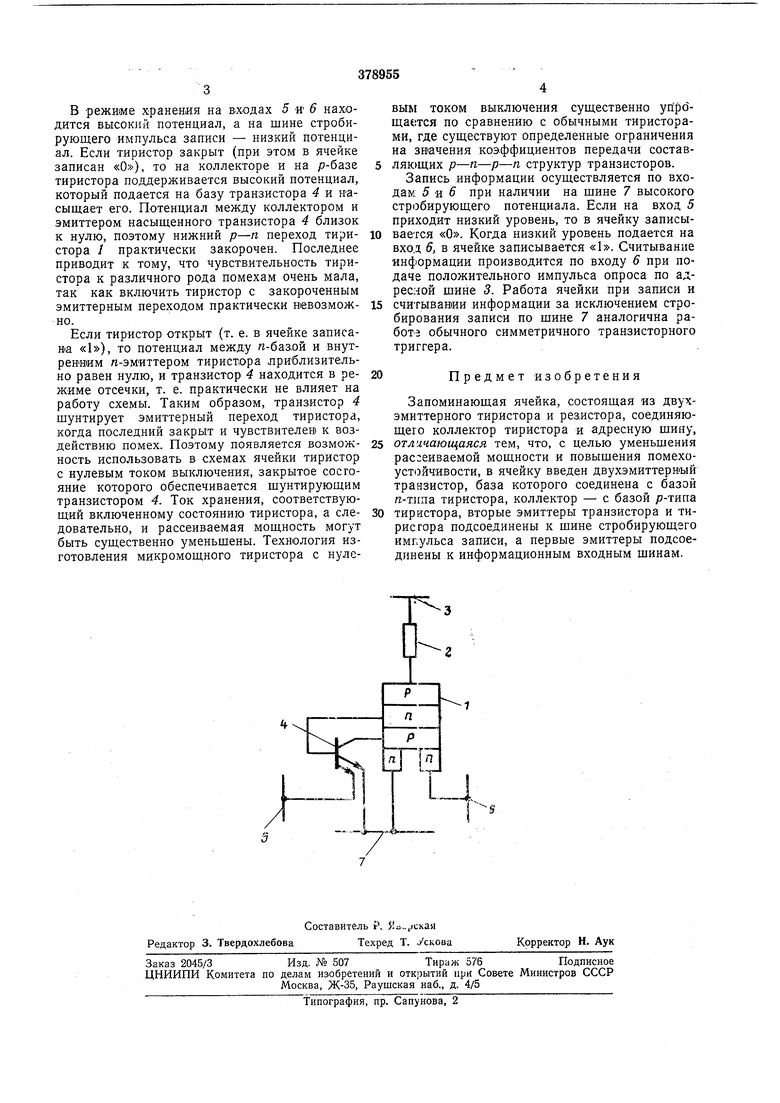

Это позволяет использовать тиристоры с током выключения, равным нулю, а следовательно, и существенно снизить потребляемую ячейкой мощность. При этом технология изготовления тиристоров существенно упрощается, так как снимаются ограничения на стабильность величины тока выключения. На чертеже показана схема предлагаемой

запоминающей ячейки.

Предлагаемая ячейка состоит ,из двухэмиттерного тиристора /, подсоединенного через резистор 2 к адресной щине 3, и двухэмиттерного транзистора 4, база которого соединена

с базовой областью л-типа тиристора, а коллектор - с базой областью р-ткпа. Внешние эмиттеры транзистора и тиристора подсоединены к информационным входам 5 и 6, а внутренние - к шине 7 стробирующего импульса

записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИММЕТРИЧНЫЙ ТИРИСТОРНЫЙ ЭЛЕМЕНТ НАМЯТИ | 1973 |

|

SU381098A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Запоминающий элемент | 1977 |

|

SU733022A1 |

| Симметричный тиросторный элемент памяти | 1976 |

|

SU652613A2 |

| ПАТЕ^Тй1М[Ш';=^^ГНД БсесонэзнАЯ | 1973 |

|

SU377881A1 |

| Запоминающее устройство | 1975 |

|

SU604032A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

Авторы

Даты

1973-01-01—Публикация