1

Изобретение относится к интегральным запоминающим устройствам и может быть использовано в вычислительной технике и системах дискретной автоматики.

Известен запоминающий элемент, содержащий резистор, два р-п-р транзистора и два двухэмиттерных п-р-п транзистора с перекрестными связями 1.

Указанный запоминающий элемент позволяет надежно хранить записанную информацию, но для смены ее. необходимо выключить одну пару транзисторов р-п-р и п-р- п типов, составляющих тиристорную структуру, л включить другую пару р-п-р и п-р-п транзисторов, что существенно снижает его быстродействие.

Кроме того, такой запоминающий элемент занимает больщую площадь при реализации его в интегральном исполнении, в связи с чем он непригоден для построения больщих интегральных схем запоминающих устройств емкостью 1024 бит и более.

Известен также запоминающий элемент, содержащий четыре р-п-р и два п-р-п транзистора, работающих в инверсном включении и перекрестно связанных между собой 2.

Связи между транзисторами осуществлены таким образом, что все транзисторы имеют одну общую область п-типа проводимости

что позволяет весь запоминающий элемент реализовать в одной изолированной области. „ Однако на.тичие больщого количества элементов и перекрестных связей не дает возможности существенно снизить занимаемую элементом площадь и он не может быть использован также для построения больщих интегральных схем запоминающих устройств.

10 Кроме того, известный запоминающий элемент обладает малым быстродействием при считывании информации и малым током считывания, что объясняется связью запоминающего элемента с информационными щинами через медленные р-п-р транзисто ры.

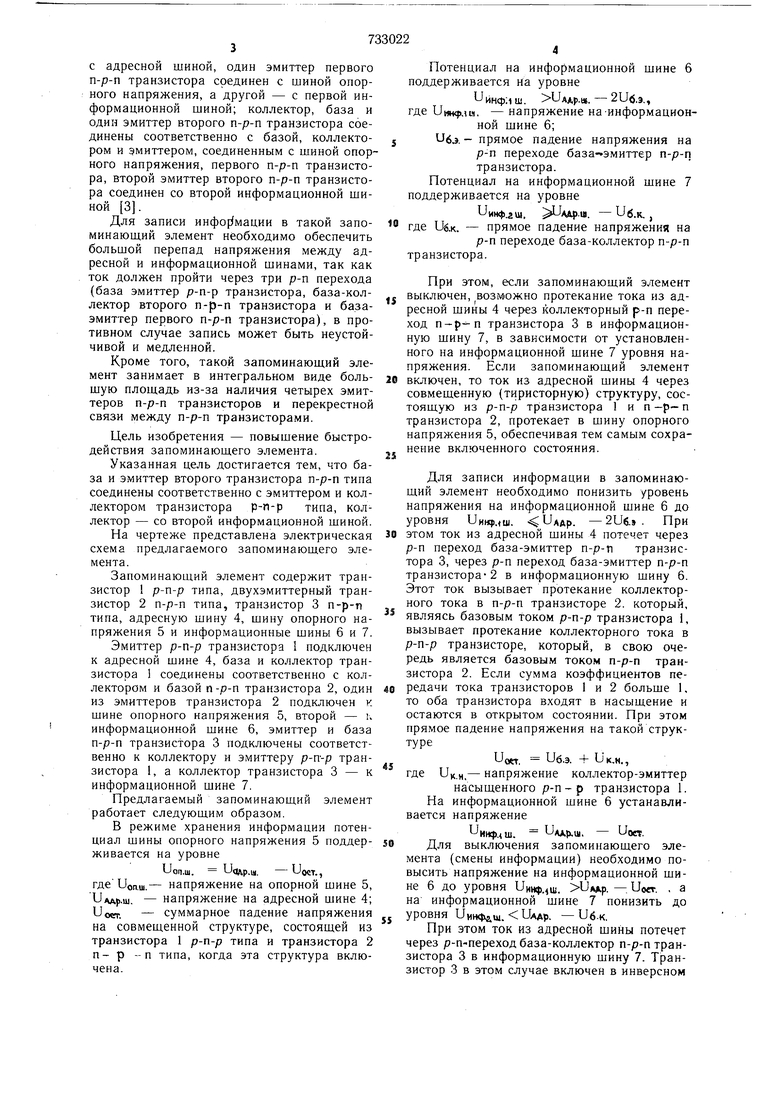

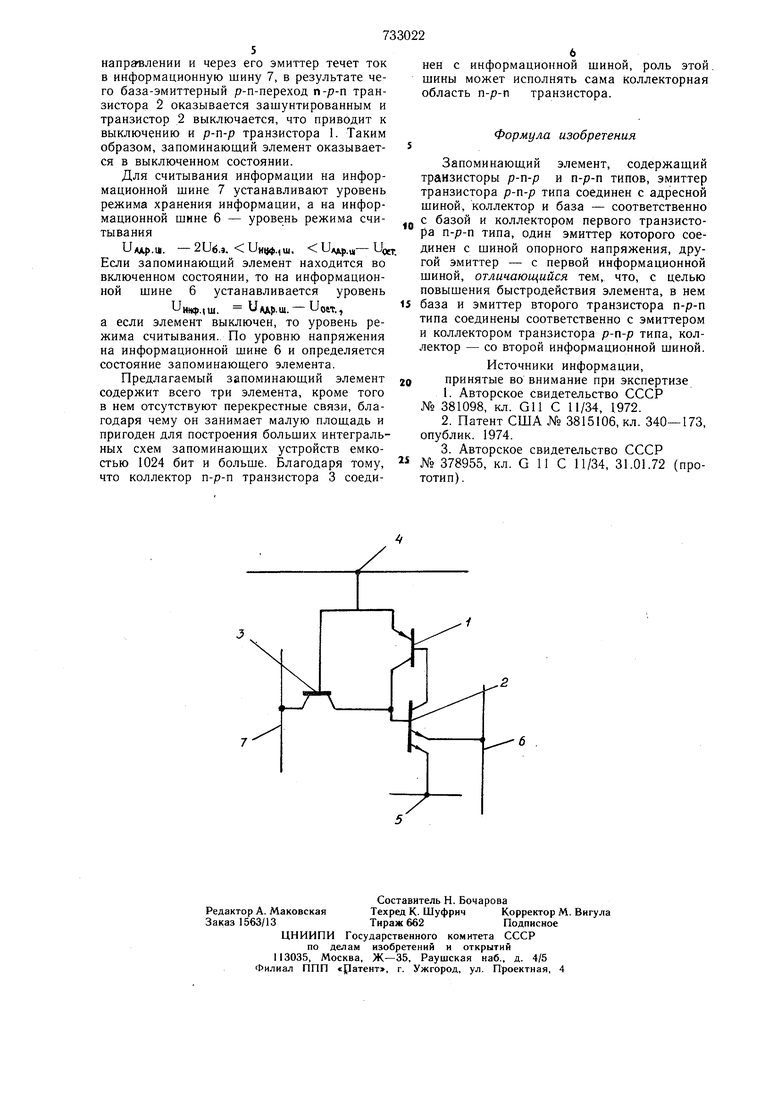

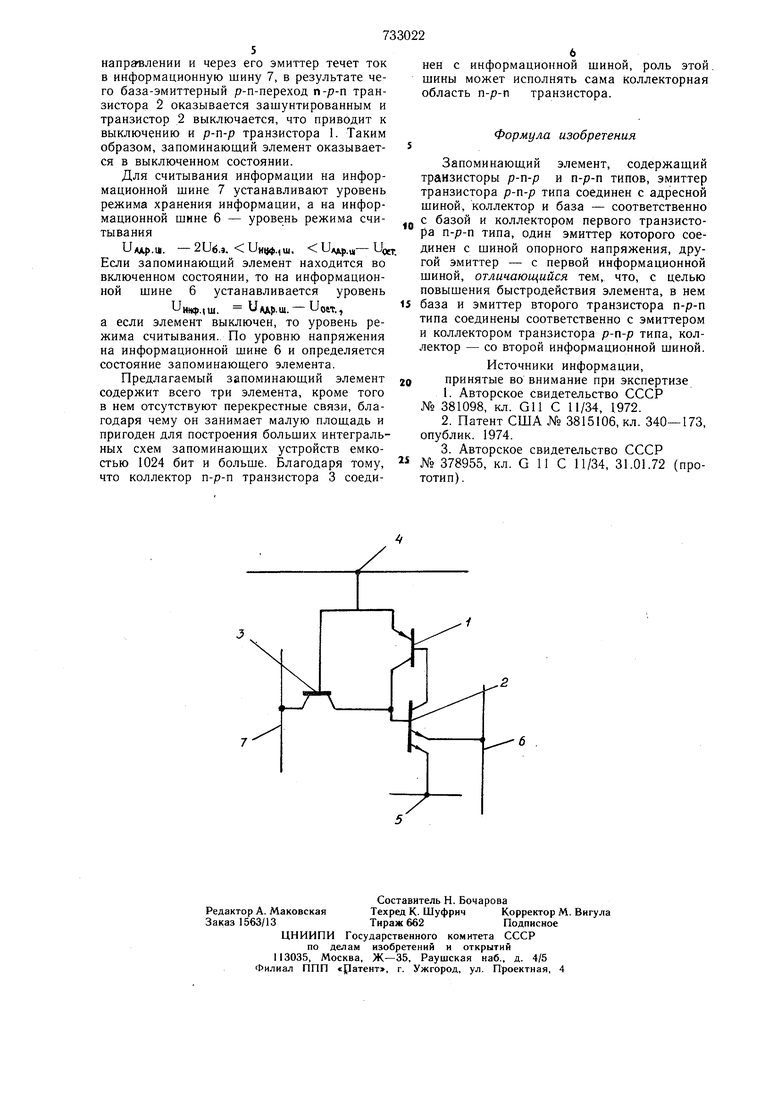

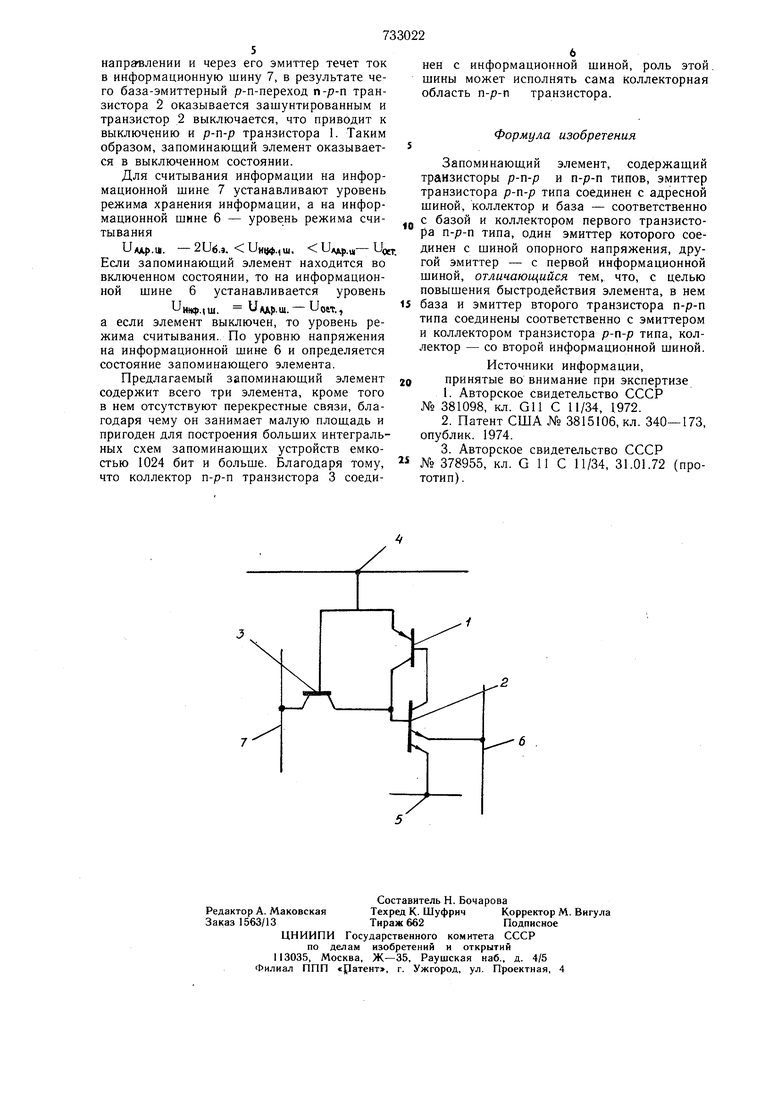

Наиболее близким к предлагаемому является запоминающий элемент, содержащий транзистор р-п-р типа, первый и второй двухэмиттерные транзисторы п-р-п типа, адресную щину, щину опорного напряжения, причем коллектор и база р-п-р транзистора соединены соответственно с базой и коллектором первого транзистора п-р-п типа, эмиттер р-п-р транзистора соединен с адресной шиной, один эмиттер первого п-р-п транзистора соединен с шиной опорного напряжения, а другой - с первой информационной шиной; коллектор, база и один эмиттер второго п-р-п транзистора соединены соответственно с базой, коллектором и эмиттером, соединенным с шиной опорного напряжения, первого п-р-п транзистора, второй эмиттер второго п-р-п транзистора соединен со второй информационной шиной 3. Для записи инфо мации в такой запоминаюший элемент необходимо обеспечить большой перепад напряжения между адресной и информационной шинами, так как ток должен пройти через три р-п перехода (база эмиттер р-п-р транзистора, база-коллектор второго п-р-п транзистора и базаэмиттер первого п-р-п транзистора), в противном случае запись может быть неустойчивой и медленной. Кроме того, такой запоминающий элемент занимает в интегральном виде большую плошадь из-за наличия четырех эмиттеров п-р-п транзисторов и перекрестной связи между п-р-п транзисторами. Цель изобретения - повышение быстродействия запоминающего элемента. Указанная цель достигается тем, что база и эмиттер второго транзистора п-р-п типа соединены соответственно с эмиттером и коллектором транзистора р-п-р типа, коллектор - со второй информационной шиной. На чертеже представлена электрическая схема предлагаемого запоминающего элемента. Запоминающий элемент содержит транзистор р-п-р типа, двухэмиттерный транзистор 2 п-р-п типа, транзистор 3 п-р-г типа, адресную шину 4, шину опорного напряжения 5 и информационные шины 6 и 7. Эмиттер р-п-р транзистора 1 подключен к адресной шине 4, база и коллектор транзистора 1 соединены соответственно с коллектором и базой п-р-п транзистора 2, один из эмиттеров транзистора 2 подключен к шине опорного напряжения 5, второй - к информационной шине 6, эмиттер и база п-р-п транзистора 3 подключены соответственно к коллектору и эмиттеру р-п-р транзистора 1, а коллектор транзистора 3 - к информационной шине 7. Предлагаемый запоминающий элемент работает следуюшим образом. В режиме хранения информации потенциал шины опорного напряжения 5 поддерживается на уровне Uon.m. U(js,p.u - UOCT., где UoaiB.- напряжение на опорной шине 5, UAA(,.UI. - напряжение на адресной шине 4; UOCT. - суммарное падение напряжения на совмещенной структуре, состоящей из транзистора 1 р-п-р типа и транзистора 2 п- р -п типа, когда эта структура включена. Потенциал на информационной шине 6 поддерживается на уровне йнф;1 ш. UAAP.W. - 2 Uti.a., где ).IU. - напряжение на-информационной шине 6; U6j. - прямое падение напряжения на р-п переходе база-эмиттер п-р-п транзистора. Потенциал на информационной шине 7 поддерживается на уровне иинф.гш. . - U6.K., где U6.K. - прямое падение напряжения на р-п переходе база-коллектор п-р-п транзистора. При этом, если запоминающий элемент выключен, возможно протекание тока из адресной шины 4 через коллекторный р-п переход транзистора 3 в информационную шину 7, в зависимости от установленного на информационной шине 7 уровня напряжения. Если запоминающий элемент включен, то ток из адресной шины 4 через совмешенную (тиристорную) структуру, состоящую из р-п-р транзистора 1 и п -р-п транзистора 2, протекает в шину опорного напряжения 5, обеспечивая тем самым сохранение включенного состояния. Для записи информации в запоминающий элемент необходимо понизить уровень напряжения на информационной шине 6 до уровня иинф.ш. илАр. -2Ul . При этом ток из адресной шины 4 потечет через р-п переход база-эмиттер п-р-п транзистора 3, через р-п переход база-эмиттер п-р-п транзистора-2 в информационную шину 6. Этот ток вызывает протекание коллекторного тока в п-р-п транзисторе 2. который, являясь базовым током р-п-р транзистора 1, вызывает протекание коллекторного тока в р-п-р транзисторе, который, в свою очередь является базовым током п-р-п транзистора 2. Если сумма коэффициентов передачи тока транзисторов 1 и 2 больше 1, ТО оба транзистора входят в насыщение и остаются в открытом состоянии. При этом прямое падение напряжения на такой структуреUo«. Ш.Э. + UK.H., где иц.„,- напряжение коллектор-эмиттер насыщенного р-п-р транзистора 1. На информационной шине 6 устанавливается напряжение ин1}.ш. , - oct. Для выключения запоминающего элемента (смены информации) необходимо повысить напряжение на информационной щине 6 до уровня иинф.,ш. им.р. - UO«T. , а на информационной шине 7 понизить до уровня . UAAP. - ий.к. При этом ток из адресной шины потечет через р-п-переход база-коллектор п-р-п транзистора 3 в информационную шину 7. Транзистор 3 в этом случае включен в инверсном напратвлении и через его эмиттер течет ток в информационную шину 7, в результате чего база-эмиттерный р-п-переход п-р-п транзистора 2 оказывается зашунтированным и транзистор 2 выключается, что приводит к выключению и р-п-р транзистора 1. Таким образом, запоминающий элемент оказывается в выключенном состоянии. Для считывания информации на информационной шине 7 устанавливают уровень режима хранения информации, а на информационной шине 6 - уровень режима считыванияUy(Ap.m. -2U6.S. иицф.,ш. иАд.р.и,- Цет Если запоминающий элемент находится во включенном состоянии, то на информационной шине 6 устанавливается уровень иинф.|ш. UAA)).m. - UOHT., а если элемент выключен, то уровень режима считывания. По уровню напряжения на информационной шине 6 и определяется состояние запоминающего элемента. Предлагаемый запоминающий элемент содержит всего три элемента, кроме того в нем отсутствуют перекрестные связи, благодаря чему он занимает малую площадь и пригоден для построения больших интегральных схем запоминающих устройств емкостью 1024 бит и больще. Благодаря тому, что коллектор п-р-п транзистора 3 соединен с информационной шиной, роль этой, шины может исполнять сама коллекторная область п-р-п транзистора. Формула изобретения Запоминающий элемент, содержащий транзисторы р-п-р и п-р-п типов, эмиттер транзистора р-п-р типа соединен с адресной щиной, коллектор и база - соответственно с базой и коллектором первого транзистора п-р-п типа, один эмиттер которого соединен с щиной опорного напряжения, другой эмиттер - с первой информационной щиной, отличающийся тем, что, с целью повыщения быстродействия элемента, в нем база и эмиттер второго транзистора п-р-п типа соединены соответственно с эмиттером и коллектором транзистора р-п-р типа, коллектор - со второй информационной шиной. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 381098, кл. G11 С 11/34, 1972. 2.Патент США № 3815106, кл. 340-173, опублик. 1974. 3. Авторское свидетельство СССР № 378955, кл. G 11 С 11/34, 31.01.72 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1973 |

|

SU444244A1 |

| СИММЕТРИЧНЫЙ ТИРИСТОРНЫЙ ЭЛЕМЕНТ НАМЯТИ | 1973 |

|

SU381098A1 |

| Запоминающий элемент | 1975 |

|

SU562866A1 |

| Инжекционный запоминающий элемент | 1974 |

|

SU526951A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Запоминающее устройство | 1985 |

|

SU1310896A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Запоминающее устройство | 1983 |

|

SU1171848A1 |

Авторы

Даты

1980-05-05—Публикация

1977-06-20—Подача