(5) УСТРОЙСТВО для ВЫБОРКИ ЭЛЕМЕНТОВ ПАНЯТИ В НАКОПИТЕЛЕ

I

Изобретение относится к вычислительной технике и может быть использовано в. запоминакмчих устройствах.

Известны устройства для управления элементами памяти динамического типа на биполярных транзисторах которые соде ржа т п-р-п тоанзистрры и построены по.ключевой схеме tl и Г23.

Известные устройства имеют малую надежность.

Наиболее близким по технической сущности является устройство, которое содермит один двухэмиттерный и два одноэмиттерных транзистора ГЗ.

Это устройство имеет низкую надежность, обусловленную тем, что в про.цессе формирования сигнала выборки при считывании шина управления переключает большой ток, а амплитуда сигнала по шине выборки элементов памяти при считывании невелика.

Цель изобретения - повышение надежности устройства для выборки элементов памяти в накопителе..

Поставленная цель достигается тем, что в устройство для выборки элементов памяти в накопителе, содержащее двухэмиттёрный п-р-п транзистор, база которого соединена с адресной ши. ной, первый эмиттер - с шиной выборки элементов памяти при записи, а второй эмиттер - с шиной выборки элементов памяти при считывании, .

10 п-р-п транзистор, коллектор которого соединен с вторым эмиттером двухэмиттерного п-р-п транзистора и через нагрузочный резистор с первой шиной питания, шину управления и вторую

15 шину питания, введен р-п-р транзистор, база которого пбдклочена к шине .управления, коллектор - к базе п-р-п транзистора, э эмиттер - к адресной шине, причем коллектор двухэмиттёр20 ного п-р-п транзистора подключен к первой шине питания, а эмиттер п-р-п транзистора - к второй шине питания.

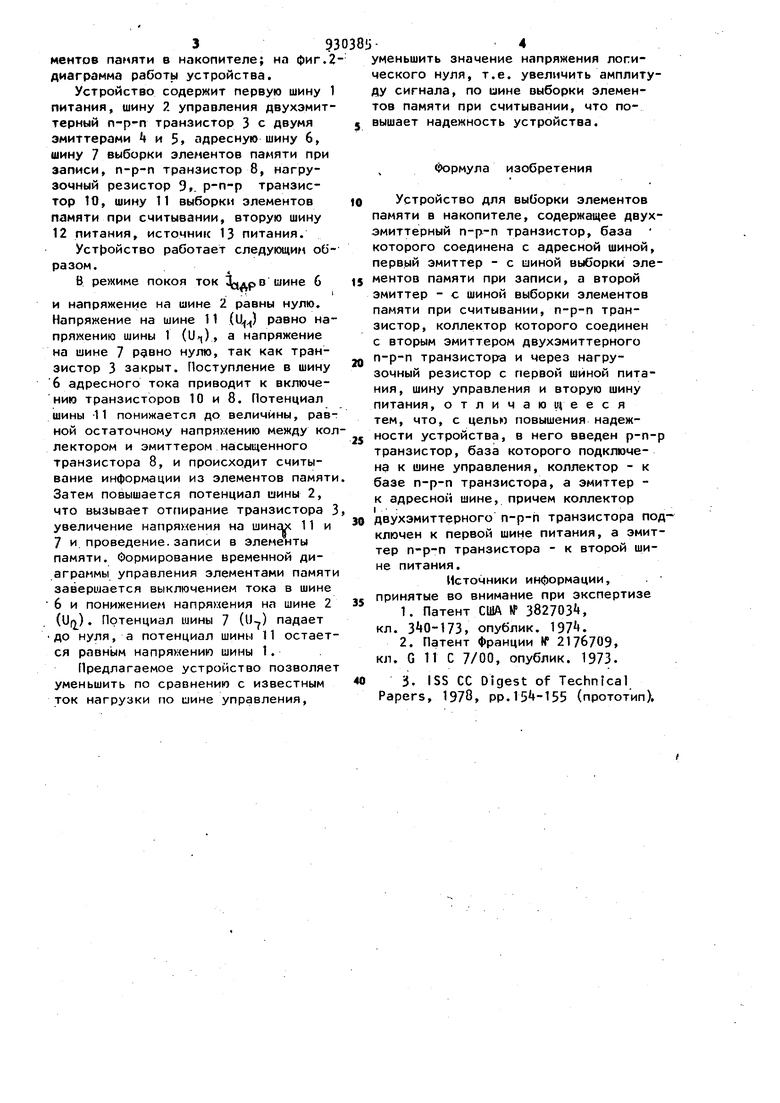

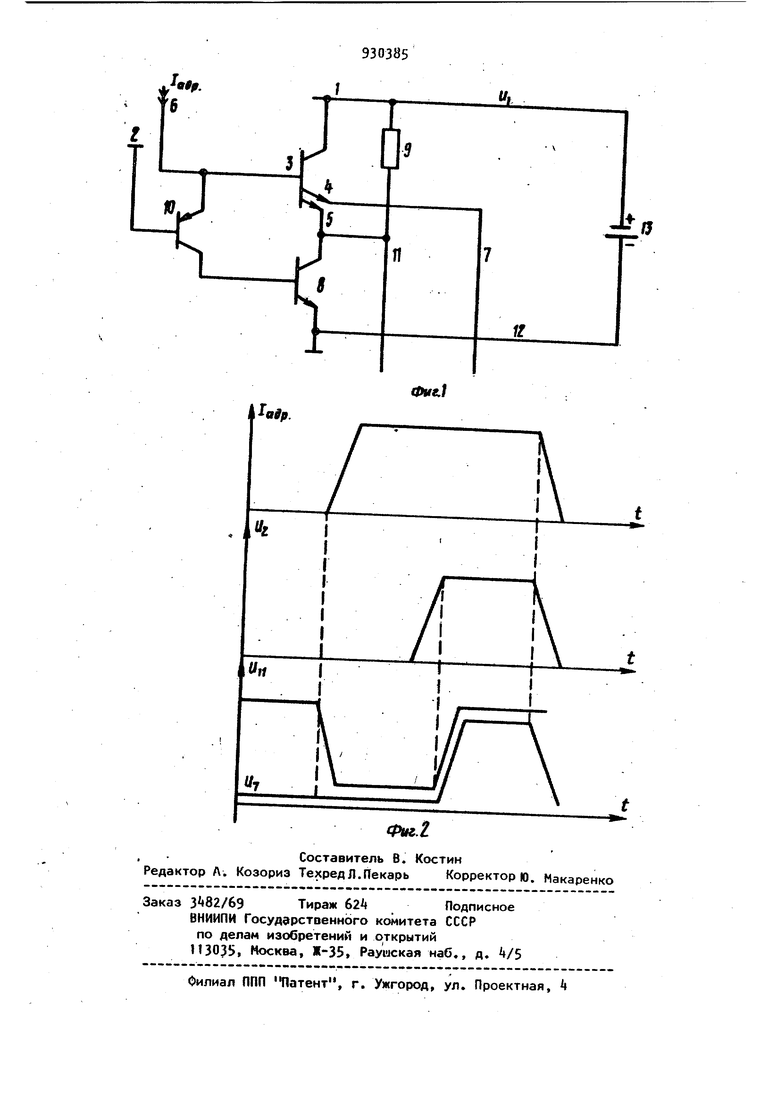

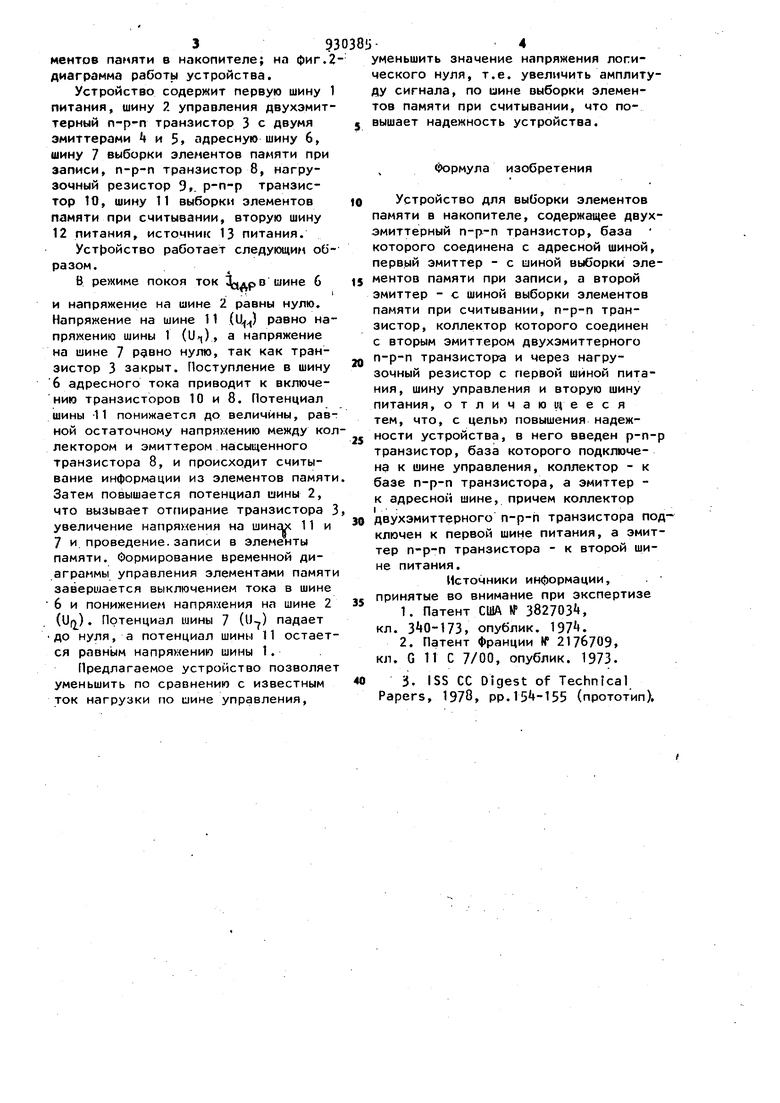

На фиг. 1 изображена электрическал схема устройства для выборки злеентов памяти в накопителе; на фиг.2иаграмма работы устройства.

Устройство содержит первую шину 1 итания, шину 2 управления двухэмиттерный п-р-п транзистор 3 с двумя эмиттерами 4 и 5 адресную шину 6, ину 7 выборки элементов памяти при записи, п-р-п транзистор 8, нагрузочный резистор 9. транзистор 10, шину 11 выборки элементов амяти при считывании, вторую шину 12 питания, источник 13 питания.

Уст{)ойство работает следующим образом.

В режиме покоя ток .рв шине б

и напряжение на шине L равны нулю. Напряжение на шине 11 (Ц) равно напряжению шины 1 (UT), а напряжение на шине 7 нулю, так как транзистор 3 закрыт. Поступление в шину

6 адресного тока приводит к включению транзисторов 10 и 8. Потенциал шины -11 понижается до величины, равной остаточному напря : ению между коллектором и эмиттером насыщенного транзистора В, и происходит считывание информации из элементов памяти. Затем повышается потенциал шины 2, что вызывает отпирание транзистора 3 увеличение напряучения на шингус 11 и 7 и проведение.записи в элементы памяти. Формирование временной диаграммы управления элементами памяти завершается выключением тока в шине

6 и понижением напря)хения на шине 2 (Ufj). Потенциал шины 7 (U-) падает

до нуля, а потенциал шины 11 остается равным напряжению шины 1.

Предлагаемое устройство позволяет уменьшить по сравнению с известным ток нагрузки по шине управления.

уменьшить значение напряжения логического нуля, т.е. увеличить амплитуду сигнала, по шине выборки элементов памяти при считывании, что повышает надежность устройства.

Формула изобретения

Устройство для выборки элементов памяти в накопителе, содержащее двухэмиттерный п-р-п транзистор, база которого соединена с адресной шиной, первый эмиттер - с шиной выборки элементов памяти при записи, а второй эмиттер - с шиной выборки элементов памяти при считывании, п-р-п транзистор, коллектор которого соединен с вторым эмиттером двухэмиттерного

п-р-п транзистора и через нагрузочный резистор с первой шиной питания, шину управления и вторую шину питания, отличающееся тем, что, с целью повышения надежности устройства, в него введен р-п-р транзистор, база которого подключена к шине управления, коллектор - к базе п-р-п транзистора, а эмиттер к адресной шине, причем коллектор

двухэмиттерного п-р-п транзистора подключен к первой шине питания, а эмиттер п-р-п транзистора - к второй шине питания.

Источники информации,

принятые во внимание при экспертизе

1.Патент США № 382703, кл. З 0-173, опублик. 197.

2.Патент франции № 2176709, кл. G 11 С 7/00, опублик. 1973.

3. ISS СС Digest of Technical Papers, 1978, pp. (прототип).

и,

5

9

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь адресного сигнала для оперативного запоминающего устройства | 1981 |

|

SU1015439A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Элемент памяти для накопителя с произвольной выборкой | 1982 |

|

SU1064318A1 |

| Накопитель | 1988 |

|

SU1536442A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1575234A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Оперативное запоминающее устройство | 1979 |

|

SU903972A1 |

Авторы

Даты

1982-05-23—Публикация

1980-09-16—Подача