1

Изобретение относится к области вычислительной техники.

Известны однотактные регистры с обнаружением ошибок. Однако в них блок обнаружения ошибок нригоден только для класса однотактных регистров.

Известны также двухтактные регистры сдвига, в которых возможно возникновение необнаруженных ошибок.

В предлагаемом двухтактном регистре для повышения надежности обнаружения ошибок первые выходы основного и вспомогательного триггера каждого разряда соединены со входами одного элемента, «ИСКЛЮЧЕННОЕ ИЛИ, выход которого соединен со входом первого элемента «ИЛИ, вторые выходы основного триггера каждого разряда и вспомогательного триггера последуюшего разряда соединены со входами другого элемента «ИСКЛЮЧЕННОЕ ИЛИ, выход которого соединен со входом второго элемента «ИЛИ, выходы элементов «ИЛИ соединены со входом соответствующего ему элемента «И, другой вход которого соединен с выходом дополнительного триггера, входы которого соединены с ocHOBiioE и всномогательной тактовой шиной, а выходы элементов «И подключены ко входам третьего элемента «ИЛИ.

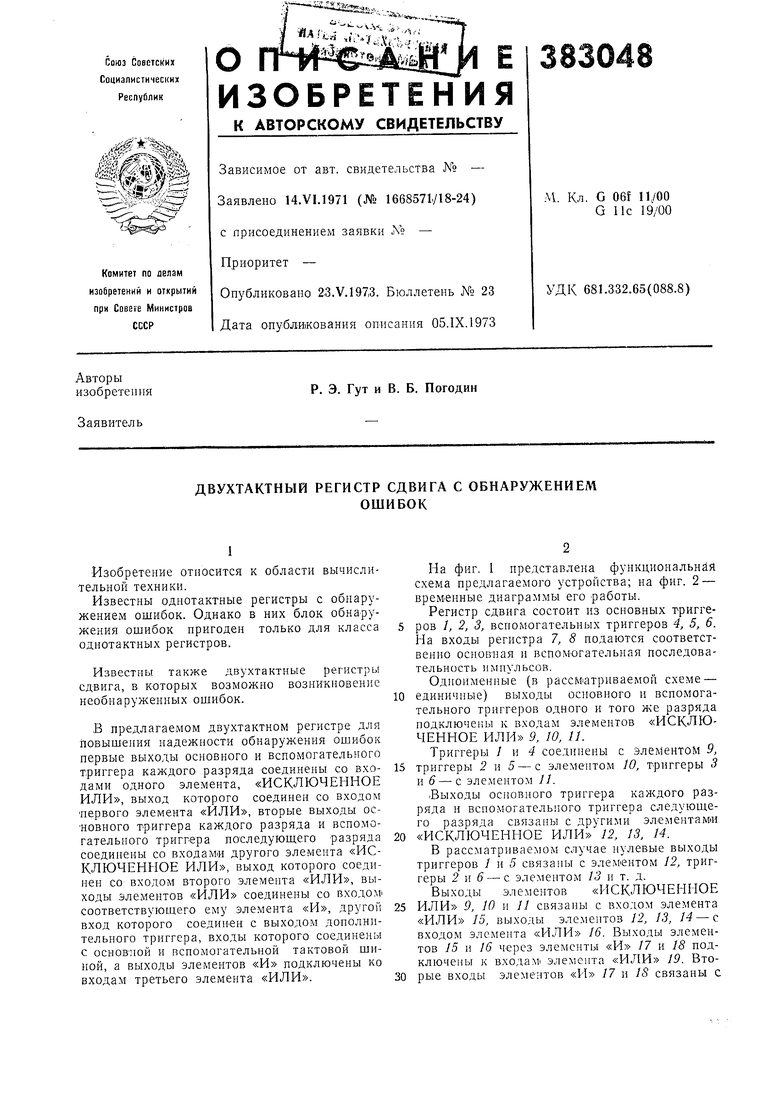

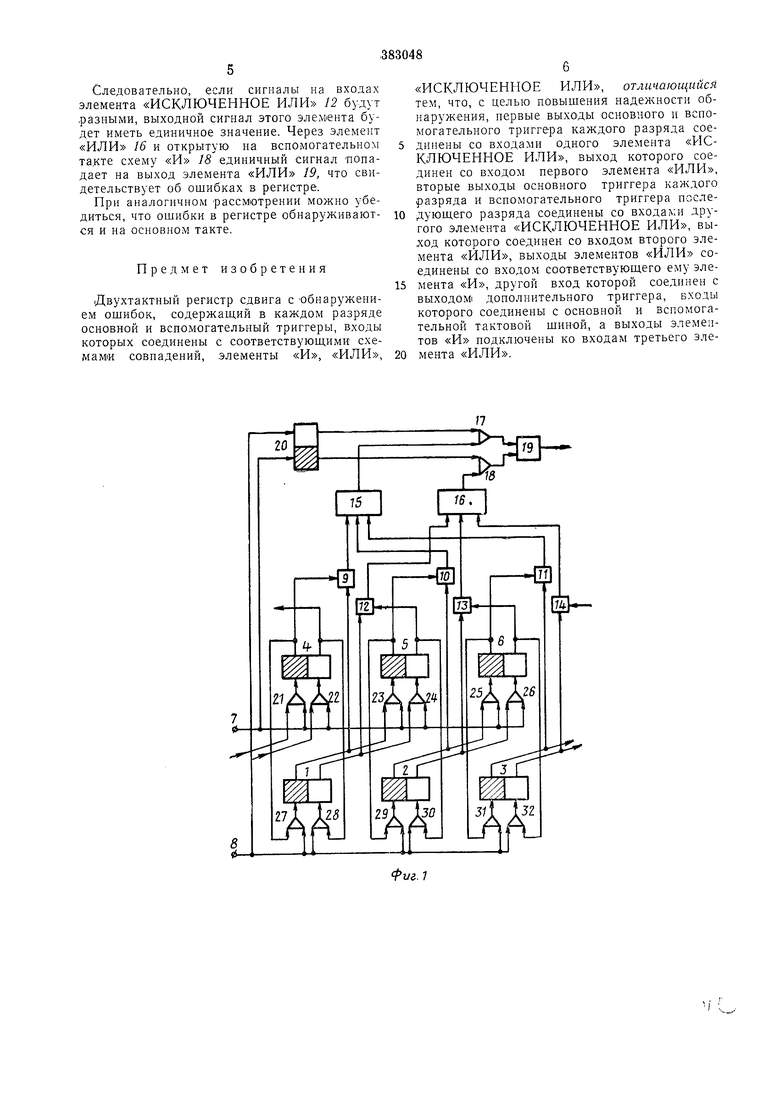

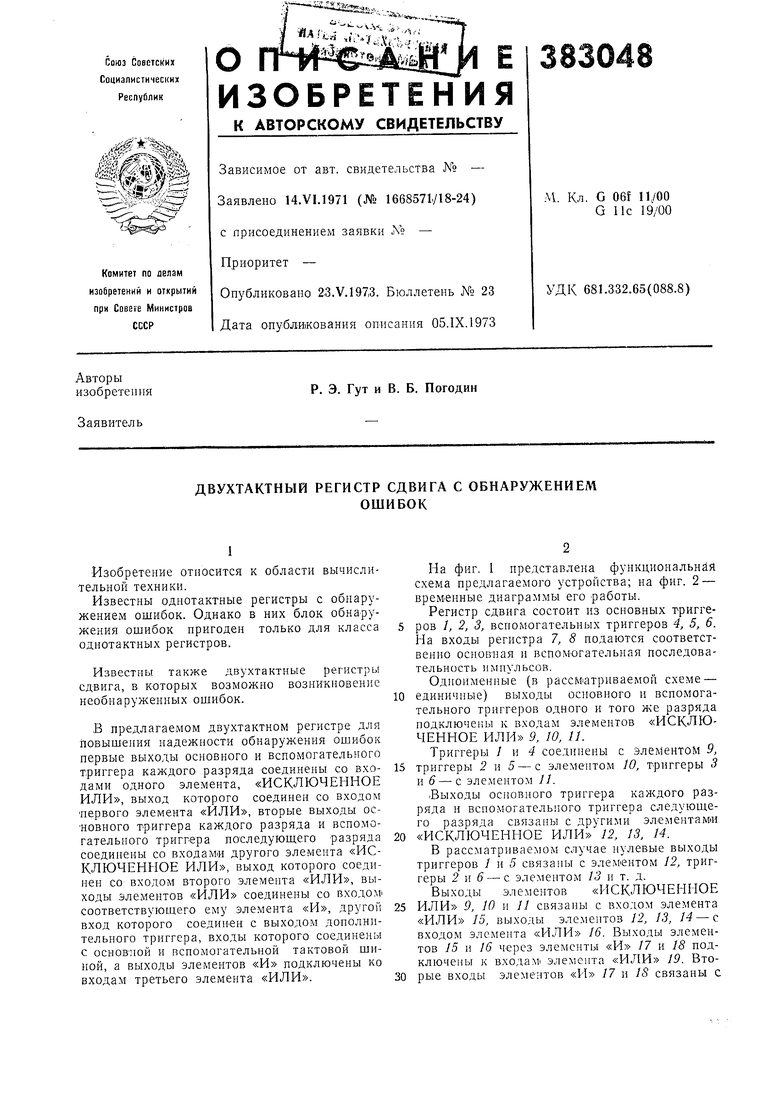

На фиг. 1 представлена функциональнйя схема предлагаемого устройства; на фиг. 2 - временные диаграммы его работы.

Регистр сдвига состоит из основных триггеров /, 2, 3, всномогательных триггеров 4, 5, 6. На входы регистра 7, 8 подаются соответственно осноЕшая и вспомогательная последовательность имнульсов.

Одноименные (в рассм атрнваемой схеме - единичные) выходы основного и всномогательного триггеров одного и того же разряда подключены к входам элементов «ИСКЛЮЧЕННОЕ ИЛИ 9, 10, и.

Триггеры } i 4 соединены с элементом 9, триггеры 2 и 5 - с элементом 10, триггеры 3 и 6-с элементом //.

/Выходы основного триггера каждого разряда н вспомогательного триггера следуюш,его разряда связаны с другими элементами «ИСКЛЮЧЕННОЕ ИЛИ 2, 13, 14.

В рассматриваемом случае нулевые выходы триггеров 1 м 5 связаны с эле М1ентом 12, триггеры 2 м 6 - с элементом 13 н т. д.

Выходы элементов «ИСКЛЮЧЕННОЕ ИЛИ 9, 10 и 11 связаны с входом элемента «ИЛИ 15, выходы элементов 12, 13, 14 - с входом элемента «ИЛИ 16. Выходы элементов 15 п 16 через элементы «И 17 м 18 подключены к входам элемента «ИЛИ 19. Вторые входы элементов «И 17 и связаны с

3

выходами триггера 20, а его раздельные входы подключены к входам регистра 7 и 8:

Запись чисел в триггеры производится через схемы совпадений 21-32, связанные со входами регистра 7 или 8.

Цифровые обозначения на фиг. 2 указывают на то, что соответствующая диаграмма отражает изменение напряжения на выходе элемента схемы на фиг. 1, обозначенного той же цифрой (для триггеров - на единичных выходах).

Первоначально рассмотрим случай, когда ошибки в регистре отсутствуют (см. фиг. 2,а).

Для конкретности предположим, что в основных триггерах регистра 1, 2 н 3 записано число «101 (считая слева). Приходящий первым на вход регистра 7 им нульс вспомогательной последовательности производит запись во вспомогательные триггеры чисел, которые записаны в основных триггерах предыдущих разрядов. Поэтому с приходом вспомогательного импульса в триггере 5 запишется «1, а в триггере 6 - «О. В триггере 4 запишется число из основного триггера предыдущего разряда, не показанного на чертеже, (например «О). Таким образом, при исправной работе после поступления вспомогательного импульса, каждый основной триггер и вспомогательный триггер следующего разряда должны -находиться в одинаковом состоянии. В рассматриваемом примере триггеры 1 и 5 находятся в СОСТОЯНИЕ «1, а триггеры 2 и 6--в состоянии «о. К нулевым выходам триггеров 1, 5 и 2, 6 подключены элементы, реализующие логическую операцию «ИСКЛЮЧЕННОЕ ИЛИ.

Элемент «ИСКЛЮЧЕННОЕ ИЛИ дает на выходе нулевой сигнал только в том случае, когда сигналы на его входах имеют одинаковое значение. Поэтому в данном случае на выходах элементов «ИСКЛЮЧЕННОЕ ИЛИ сигналы будут иметь нулевое значение.

Следовательно, на выходе элемента «ИЛИ 16 сигнал также будет нулевым.

Поступивший на вход 7 вспомогательный имлульс подается также на единичный вход триггера 20 и переводит его в единичное состояние. На единичном выходе этого триггера сигнал имеет единичное значение, а на нулевом выходе - нулевое значение. Эти сигналы поступают на входы элементов «И /7 и 18. Поэтому на выходе элемента 17 сигнал будет нулевым, а значение сигнала на выходе элемента 18 будет определяться тем , какой сигнал имеется на выходе элемента «ИЛИ 16. Поскольку в данном случае этот сигнал будет нулевым, то на входы элемента «ИЛИ /Р поступают нулевые сигналы и на его выходе сигнал также будет нулевым, что свидетельствует об отсутствии ошибок в регистре на первом (вспомогательном) такте.

Далее на вход 8 поступает импульс основной последовательности. Этот импульс попадает на нулевой вход триггера и переводит его в нулевое состояние. Триггер открывает

4

ключ 17 и закрывает ключ 18. Поэтому сигнал на выходе ключа 18 принимает нулевое значение, а значение сигнала на выходе элемента «И 17 совпадает с сигналом, поступающим на него с элемента «ИЛИ 15.

Основной импульс, поступивший на вход 8, производит также запись в основные триггеры каждого разряда чисел, записанных к этому моменту во вспомогательных триггерах того же разряда. В рассматриваемом примере триггер 2 окажется в состоянии «1, как и триггер 5, триггер 5 - в состоянии «О, как и триггер в.

Поскольку после прихода основного импульса основной и вспомогательный триггеры одного и того же разряда при исправной работе регистра должны находиться в одинаковых состояниях, сигналы на выходах элементов «ИСКЛЮЧЕННОЕ ИЛИ 9, 10 и 11 будут иметь нулевое значение и сигнал на выходе элемента «ИЛИ 15 будет также нулевым. Этот нулевой сигнал через открытый элемент «И 17 попадает на вход элемента «ИЛИ 19.

Следовательно, на выходе элемента 19 сигнал будет иметь нулевое значение, что свидетельствует об отсутствии ошибок в регистре на втором такте. Итак в соответствии с Данным нредложением, двухтактный регистр сдвига снабжается двумЯ группами логических элементов «ИСКЛЮЧЕННОЕ ИЛИ. Одна группа (элементы 12, 13, 14) предназначена для контроля исправности работы регистра на всномогательном такте (т. е. на отрезке времени между вспомогательным и основным импульсом), а вторая группа (элементы 9, 10 и 11) --для контроля на основном такте (на отрезке i peмени между основным и следующим вспомогательным импульсами).

Выходы каждой группы объединяются с помощью элементов «ИЛИ 16 ъ 15 Е. подключаются на время длительности соответствующего такта к выходам собирательной схемы

«ИЛИ 19 с помощью триггера 20. Поэтому, если в процессе передачи информации на одHOMi или другом такте в регистре возникнут ошибки, т. е. ноявится несогласованность между соответствующими триггерами, это сразу

же будет зафиксировано соответствующим элементом «ИСКЛЮЧЕННОЕ ИЛИ.

Естественно, что ошибка, возникшая на соответствующем такте одновременно в двух триггерах, связанных с одним элементом «ИСКЛЮЧЕННОЕ ИЛИ, не будет обнаружена. Однако вероятность таких ошибок, как показывают эксперименты, очень мала по сравнению с вероятностью одиночных ошибок. Для примера рассмотрим случай, когда при

той же исходной комбинации состояний «101, на вспомогательном такте происходит сбой триггера 5 (см. фиг, 2,6). При этом триггер 5 вместо того, чтобы перейти в единичное состояние, как это должно быть при исправной

работе, остается в нулевом состоянии.

Следовательно, если сигналы на входах элемента «ИСКЛЮЧЕННОЕ ИЛИ 12 будут .разными, выходной сигнал этого элемента будет иметь единичное значение. Через элемент «ИЛИ 16 и открытую на вспомогательном такте схему «И 18 единичный сигнал -попадает на выход элемента «ИЛИ 19, что свидетельствует об ошибках в регистре.

При аналогичном рассмотрении можно убедиться, что ошибки в регистре обнаруживаются и на основном такте.

Предмет изобретения

Двухтактный регистр сдвига с Обнаружением ошибок, содержанций в каждом разряде основной и вспомогательный триггеры, входы которых соединены с соответствуюш ими схемами совпадений, элементы «И, «ИЛИ,

6

«ИСКЛЮЧЕННОЕ ИЛИ, отличающийся тем, что, с целью повышения наделчности обнаружения, первые выходы основного и вспомогательного триггера каждого разряда соединены со входами одного элемента «ИСКЛЮЧЕННОЕ ИЛИ, выход которого соединен со входом первого элемента «ИЛИ, вторые выходы основного триггера каждого разряда и вспомогательного триггера после10 дуюш,его разряда соединены со входами другого элемента «ИСКЛЮЧЕННОЕ ИЛИ, выход которого соединен со входом второго элемента «ИЛИ, выходы элементов «ИЛИ соединены со входом соответствующего ему элемента «И, другой вход которой соединен с ВЫХОДОМ1 дополнительного триггера, входы которого соединены с основной и вспомогательной тактовой шиной, а выходы элементов «И подключены ко входам третьего эле20 мента «ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации биимпульсного сигнала | 1985 |

|

SU1350837A1 |

| Электронный распределитель | 1986 |

|

SU1392624A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Устройство контроля цифровых блоков | 1985 |

|

SU1339567A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Устройство для обнаружения и исправления ошибок | 1980 |

|

SU938415A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Устройство для измерения характеристик дискретного канала связи | 1990 |

|

SU1741278A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

.MJ

Авторы

Даты

1973-01-01—Публикация