1

Изобретение относится к вычислительной технике и предназначено для алгебраического суммирова.ния двоично-десятичных кодов.

Известен последовательный двоично-десятичный сумматор-вычитатель, содержащий два сумматора со схемами фармирования переноса, формирователь инверсного кода, четырехразрядный регистр сдвига, схему коррекции с триггером коррекции. Однако сигнал, подаваемый на вход триггера кор рекции, формируется с помощью многокаскадной логической схемы, -вносящей задержку.

Предлагаемое устройство отличается тем, что выход схемы формировайия переноса первого сумматора соединен со -входом триггера коррекции, прямой и инверсный -выходы которого соединены со входами соответствуюЩ1ИХ элементов «И схемы коррекции, соеди«енных по .входам с управляющими щинами «сложение и «вычитание и с выходами соответствующих элементов «ИЛИ, входы которых соединены с синхронизирующими входами устройства, выходы элементов «И через элемент «ИЛИ .соединены со -входом второго сумматора.

Это позволяет упрост1ить устройство и повысить его быстродействие.

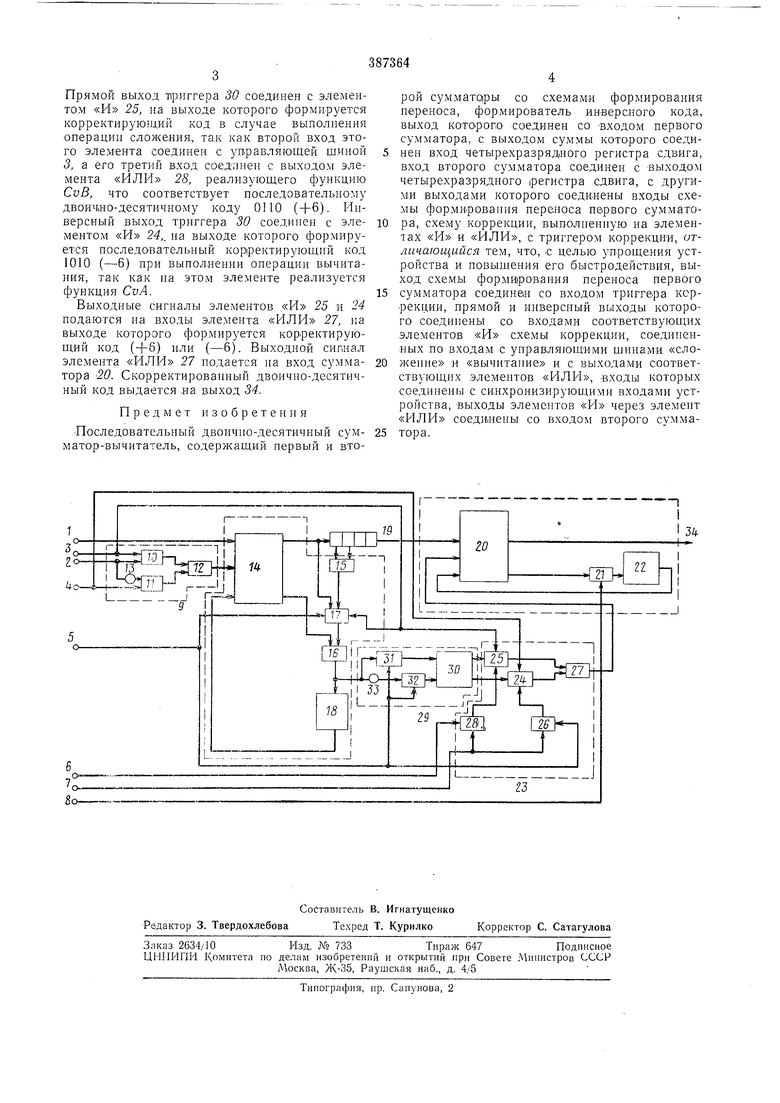

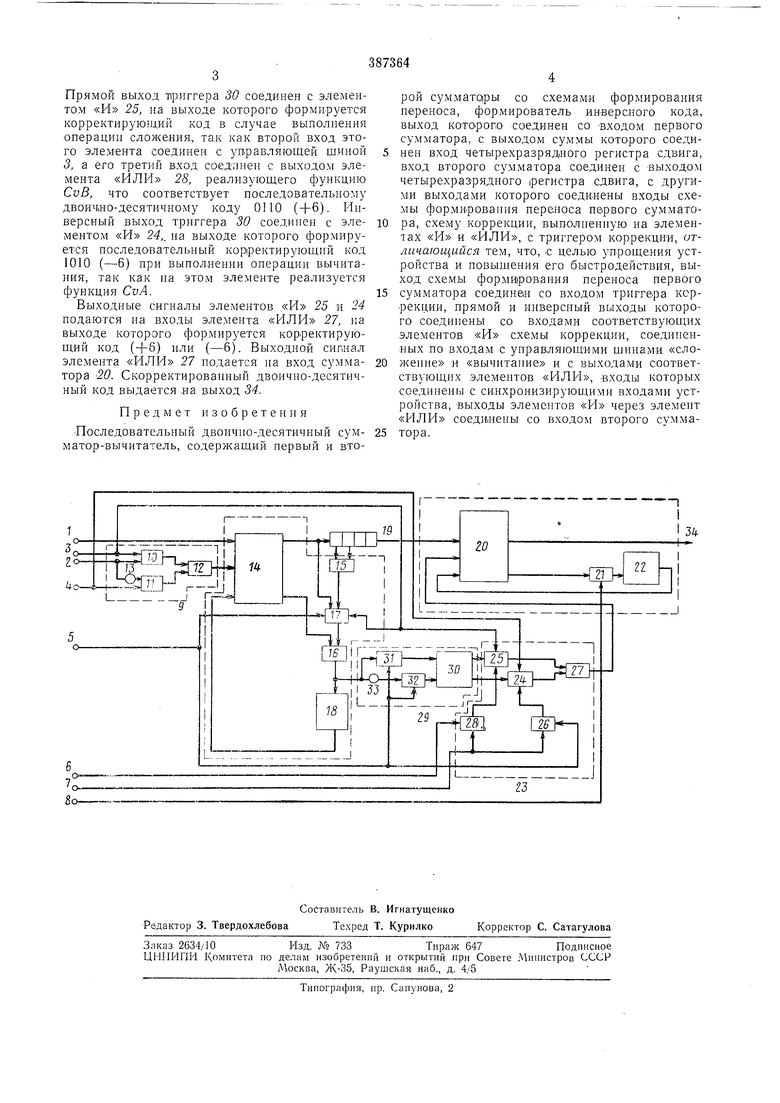

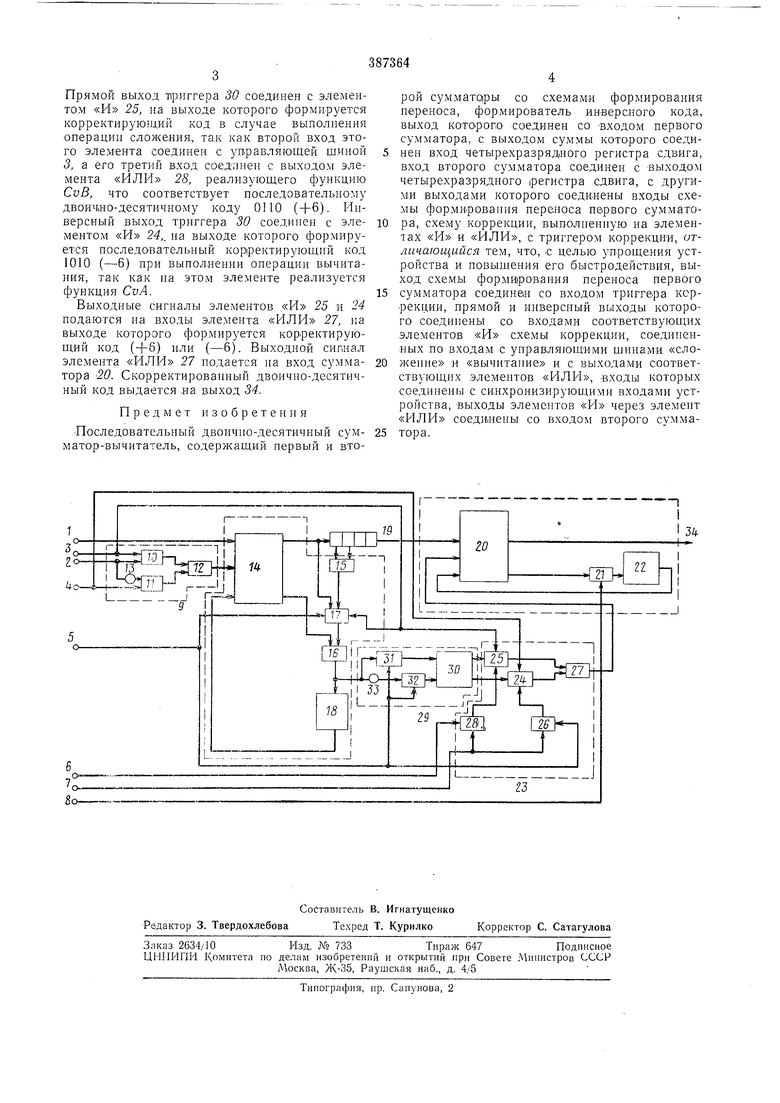

На чертеже изображена схема предлагаемого сумматора-вычитателя.

Устройство содержит входы 1 .ц 2 для подачи слагаемых, уп|равляющие щины «сложеиие 3 и «вычитание 4, синхро.низируюндие входы 5-8 для подачи сдвинутых отнооительйо друг друга синхроимпульсов А, В, С и ипверсного синхроимлульса Л соответственно, форм-ирователь 9 инверсного кода, выпол.ненный на элементах «И 10 и 11, «ИЛИ 12, «НЕ 13, сумматор 14 со схемой формирования переноса на элементах «ИЛИ 15 и 16,

«И /7 и триггере 18 переноса, четырехразрядный регистр 19 сдвига, сумматор 20 со схемой формирован;ия переноса па элементе «И 21 и триггере 22 переноса, схему 23 коррекции на элементах «И 24 и 25, «ИЛИ 26,

27, 28; триггер 29 коррекции, содержащий -собственно триггер 30, элементы «И 31, 32, «НЕ 33; выход 34.

Два числа в последовательном коде поступают на входы / и 2. При выполнении сложекия на управляющей щине 3 уста.навливается

уровень «1, а при выполнении -вычитания

уровень «1 устанавливается на управляющей щине 4. Нескорректированное значение

двоично-десятичной тетрады, полученное па

выходе сумматора 14, заносится в регистр 19 сдвига. Сигнал переноса, сформированный схемой переноса сумматора 14, записывается в триггер 29 коррекции синхроимпульсом Л, возникающим на входе 6 в момент оконча.пия

сложения одной двоично-десятичной тетрады.

Прямой выход тприггера 30 соединен с элементом «И 25, на выходе которого формируется корректирующий код в случае выполнения операции сложения, так как второй вход этого элемента соединен с управляющей щиной 3, а его третий вход соединен с выходом элемента «ИЛИ 28, реализующего функцию CvB, что соответствует последовательному двоичло-десятичному коду ОНО (+6). Инверсный выход триггера 30 соединен с элементом «И 24,, на выходе которого формируется последовательный кор|ректирующий код 1010 (-6) ири выполиении операции вычитания, так как на этом элементе реализуется функция CvA.

Выходные сигналы элементов «И 25 и 24 подаются на входь элемента «ИЛИ 27, на выходе которого формируется корректирующий код (Н-6) или (-6). Выходной сигнал элемеита «ИЛИ 27 иодается на вход сумматора 20. Скорректированный двоично-десятичный код выдается на выход 34.

Предмет изобретения

Последовательный двоичио-десятичиый сумматор-вычитатель, содержащий первый и второй сумматоры со схемами формирования иереноса, формирователь инверсного кода, выход котОрого соединен со входом первого сумматора, с выходом суммы которого соеди5 ней вход четырехразрядного регистра сдвига, вход второго сумматора соединен с выходом четырехразрядного 1регистра сдвига, с другими выходами которого соединены входы схемы формироваиия переноса первого сумматора, схему коррекции, выиолнеиную на элементах «И и «ИЛИ, с триггером коррекции, отличающийся тем, что, с целью упрощения устройства и иовышения его быстродействия, выход схемы форми|роваиия переноса первого

5 сумматора соединен со входом триггера коррекции, прямой и инверсный выходы которого соединены со входами соответствующих элементов «И схемы коррекции, соедниениых по входам с управляющими щииами «сло0 жение и «вычитатще и с выходами соответствующих элементов «ИЛИ, входы которых соединены с синхронизирующими входами устройства, выходы элемеитов «И через элемент «ИЛИ соединены со входом второго сумма5 тора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Разряд двоично-десятичного сумматора | 1972 |

|

SU441562A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый и дВОичНО-дЕСяТичНОгОВ дВОичНый | 1979 |

|

SU849197A1 |

Авторы

Даты

1973-01-01—Публикация