1

Изобретение относится к области электронной вычислительной техники и может быть иснользовано в аппаратуре контроля и настройки цифровых узлов ЭВМ.

Известны устройства, содержащие запоминающее устройство (ЗУ) для хранения тестов, регистр теста, устройство записи информации из ЗУ в регистр теста, формирователи входных и выходных сигналов, коммутационное устройство и устройство сравнения.

К недостаткам этих устройств следует отнести:

больщое количество переключателей, необходимое для коммутации входных и выходных контактов проверяемого цифрового узла;

большое количество разрядов регистров;

сложную схему контроля исправности входных и выходных формирователей и коммутационного устройства.

Целью изобретения является уменьшение количества переключателей в коммутационной схеме и количества разрядов регистров в регистре теста при одновременном упрощении схемы контроля исправности входных и выходных формирователей и коммутационного устройства.

Эта цель достигается тем, что запоминающая ячейка любого из разрядов регистра теста подключена через выходной формирователь и переключатель коммутационного замкнутого устройства и через параллельно включенные им схему совпадения и входной формирователь к входному контакту проверяемого цифрового узла.

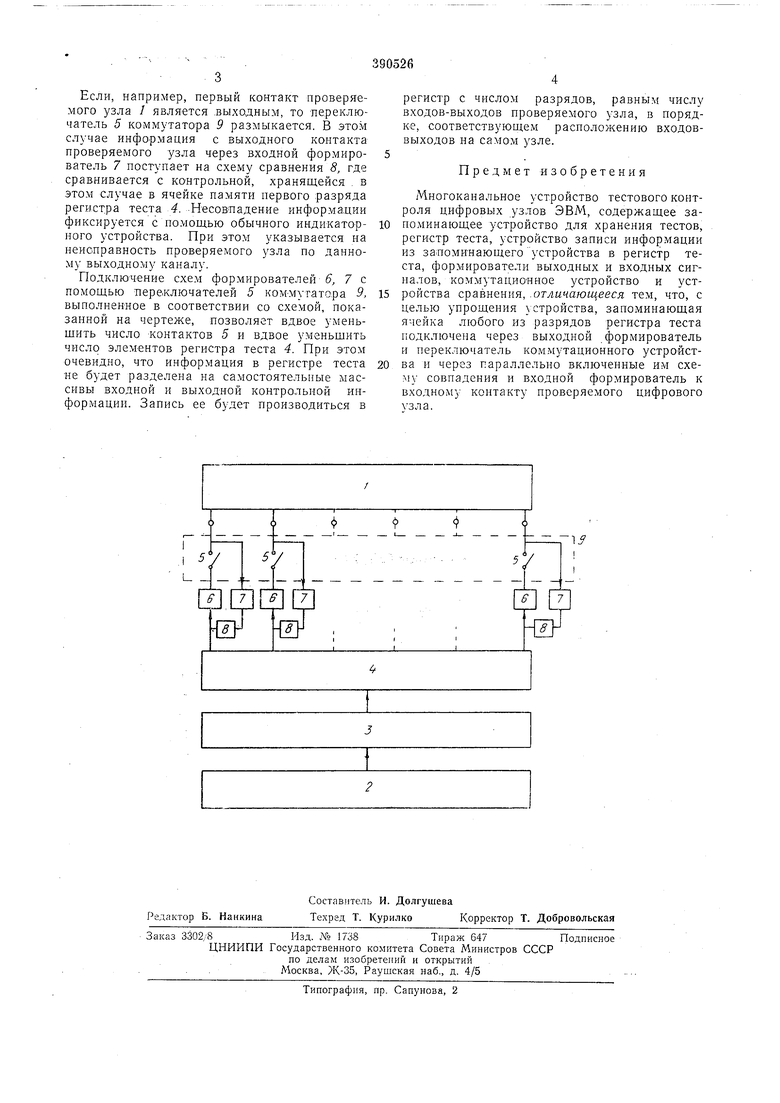

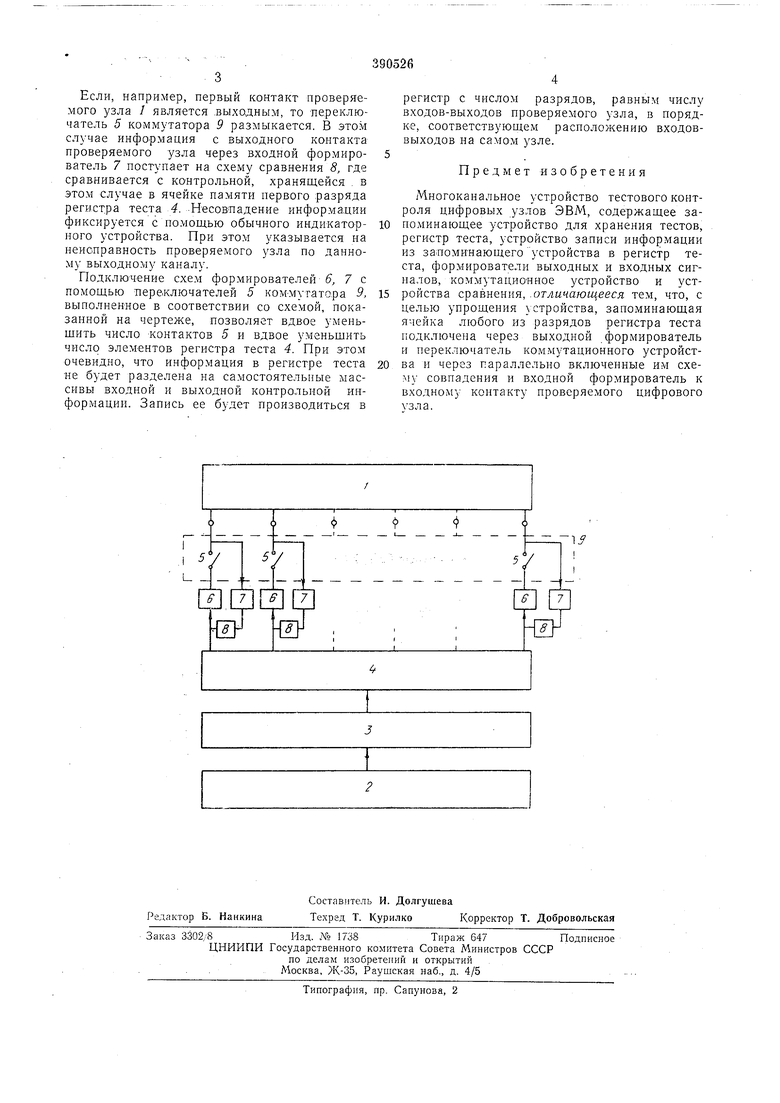

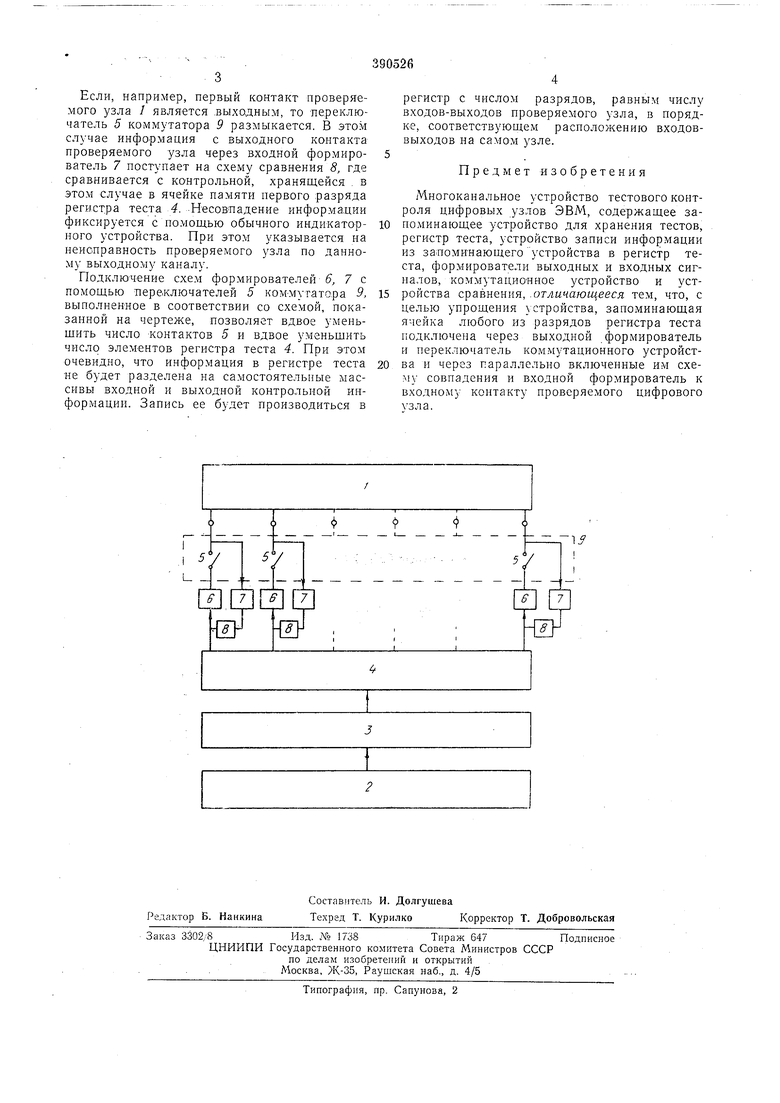

Функциональная схема предлагаемого многоканального устройства тестового контроля цифровых узлов ЭВМ показана на чертеже.

Устройство работает следующим образом.

Проверяемый узел 1 имеет п контактов, каждый из которых может быть входным илп выходным. Тестовая информация из ЗУ 2 через устройство записи 3 записывается в регистр теста 4.

Если, например, первый контакт проверяемого узла является входным, то переключатель 5 замыкается, и информация с запоминающей ячейки первого разряда регистра теста 4 через выходной формирователь 6 поступает на этот контакт. Одновременно эта же информация через входной формирователь 7 цоступает на схему сравнения 8, где сравнивается с исходной информацией, хранящейся в ячейке памяти первого разряда

регистра теста 4. Несовпаденпе информации фиксируется индикатором, .который на чертеже не показан. С помощью такого подключения осуществляется контроль исправности формирователей 6, 7 и переключателей 5коммутатора 9.

Если, например, первый контакт проверяемого узла / является .выходным, то переключатель 5 коммутатора 9 размыкается. В этом случае информация с выходного контакта проверяемого узла через входной формирователь 7 поступает на схему сравнения 8, где сравнивается с контрольной, хранящейся . в этом случае в ячейке памяти первого разряда регистра теста 4. Несовпадение информации фиксируется с помощью обычного индикаторного устройства. При этом указывается на неисправность проверяемого узла по данному выходному каналу.

Подключение схем формирователей 6,7с. помощью переключателей 5 коММутатора Я выполненное в соответствии со схемой, показанной на чертеже, позволяет вдвое уменьшить число контактов 5 и вдвое уменьшить число элементов регистра теста 4. При этом очевидно, что информация в регистре теста не будет разделена на самостоятельные массивы входной и выходной контрольной информации. Запись ее будет производиться в

регистр с числом разрядов, равным числу входов-выходов проверяемого узла, в порядке, соответствующем расположению входоввыходов на самом узле.

Предмет изобретения

Многоканальное устройство тестового контроля цифровых узлов ЭВМ, содержащее запоминающее устройство для хранения тестов, регистр теста, устройство записи информации из за1поминающего устройства в регистр теста, формирователи выходных и входных сигналов, коммутационное устройство и устройства сравнения, .отличающееся тем, что, с целью упрощения устройства, запоминающая ячейка любого из разрядов регистра теста подключена через выходной формирователь и переключатель коммутационного устройства и через параллельно включенные им схему совпадения и входной формирователь к входному контакту проверяемого цифрового узла.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1980 |

|

SU888127A1 |

| Многоканальное устройство тестового контроля цифровых узлов ЭВМ | 1983 |

|

SU1179347A2 |

| Устройство для контроля цифровых узлов | 1981 |

|

SU1013960A1 |

| Многоканальное устройство тестового контроля цифровых узлов электронных вычислительных машин | 1977 |

|

SU656065A2 |

| Устройство для тестового контроля цифровых узлов цифровой вычислительной машины | 1975 |

|

SU618742A1 |

| Устройство для тестового контроля цифровых узлов электронно-вычислительных машин | 1981 |

|

SU993266A2 |

| Устройство для функционального контроля цифровых блоков | 1983 |

|

SU1196875A1 |

| Система централизованного контроля радиоэлектронных изделий | 1978 |

|

SU744481A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1136169A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

Даты

1973-01-01—Публикация