Изобретение отгюснтся к вычислительной технике.

Известные устройства для управления цифровыми вычислительпыми машинами., в операционных устройствах которых использована магазинная память, содержат регистр команд, соединенный с дешифратором кода операций и дешифратором адреса. Эти машины не ПОЗВОЛЯЮТ реализовать автоматический выбор адресности команд и обладают недостаточным быстродействием.

Цель изобретения - расширеиие функциональных возможностей устройства и увеличение его быстродействия.

Для этого предлагаемое устройство дополнительно содержит блок режима работы, а регистр команд выполнен В виде секций равной длины, число которых на единицу больше максимального для одной команды числа операндов. Выходы младшего разряда каждой секции и других разрядов первой секции (по числу секций) соединены с соответствующими входами блока режима работы.

Устройству придается такая конфигурация, которая обеспечивает возможность эффективного оперироваиия в режиме выборки операндов из магазина и в режиме выборки их из ОСНОВНОЙ памяти, а также в комбинированном режиме, при котором одни операнды для вывыиолняемой операции выбираются из основиой памяти, а другие - из магазина.

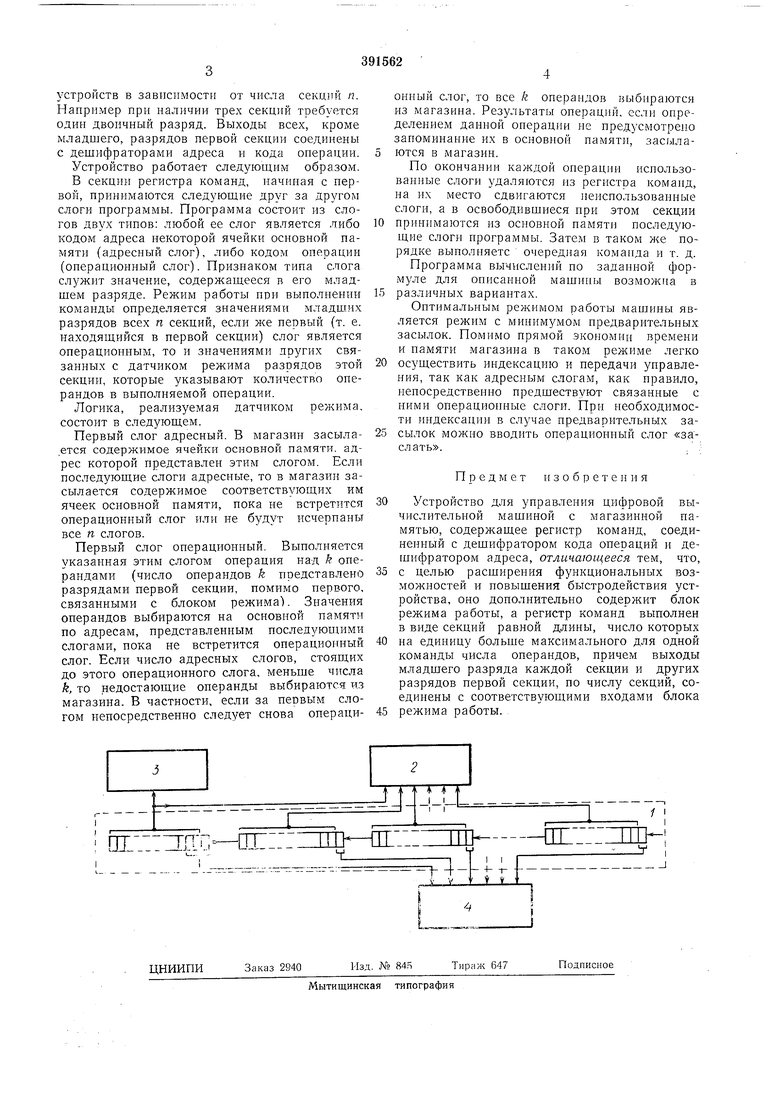

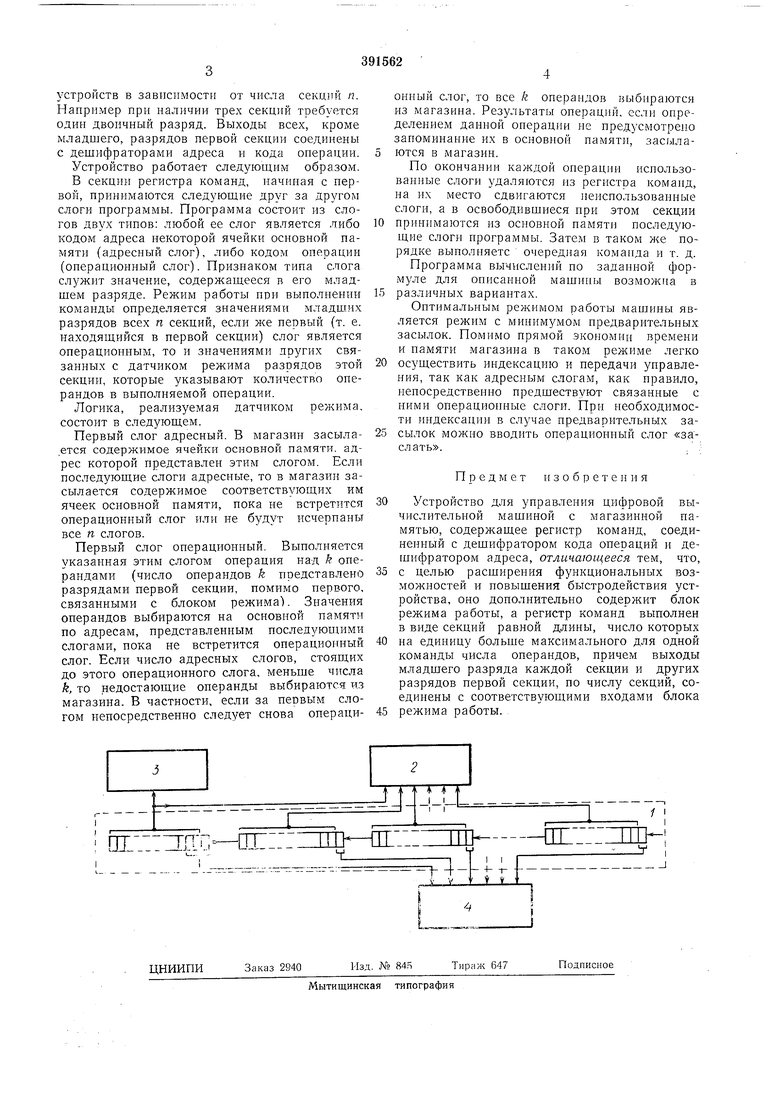

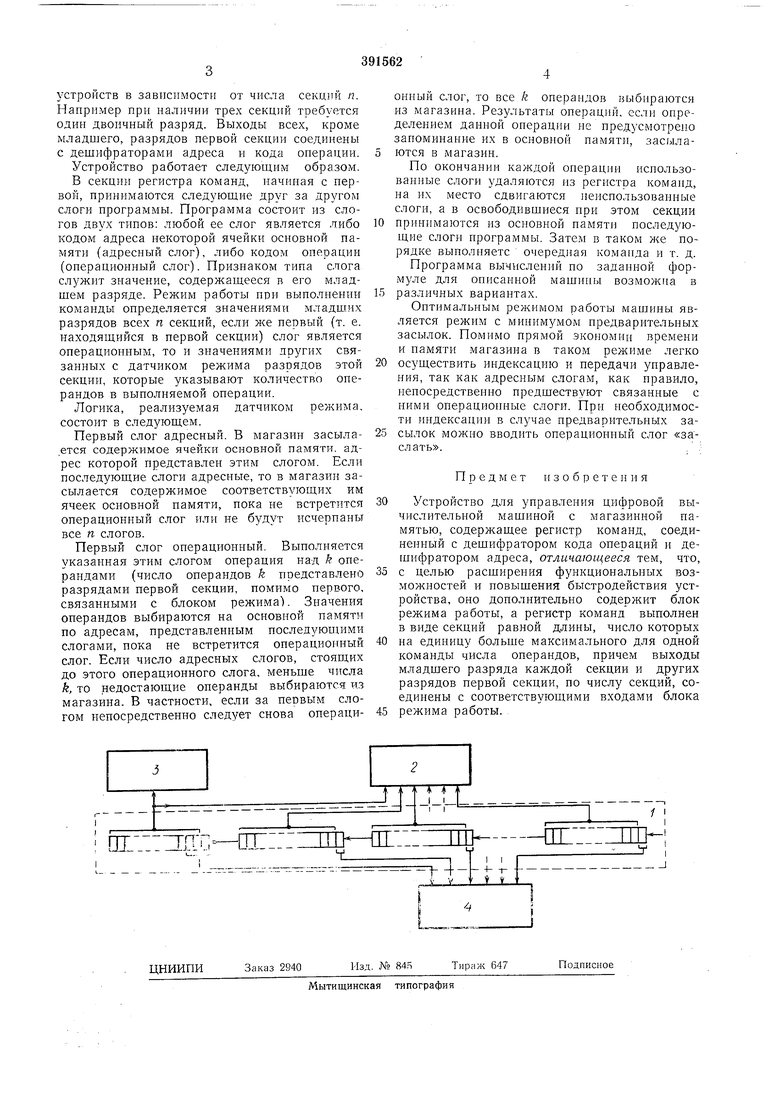

На чертеже представлена блок-схема описываемого устройства.

Оно содержит регистр комаид /, дешиф ратор адреса 2, дешифратор кода операций 3 и блок режима работы 4.

Регистр комаид выполнен в впде секций одинаковой длины, которая в конкретном вариаите выбирается в зависимости от установлеиного для данного устройства числа непосредствеиио адресуемых ячеек основной памяти. Секции соответствуют слогам, из которых состоит управляющая работой машины программа. Число секций в регистре на единицу больше числа операидов, допустимых в конкретиой машиие для одной операции. Например, В устройстве для управления машиной с одио-и двухместными операциями регистр комаид трехсекциоиный, а в машине,

выполияющей также трехместные операции,-четырехсекциоиный.

Конструкция всех секций, за исключением первой, одинакова. Это обычные запоминающие регистры, В каждом из которых выход

младшего разряда соединен с блоком режима работы 4, а выходы всех остальных разрядов - с дешнфратором адреса. В первой секции с датчиком режимов, помимо младшего разряда, соединены выходы еше нескольких разрядов, количество которых определяется для

устройств в зависимости от числа секций п. Например при наличии трех секций требуется один двоичный разряд. Выходы всех, кроме младшего, разрядов первой секции соединены с дешифраторами адреса и кода операции.

Устройство работает следующим образом.

В секции регистра команд, начиная с первой, принимаются следующие друг за другом слоги программы. Программа состоит из слогов двух типов: любой ее слог является либо кодом адреса некоторой ячейки основной памяти (адресный слог), либо кодом операции (операционный слог). Признаком типа слога служит значение, содержащееся в его младшем разряде. Режим работы при выполнении команды определяется значениями младших разрядов всех п секций, если же первый (т. е. находящийся в первой секции) слог является операционным, то и значениями других связанных с датчиком режима разрядов этой секции, которые указывают количество операндов в выполняемой операции.

Логика, реализуемая датчиком режима, состоит в следующем.

Первый слог адресный. В магазин засыла.ется содержимое ячейки основной памяти, адрес которой представлен этим слогом. Если последующие слоги адресные, то в магазин засылается содержимое соответствующих им ячеек основной памяти, пока не встретится операциоццый слог или не будут исчерпаны все п слогов.

Первый слог операционный. Выполняется указанная этим слогом операция над k операндами (число операндов k представ.леио разрядами первой секции, помимо первого, связанными с блоком режима). Значения операндов выбираются на основной памяти по адресам, представленным последующими слогами, пока не встретится операционный слог. Если число адресных слогов, стоящих до этого операционного слога, меньше числа k, то недостающие операнды выбираются из магазина. В частности, если за пепвым слогом непосредственно следует снова операционный слог, то все /г операндов выбираются из магазина. Результаты операций, если определением данной оиерации ие предусмотпеио запоминание их в основной памяти, засьшаются в магазин.

По окончании каждой операции использованные слоги удаляются из регистра команд, на их место сдвигаются неиспользованные слоги, а в освободивщиеся при этом секции

принимаются из основной памяти последующие слоги ирограммы. Затем в таком же порядке выполняете очередная команда и т. д. Программа вычислений по заданной формуле для описанной машины возможна в

различных вариантах.

Оптимальным режимом работы машины является режим с минимумом предварительных засылок. Помимо прямой экоиомии времени и памяти магазина в таком режиме легко

осуществить индексацию и передачи управления, так как адресным слогам, как нравило, непосредственно предшествуют связанные с ними операционные слоги. Прн необходимости индексации в случае предварительных засылок можно вводить операционный слог «заслать.

Предмет изобретен и я

Устройство для управления цифровой вычислительной машиной с магазинной памятью, содержащее регистр команд, соединенный с дешифратором кода операций и дешифратором адреса, отличающееся тем, что, с целью расширения функциональных возможностей и повышения быстродействия устройства, оно дополнительно содержит блок режима работы, а регистр команд выполнен в виде секций равной длины, число которых иа единицу больще максимального для одной команды числа операндов, причем выходы младшего разряда каждой секции и других разрядов первой секции, по числу секций, соединены с соответствующими входами блока режима работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Центральный процессор | 1980 |

|

SU890400A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| УСТРОЙСТВО Д,ПЯ УПРАВЛЕНИЯ СТЕКОВОЙ ПАМЯТЬЮ | 1970 |

|

SU284431A1 |

| Микропрограммный процессор | 1987 |

|

SU1553984A1 |

Авторы

Даты

1973-01-01—Публикация