1

Изобретение относится к автоматике и вычислительной технике и может найти применение в интегральных схемах регистров на МДП-транзисторах.

Известны схемы разряда регистра, вьгнолненные на МДП-транзисторах, например схема разряда регистра, который содержит шину питания, иагрузочные и логические транзисторы, попарно образующие два последовательно соединенных инвертора, охваченных Обратной связью с выхода на вход, и проходной транзистор, затвор -которого подключен .к шнне записи информации. Однако этим схемам свойственно невысокое быстродействие, вызванное длительным процессом заряда еМКостной нагрузки, особенно при выводе информации из микросхем.

Для уменьшения длительности переходных процессов на выходе применяют специальные буферные схемы иди увеличивают проводимость нагрузочного транзистора второго инвертора, поддерживая требуемое отношение крутизны нагрузочного и логического транзисторов этого инвертора. В этом случае увеличивается ток, потребляемый от источника питания в статическоМ режиме при низком уровне выходного напряжения, что приводит к ухудшению энергетических параметров разрядной ячейки.

Цель изобретения - улучшение электрических параметров схемы, а именно увеличение быстродействия разряда регистра, построенного на МДП-транзисторах.

Для достижения поставленной цели в известную схему введен дополн 1тельный МДПтранзнстор, включенный таким образом, что его СТ01К соединен с шиной литания, исток-с выходной шиной разряда, а затвор - с шиной записи информации.

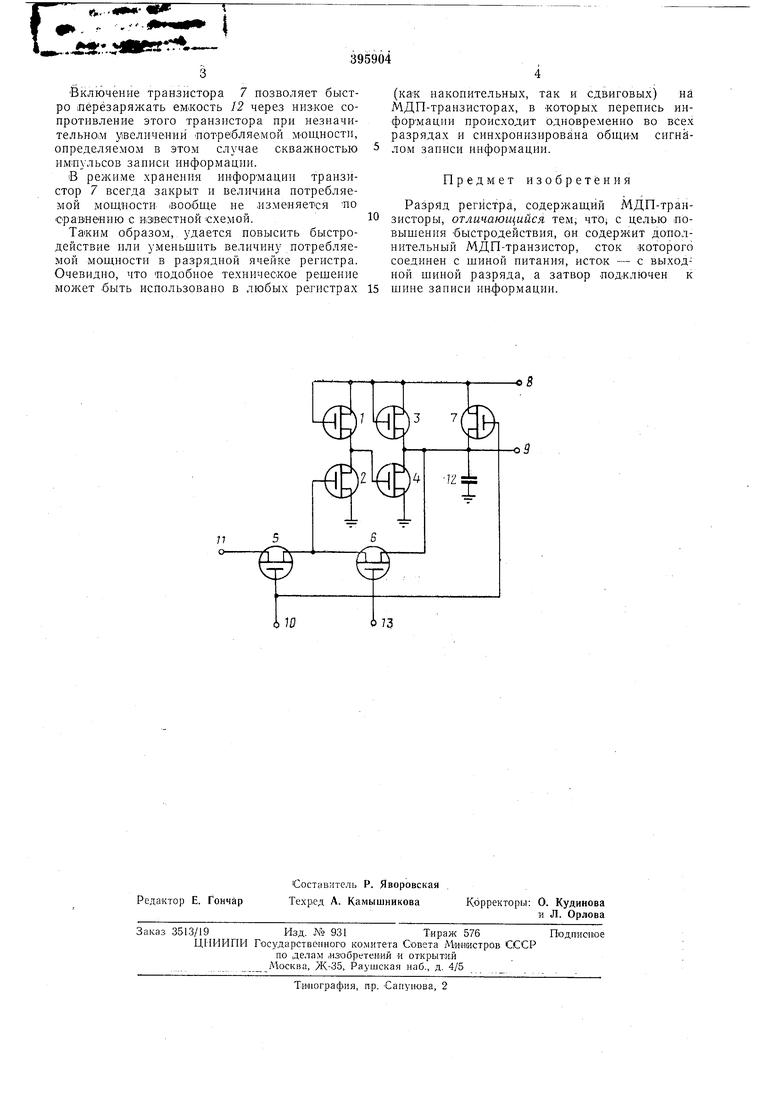

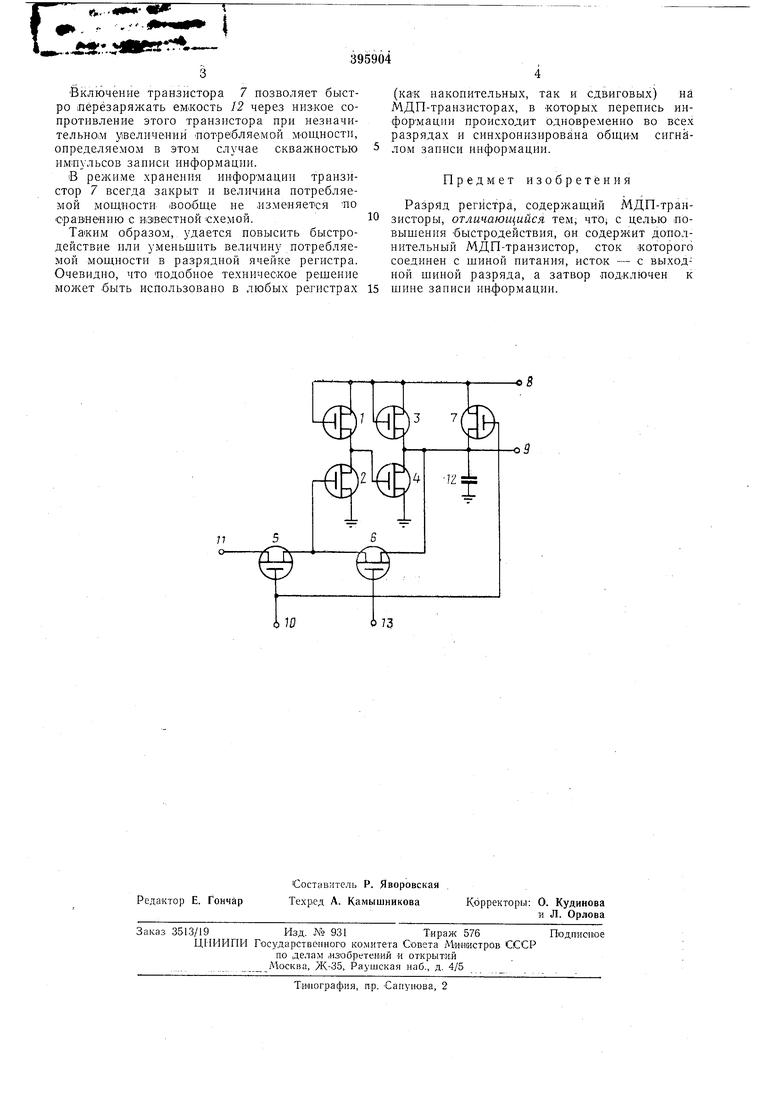

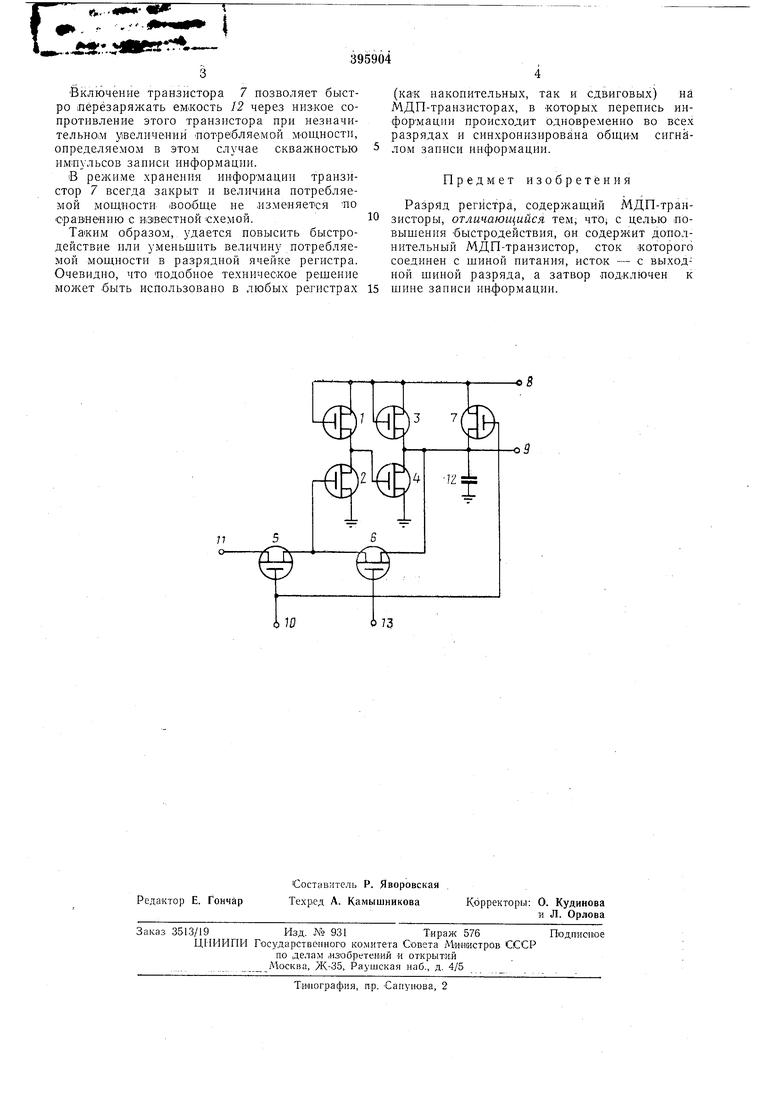

Па чертеже представлена предлагаемая схема разряда регистра.

Разряд регистра построен на полевых МДП-траизисторах /-6 (вообще схемное ipemaHiHe регистра может быть и .други1м). В него введен дополнительный МДП-транзистор 7, сток которого подключен « шине питания 8, исток - к выходной шине .9 разряда, а затвор соединен с шиной 10 записи информации.

Па чертеже также обозначены вход // разряда регистра; эквивалентная емкость 12, наГружаюшая выход разряда регистра, щина инверсных сигналов записи информации 13.

Запись входной информации в схеме осуществляется ири поступлении импульсов заппси на шину 10. При этом инверсный сигнал записи на шине 13 закрывает транзистор обратной связи 6 и входная информацня проходит через два инвертора, образоваииых транзисторами 1, 2 и 3, 4 на выход 9 ирн разомкнутой цепи обратной связи.

«- «....«Mi-ei

f .. ,

I..ttS-.jjeea Включение транзистора 7 позволяет быстро лерёзаряжать емкость 12 через низкое сопротивление этого транзистора при незначительной увеличении потребляемой МОШ,ности, определяемом в этом случае скважностью импульсов заинси информации. врежиме хранения информации транзистор 7 всегда закрыт и величина потребляемой мощности ( не изменяется ПО Сравяению с известной схемой. Таким образом, удается повысить быстродействие или уменьшить величину потребляемой мощности в разрядной ячейке регистра. Очевидно, что подобное техническое решение может быть использовано в любых регистрах

395904 (как накопительных, так и сдвиговых) на МДП-трапзисторах, в которых перепись информации происходит Одновременно во всех разрядах и синхронизирована общим сигналом записи информации. Предмет изобретения Разряд регистра, содержащий МДП-транзисторы, отличающийся тем, чтО; с целью повыщения -быстродействия, он содержит дополнительный МДП-транзистор, сток которого соединен с шиной питания, исток - с выходной шиной разряда, а затвор подключен к шине заииси информации.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

| Усилитель для запоминающего устройства | 1981 |

|

SU999103A1 |

| ДВУХКАСКАДНЫЙ ДИНАМИЧЕСКИЙ СДВИГОВЫЙ РЕГИСТР | 2014 |

|

RU2542898C1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

Авторы

Даты

1973-01-01—Публикация