1

Предложенная динамическая ячейка памяти относится к устройствам вычислительной техники и может быть использована в интегральных оперативных запоминающих устройствах.

Известна динамическая ячейка памяти, содержащая три МДП-транзистора, в которой сток первого транзистора подключен к истоку второго транзистора, стоки второго и третьего транзисторов подключены к разрядной шине, а затвор третьего транзистора - к адресной шине записи.

В известной ячейке памяти требуется трехуровневый сигнал на адресной шине, что усложняет управление ее работой.

Целью изобретения является устранение указанного недостатка, т. е. упрощение управления работой ячейки.

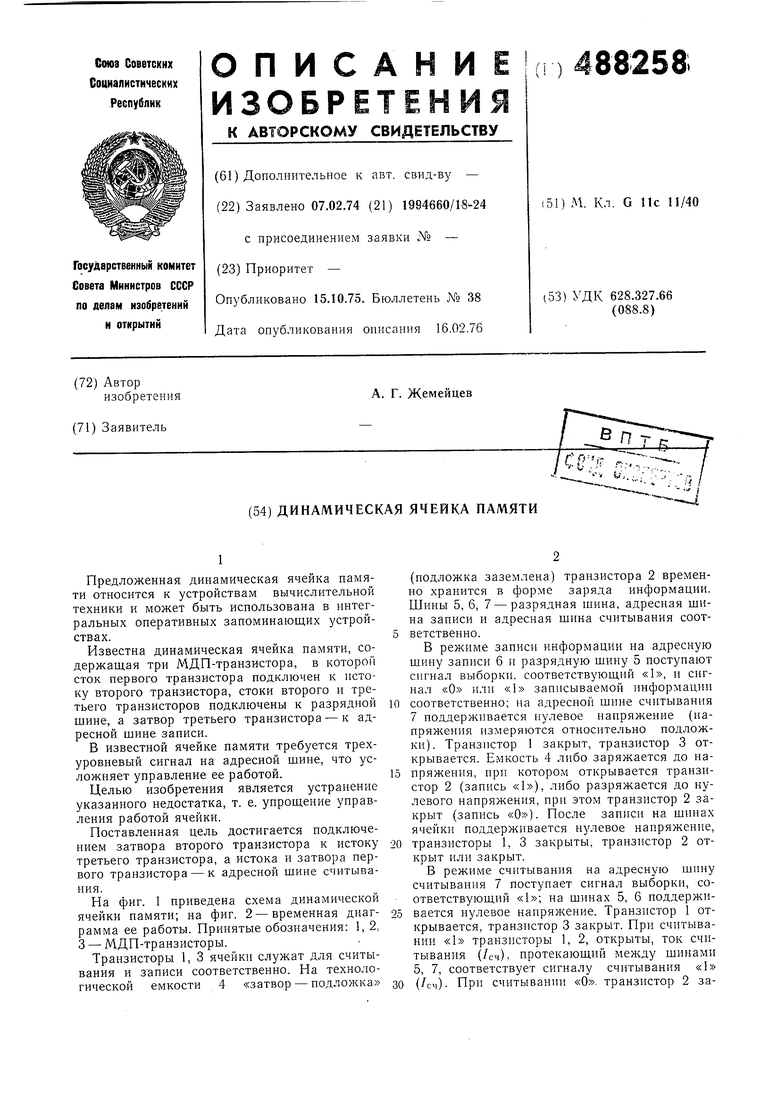

Поставленная цель достигается подключением затвора второго транзистора к истоку третьего транзистора, а истока и затвора первого транзистора - к адресной шине считывания.

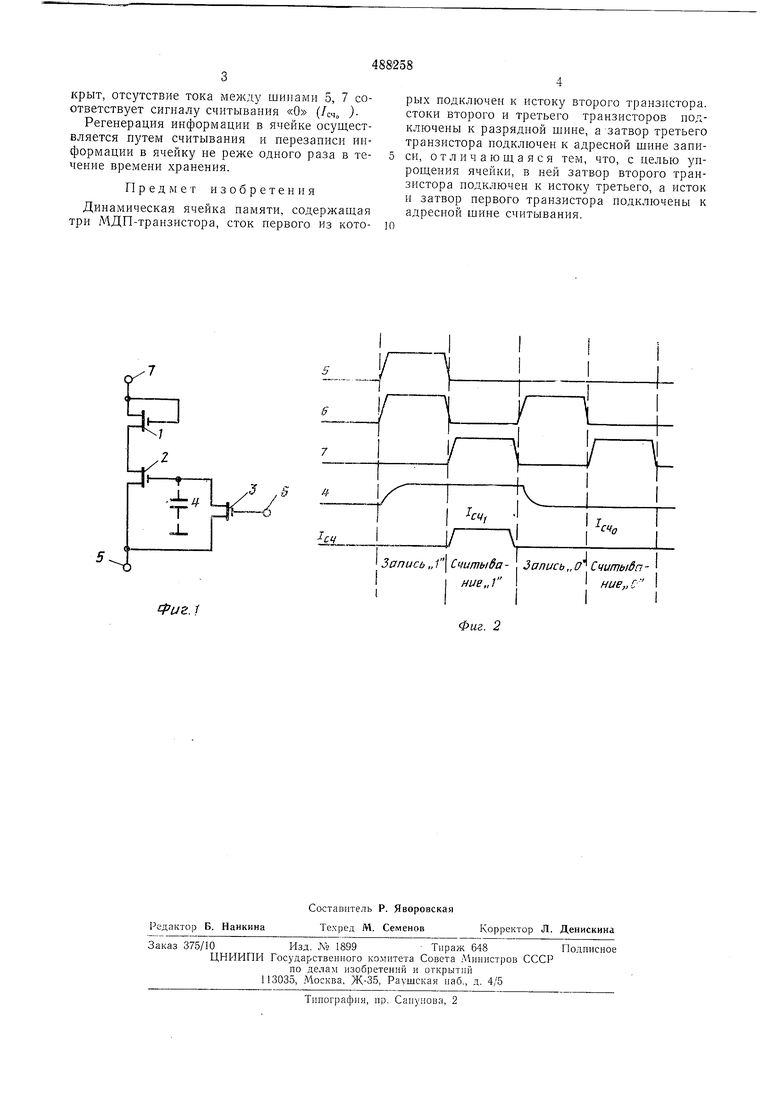

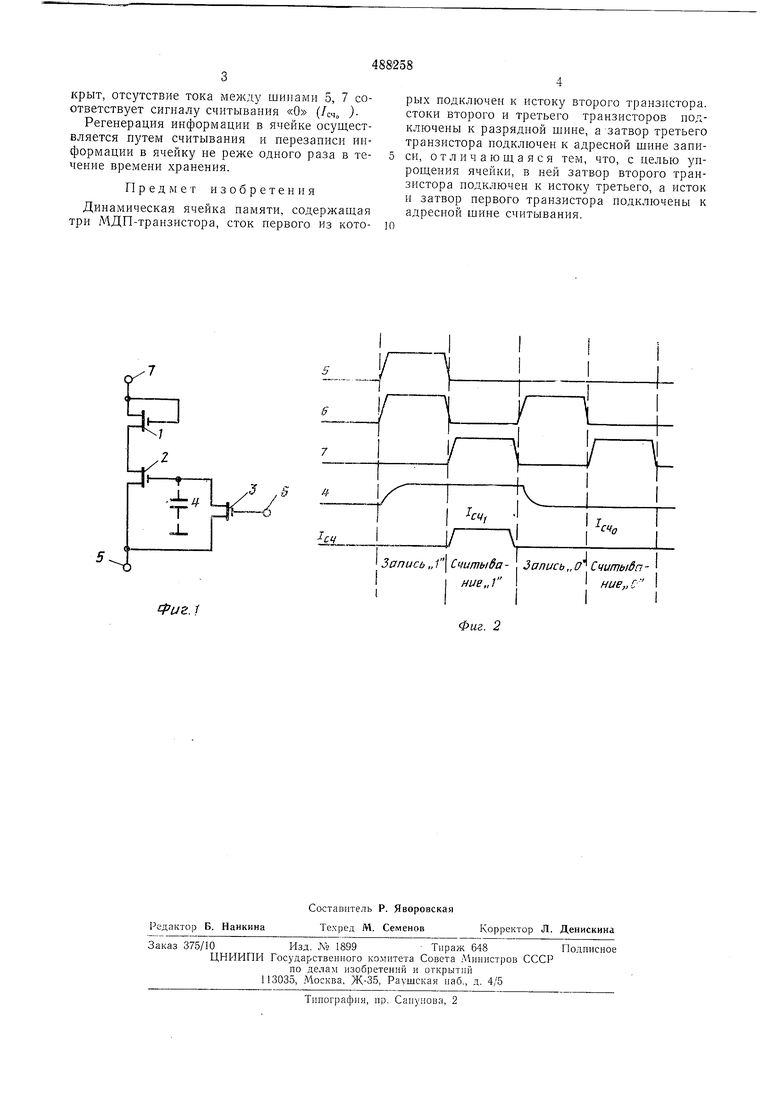

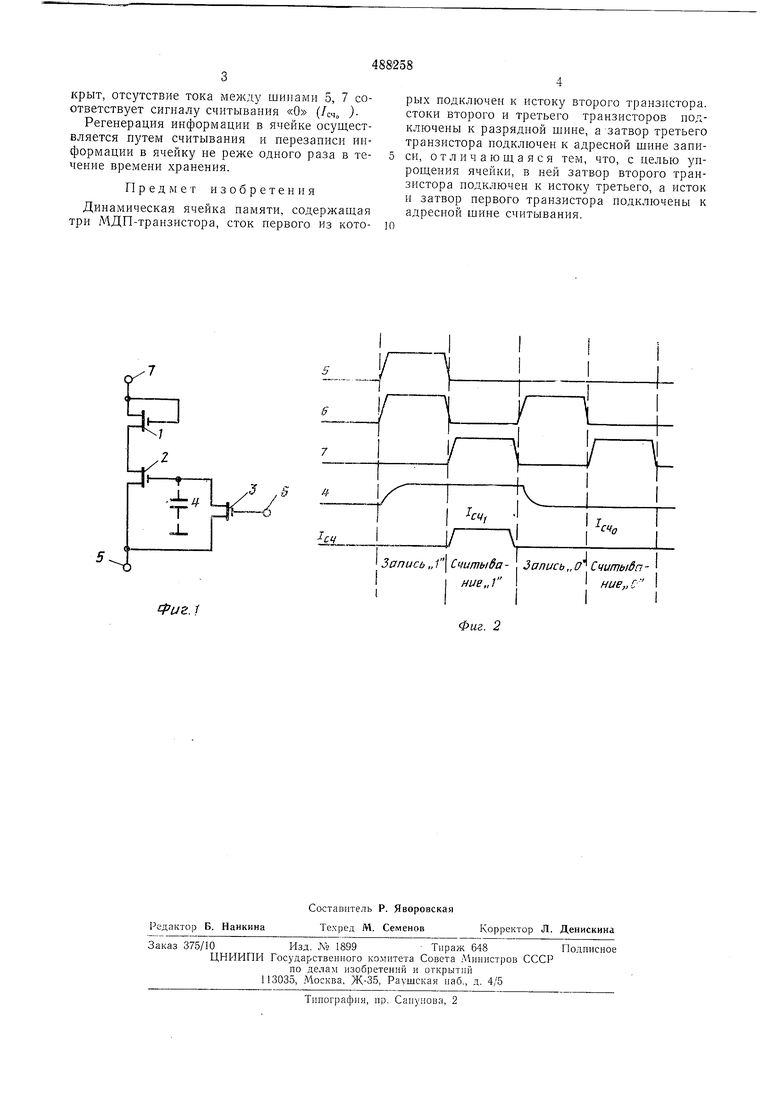

На фиг. 1 приведена схема динамической ячейки памяти; на фиг. 2 -временная диаграмма ее работы. Принятые обозначения: 1, 2, 3 - МДП-транзисторы.

Транзисторы 1, 3 ячейки служат для считывания и записи соответственно. На технологической емкости 4 «затвор - подложка

(подложка заземлена) транзистора 2 временно хранится в форме заряда информации. Шины 5, 6, 7 - разрядная шина, адресная шина записи и адресная шина считывания соответственно.

В режиме записи информации на адресную шину записи 6 и разрядную шину 5 поступают сигнал выборки, соответствуюший «1, и сигнал «О или «1 записываемой информации

соответственно; на адресной шине считывания 7 поддерживается нулевое напряжение (напряжения измеряются относительно подложки). Транзистор 1 закрыт, транзистор 3 открывается. Емкость 4 либо заряжается до напряжения, при котором открывается транзистор 2 (запись «1), либо разряжается до нулевого напряжения, при этом транзистор 2 закрыт (запись «О). После записи на шинах ячейки поддерживается нулевое напряжение,

транзисторы 1, 3 закрыты, транзистор 2 открыт или закрыт.

В режиме считывания на адресную шину считывания 7 поступает сигнал выборки, соответствуюш,ий на шинах 5, 6 поддерл ивается нулевое напряжение. Транзистор 1 открывается, транзистор 3 закрыт. При считывании «1 транзисторы 1, 2, открыты, ток считывания (/сч), протекающий между щинами 5, 7, соответствует сигналу считывания «1

(/сч). При считывании «О, транзистор 2 закрыт, отсутствие тока между шинами 5, 7 соответствует сигналу считывания «О (/сч„ )

Регенерация информации в ячейке осуществляется путем считывания и перезаписи информации в ячейку не реже одного раза в течение времени хранения.

Предмет изобретения

Динамическая ячейка памяти, содержащая три МДП-транзистора, сток первого из которых подключен к истоку второго транзистора, стоки второго и третьего транзисторов подключены к разрядной шине, а затвор третьего транзистора нодключен к адресной шине записи, отличающаяся тем, что, с целью упрощения ячейки, в ней затвор второго транзистора подключен к истоку третьего, а исток и затвор первого транзистора подключены к адресной шипе считывания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическая ячейка памяти | 1974 |

|

SU529485A1 |

| Динамическая ячейка памяти | 1974 |

|

SU488259A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| Ячейка памяти | 1974 |

|

SU537388A1 |

| Элемент памяти | 1990 |

|

SU1786508A1 |

| Динамическая ячейка на мдп транзисторах | 1973 |

|

SU478361A1 |

| Накопитель для запоминающего устройства | 1980 |

|

SU940238A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Накопитель для оперативного запоминающего устройства | 1986 |

|

SU1376118A1 |

| Матричный накопитель | 1980 |

|

SU942151A1 |

If иг. 1

Фиг. 2

Авторы

Даты

1975-10-15—Публикация

1974-02-07—Подача