I

Изобретение относится к области вычислительной техники и, В частности, может найти широкое .нр.именен,ие ири построении больших интегральных схем (БИС) ла МДП-структурах.

Известен логический элемент, содержащий логическую сборку и цепь тактирования на МДИ-транзисторах, в которой сток управляющего транзистора соединен через логическую сборку с :истокам,и нагрузочного и разделительного транаисторов, подключенных стоками соответственно к щ.ине .напряжения питания и .к истоку зарядного тр:анзистора, пр-ичем затворы .нагрузочного и зарядного транзисторов под1ключены к первой щине тактовых импульсов, а затворы управляющего и разделительного транзисторов - .ко втО|рой шине тактовых им пульсов.

Цель изобретения - увеличение быстродействия и уменьщение за.нимаемой схемой площади В интегральном исполнении.

Это достигается тем, что сток зарядного транзистора подключен к стоку нагр.узочного транзистора.

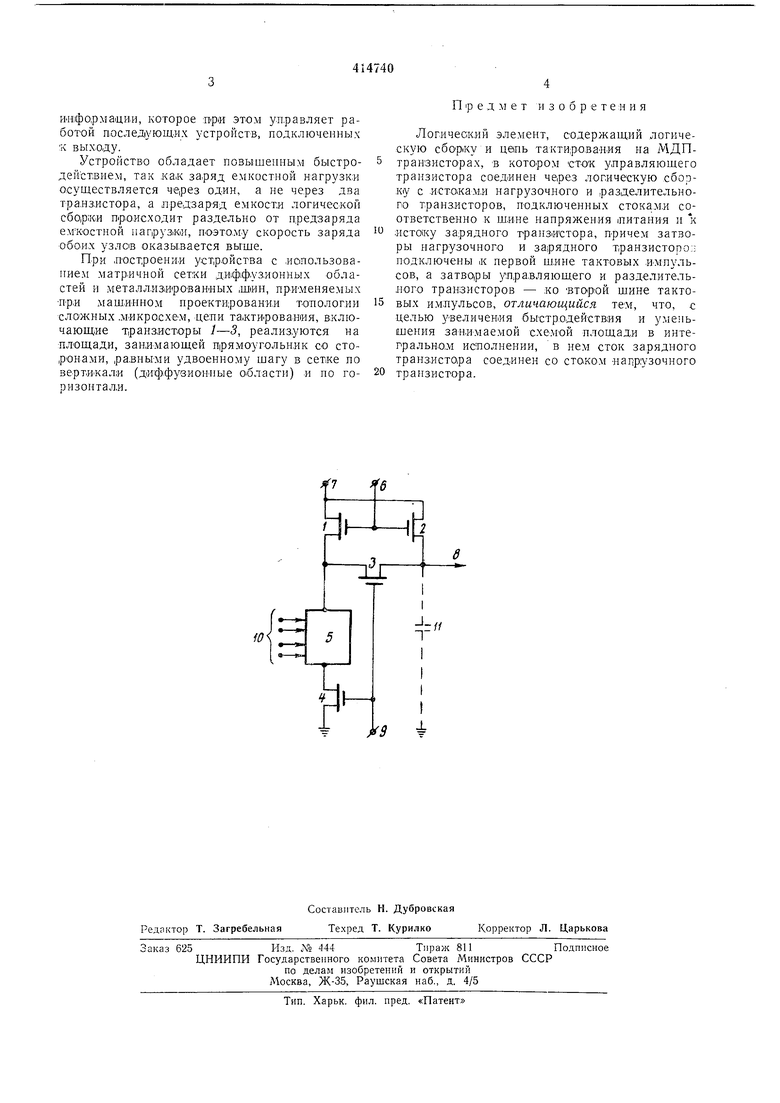

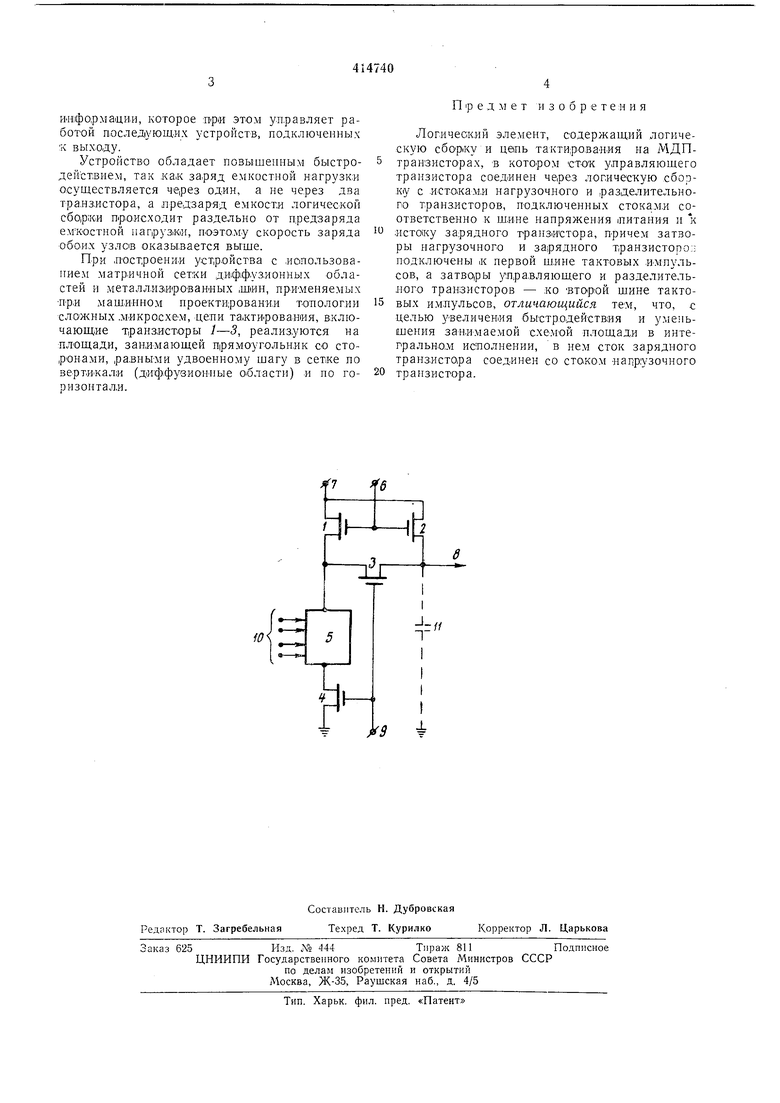

На чертеже иредставлена схема устройства.

Логический элемент соде|рж1ит МДП-транзисторы /-4 цепей тактирования и логическую сборку 5. Затворы нагрузочного / и зарядного 2 транзисторов соединены между собой и с щиной 6 тактовых импульсов. Стоки транзисторов / и 2 соедииены с шиной 7 источнвка питания, а его исток - с одним из ПОЛЮСОВ логической сборки 5 и со стоком разделительного транзистора 3, исток которого соединен с истоком транзистора 2 и с .выходом 8, а затвор - с щ;иной 9 тактовых импульсов и с затвором управляющего транзистора 4, cTOiK которого подключен ко второму логической сбор.ки 5, а исток - к общей шине. Логический элемент та.кже содержит обоощенный ВХОД 10 и емкостную нагрузку п.

Во время действия открывающего напряжения на затворах травзисторо.в / .и 2 осуществляется предварительный заряд емкостной нагрузки // через зарядный тра 1зи1стор 2. Одновременный лредзаряд емкости логической сборки 5 через нагрузочный транзистор / поз.воляет исключ.ить э;ффбкт .перераспределения заряда ВО время следующего такта- та.кта лстанов.ки иН(формадии. когда открывающее напряжение на затворах транзисторов 3 я 4 осуществляет опрос состояния логической сборки 5. Б зависи.мости от того, замкнута она или разомкнута ,происходит разряд емкостной нагрузки // или па ней сохраняется ВЫСОКИЙ .уровень .на пряження.

При отсутствии импульсов на шинах 6 и 9 на выходе 8 сохраняется записанное значение

Информааи.и, которое при этом ул.равляет работой послед|ующих устройств, подключенных к вых.оду.

Устройство обладает повышенным быстродействием, так KHiK за.ряд емкостной нагрузк:и осуществляется через один, а не через два тра.нз.истора, а лредзаряд емкости логической сборки происходит раздельно от предзаряда ем костной iiarpysiKiH, поэтому скорость заряда обоих узлсв оказывается выше.

При Лостроеии-и устройства с .использованием матр.ичной сетки диффузионных областей н металл.изированных шин, применяемых пр,и машинном проектировании топологии .микросхем, цели та.ктирования, включающие транзисторы 1-5, реализуются на площади, занимающей прямоугольник со сторонами, равными удвоенному шагу в сетке по верти-кали (диффузионНые области) и по горизонтали.

Пред м е т изобретения

Логический элемент, содержащий логическую сбор|Ку и цепь тактирования на МДПтранзисторах, в котором сток управляющего транзистора соединен через логическую сборку с исто.ками нагрузочного и разделительного транзисторов, подключенных стока.ми соответственно к шине напряжения литания и к истоку зарядного транзистора, причем затворы нагрузочного и зарядного транзисторол подключены к первой шине тактовых импульсов, а затворы управляющего и разделительного транзисторов - ко второй щине тактовых имлульсов, отличающийся тем, что, с целью увеличения быстродействия и уменьшения занимаемой схемой площади в интегральном исполнении, в нем сток зарядного транзистора соединен со стоком нагрузочного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Электронный ключ на мдп транзисторах | 1974 |

|

SU500588A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Триггер на мдп-транзисторах | 1977 |

|

SU641633A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Триггер на МДП-транзисторах | 1985 |

|

SU1330654A1 |

| Ячейка памяти на МДП транзисторах | 1981 |

|

SU968854A1 |

| Усилитель считывания | 1980 |

|

SU938316A1 |

±

Авторы

Даты

1974-02-05—Публикация

1972-07-12—Подача