(54) УСИЛИТЕЛЬ СЧИТЫВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Усилитель считывания | 1980 |

|

SU951390A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Полупроводниковое запоминающее устройство | 1979 |

|

SU879651A1 |

| Усилитель считывания для запоминающего устройства | 1981 |

|

SU985826A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Формирователь импульсов записи | 1985 |

|

SU1297114A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

1

Изобретение относится к вычислитеп&, ной технике и может быть использовано для создания запоминающих устройств на МДП-транзисторах и ПЗС.

Известны усилители считывания, предназначенные для считывания информации из накопителей, выполненных на однотранзисторных запоминающих элементах, работающие от предварительного заряда числовых щин и содержащие информаци- Q онные транзисторы и транзисторы связи 1.

Однако эти усилители рассеивают больщую мощность, так как в гфоцессе рабсугы через транзистор связи и информационный,5 транзистор, подключенный к узлу, в котором формируется уровень логического О, протекает сквозной ток.

Наиболее близким к гцэедлагаемому по технической сущности является усилитель 20 содержащий транзисторы связи, затворы которых подключены к первой тактовой щине, исток первого из которых соединен со стоком первого разрядного транзистора и затвором первого управляющего транзистора, исток BTqporo транзистора связи со стоком второго транзистора раддода и затвором второго ущэавляющего.транзистора, стоки угфавляющих транзисторов подключены к второй тактовой щине, исток первого управляющего транзистора соединен со стоком первого, затвором второго нагрузочных транзисторов и с 3aTBqpoM BTqporo транзистора разряда, исток второго утфавляющего транзистора соединен со стоком , затвором первого нагрузочных транзисторов и с затвором первого транзнerqpa разряда, истоки нагрузочных транзисторов подключены к щине нулевого потенциала, числовые щвны 2.

Данный усилитель счвтывавия работает от щюдеарительного числовых щин, обладает высхжой 4yBCTBifrenbностью, высоким быстродействием и малым потреблением мощности.

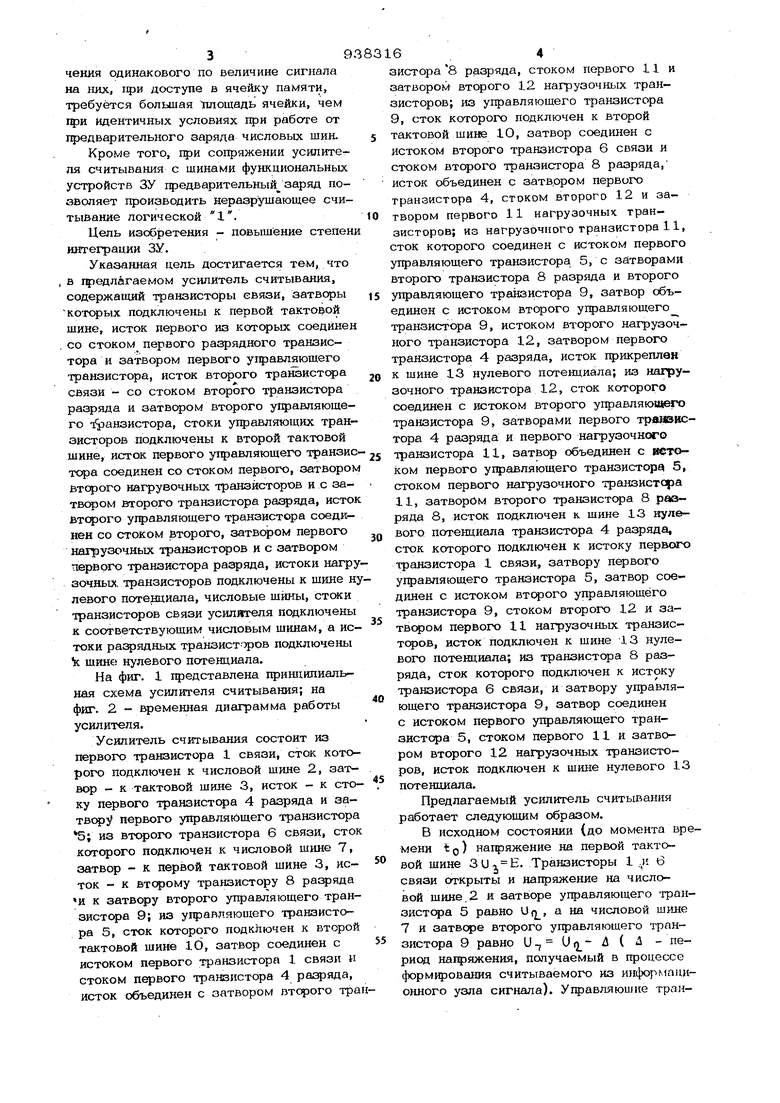

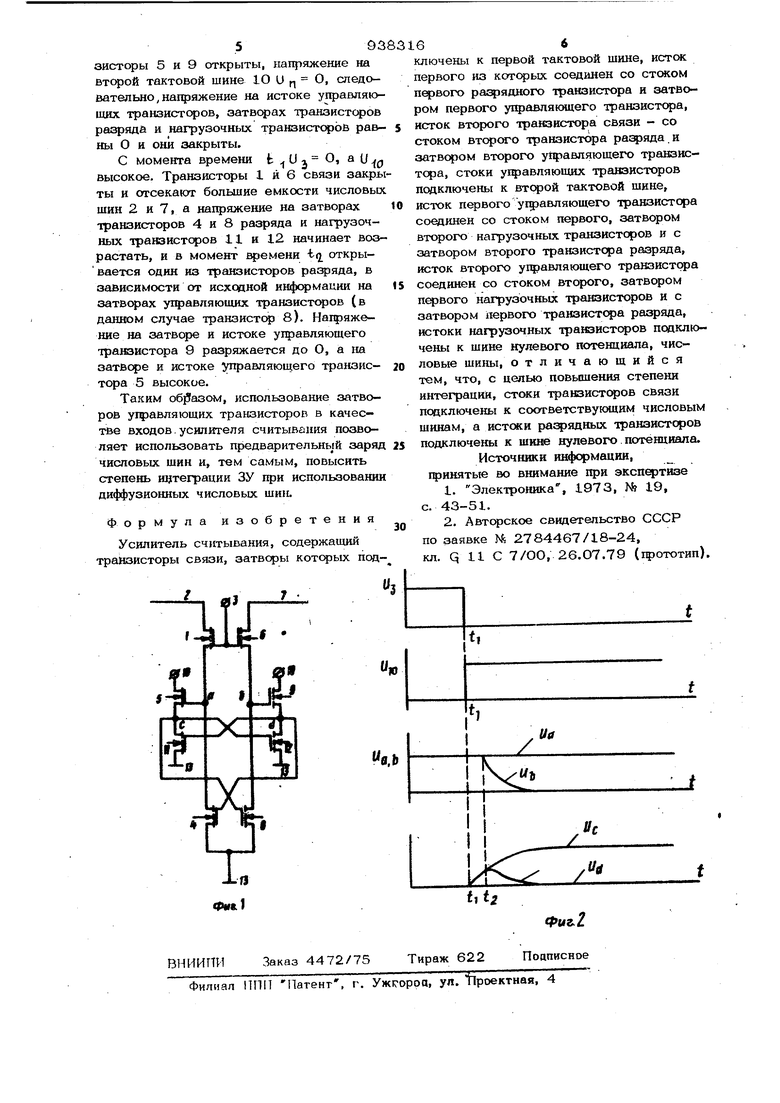

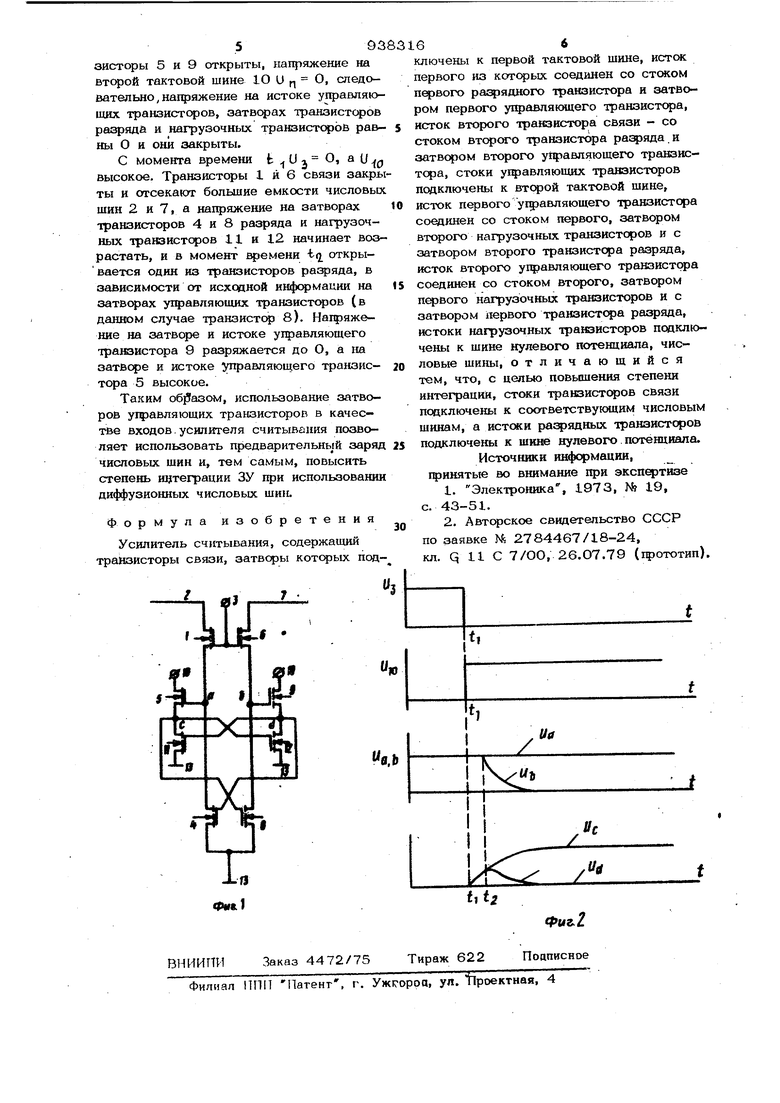

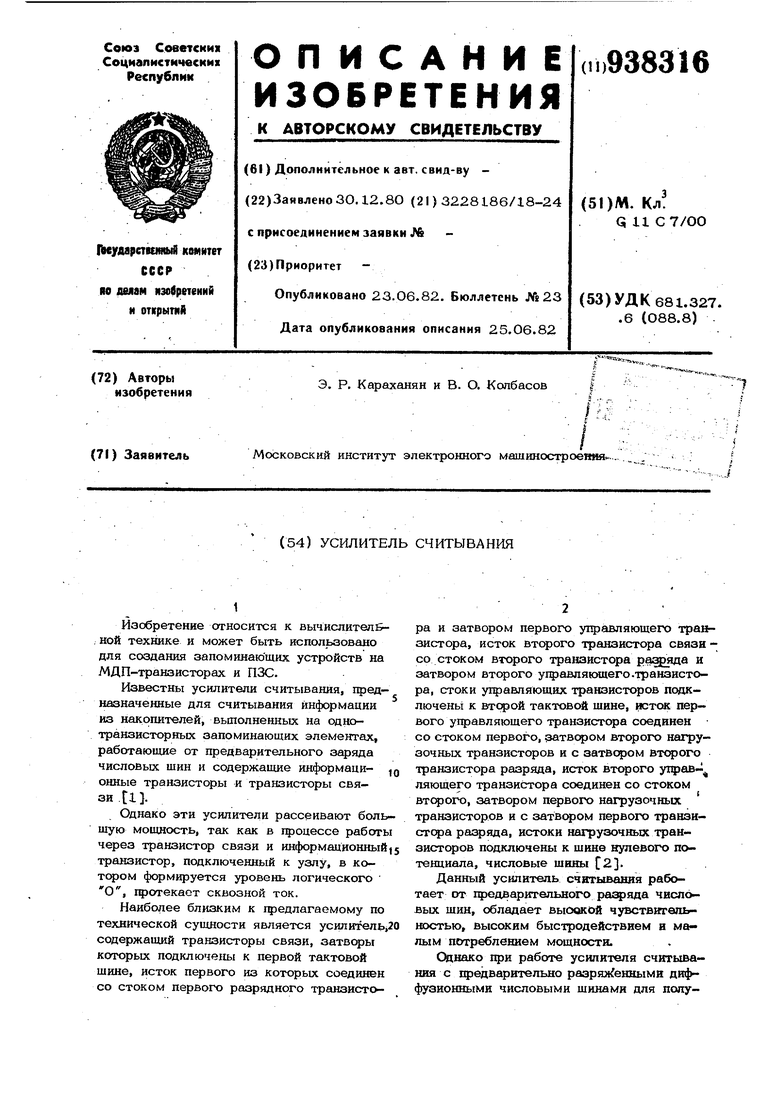

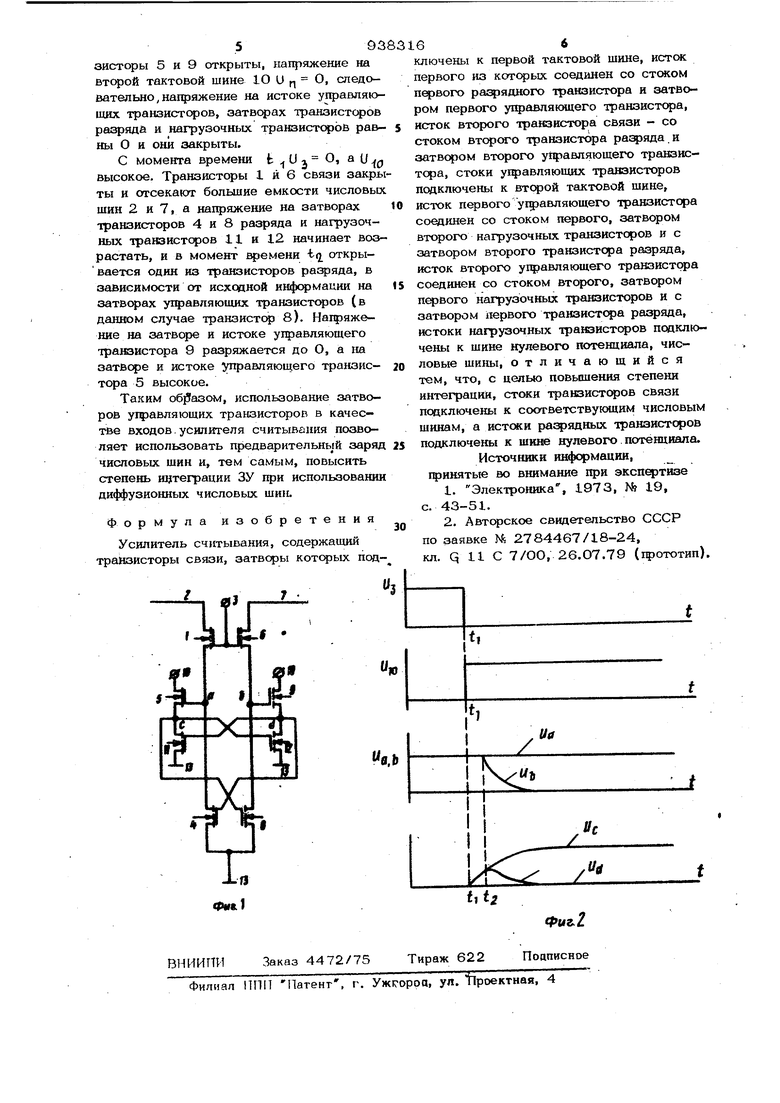

Опнако при работе усилителя считывания с щэедварительно разряя еннымн ди4 фузионными числовыми щинами для попу39чения одинакового по величине сигнала на 1ШХ, rqjH доступе в ячейку памяти, требуется большая площадь ячейки, чем iqjH Идентичных условиях при работе от предварительного заряда числовых шин. Кроме того, Щ)К сопряжении усилите ля считывания с шинами функциональных устройств ЗУ щзедварительный заряд позволяет производить неразрушающее считывание логической 1. Цель изобретения - повышение степен иш-еграции 3Y. Указанная цель достигается тем, что , в Г5 едлйгаемом усилитель считывания, содержащий транзисторы связи, затворы которых подключены к первой тактовой шине, исток первого иа котсрых соединен . со стоком первого разрядного транзистора и затвором первого ущзавляюшего транзистора, исток второго транзистора связи - со стоком второго транзистора разр5ща и затвсфом второго управляющего -фанзистора, стоки управляющих транзисторов подключены к второй тактовой шине, исток первого угравляющего транзис тора соединен со стоком первого, затвором втсфого нагрувочных транзисторов и с затвором второго транзистора разряда, исто второго управляющего транзистора соединен со стоком BTOpoixD, затвором первого нагрузочных транзисторов и с затвором первого транзистора разряда, истоки нагр зочных, транзисторов подключены к шине н левого потенциала, числовые шины, стоки транзисторов связи усилителя подключены к соответствующим числовым шинам, а ис токи ра ядных транзисторов подключены k шине; нулевого потенциала. На фиг. 1 щзедставлена принципиальная схема усилителя считывашгя; на фиг. 2 - временная диаграмма работы усилителя. Усилитель считывания состоит из первого транзистора 1 связи, сток которого подключен к числовой шине 2, затвор - к тактовой шине 3, исток - к стоку первого транзистора 4 разряда и затвору первого управлянэшего транзистора 5; из второго транзистора 6 связи, сток которого подключен к числовой шине 7, затвор - к первой тактовой шине 3, исток - к втфому транзистору 8 и к затвору второго управляющего транзистора 9; из управляющего транзистора 5, сток которого подключен к второй тактовой шине 10, затвор соединен с истоком первого транзистора 1 связи и стоком первого транзистора 4 разряда, исток объединен с затвором второго тра 164 зистора 8 разряда, стоком первого 11 и затвором второго 12 нагрузочных транзисторов; из управляющего транзистора 9, сток которого подключен к второй тактовой шине 10, затвор соединен с истоком второго транзистора 6 связи и стоком второго транзистора 8 разряда, исток объединен с затврром первого транзистора 4, стоком второго 12 и затвором первого 11 нагрузочных транзисторов; из нагрузочного гранзистора 11, сток которого соединен с истоком первого управляющего транзистора 5, с зйтворами второго транзистора 8 разряда и второго управляющего TpaksHCTOpa 9, затвор объединен с истоком второго управляющего транзистора 9, истоком второго нагрузочного транзистора 12, затвором первого транзистора 4 разряда, исток прикреплен к шине 13 нулевого потенциала; из нагрузочного транзистора 12, сток которого соединен с истоком второго управляюще1Х) транзистора 9, затворами первого трвавистора 4 разряда и первого нагрузочного транзистора 11, затвор объединен с ветоком первого ухфавляющего транзистору 5, стоком первого нагрузочного транзистора 11, затвором второго транзистора 8 раг ряда 8, исток подключен к шине 13 нулевого потенциала транзистора 4 разр5вда, сток которого подключен к истоку первого транзистора 1 связи, затвору первого ущэавляющего транзистора 5, затвор соединен с истоком управляющего транзистора 9, стоком второго 12 и затвором первого 11 нагрузочных транзисторов, исток подключен к шине 13 нулевого потенциала; из транзистора 8 разряда, сток которого подключен к истоку транзистора 6 связи, и затвору управляющего транзистора 9, затвор соединен с истоком первого управляющего транзистора 5, стоком первого 11 и затвором второго 12 нагрузочных транзисторов, исток подключен к шине нулевого 13 потенциала. Предлагаемый усилитель считывания работает следующим образом. В исходном состоянии (до момента времени t Q) нащэяжение на первой тактовой шине 3U E. Транзисторы 1 ,и 6 связи открыты и напряжение на числовой шине.2 и затворе управляющего транзистора 5 равно Uq, а на числовой шине 7 и затворе второго управляющего транзистора 9 равно U-, Un- Л ( i - период напряжения, получаемый в процессе форм1фова1шя считываемого из информационного узла сигнала). Управляющие тракзисторы 5 и 9 открыты, напряжение на втсрой тактовой шине Ю U О, следовательно , нагфяжение на истоке управляющих транзистс ов, аатвярах транзисторов разряда и нагрузочных транзистс ов равны О и они закрыты. С момента времени , ay.высокое. Транзисторы 1 и 6 связи закры ты и отсекают большие емкости числовы шин 2 и 7, а напряжение на затворах транзисторов 4 и 8 разряда и нагрузочных транзисторов 11 и 12 начинает воз растать, и в момент времени открывается один из транзисторов разряда, в зависимости от исходной информации на затвфах угфавляющих транзистс ов (в данном случае транзистс 8). Напряжение на затворе и истоке управляющего транзистора 9 разряжается до О, а на 3aTBqpe и истоке управляющего транзистора 5 высокое. Таким образом, использование затворов угравляющих транзисторов в качестве входов. усилителя считывания позволяет использовать предварительный заряд числовых щин и, тем самым, повысить степень интеграции ЗУ при использовании диффузионных числовых щин. Формула изобретения Усилитель считывания, содержащий транзисторы связи, затвсры которых подключены к первой тактовой щнне, исток первого из которых соединен со стоком пфвого ра ядного транзистора и затвором первого управляющего транзистора, исток второго транзистора связи - со стоком вторся о транзистора и 3aTBqpoM второго угфавляющего транзнстсра, стоки угфавляющих транзисторов подключены к втсрой тактовой шине, исток первого управляющего транзистора соединен со стоком первого, затвором второго нагрузочных транзисторов и с затвором второго транзистора разряда, исток второго управляющего транзистора соединен со стоком второго, затвором п фвого нагрузочных транзисторов и с затвором первого транзистора разряда, истоки нагрузочных трайзистс ов подключены к щине нулевого потенциала, числовые щины, отличающийся тем, что, с целью повьпиения степени интеграции, стоки транзисторов связи подключены к соответствуквдим числовым щинам, а истоки раг ядных транзисторов подключены к шине нулевого потенциала. Источники информации, щэинятые во внимание при экспертизе 1. Электроника, 1973, № 19, с. 43-51. 2.Авторское свидетельство СССР по заявке Ns 2784467/18-24, кл. q 11 С 7/ОО, 26.О7.79 (гфототип).

Wfl.I

Авторы

Даты

1982-06-23—Публикация

1980-12-30—Подача