I

Изобретение относится к импульсной технике, может быть использовано при построении цифровых интегральных схем на МДПтранзисторах.

Известен квазистатический триггер на МДП-транзисторах, содержащий ключевые траизисторы, причем сток и затвор ключевого транзистора одного плеча триггера соединены сЬответственно с затвором и стоком ключевого транзистора другого плеча триггера.

Недостатки известного устройства - низкое быстродействие, большой ток, коммутируемый в шине записи, н большая зона неопределенности состояния триггера (весь такт записи), во время которого нредьтдущая информация стирается.

Известен квазнстатическнй триггер на МДП-транзисторах, содержащий конденсатор хранения, тактовые шнны хранения и в каждом плече последовательно соединенные нагрузочный транзистор, сток и затвор кокоторого соединены с шиной питания, ключевой транзистор, сток и затвор которого соединены соответственно с затвором и стоком ключевого транзистора второго плеча, и управляющий транзистор в первом плече, а

во втором плече - два параллельно соединенных управляющих транзистора, у одного из которых затвор подключен ко входной шине, а у другого - к шине записи; истоки управляющих транзисторов подключены к общей щнне.

Это устройство сложно из-за наличия тактовых шин, занимающих значительную площадь кристалла при интегральном исполнении. Кроме того требуется определенная связь между тактовым импульсом и импульсом записи, что накладывает ограничение на его использование в асинхронных устройствах.;

Цель изобретения - упрощение триггера и расширение области его применения.

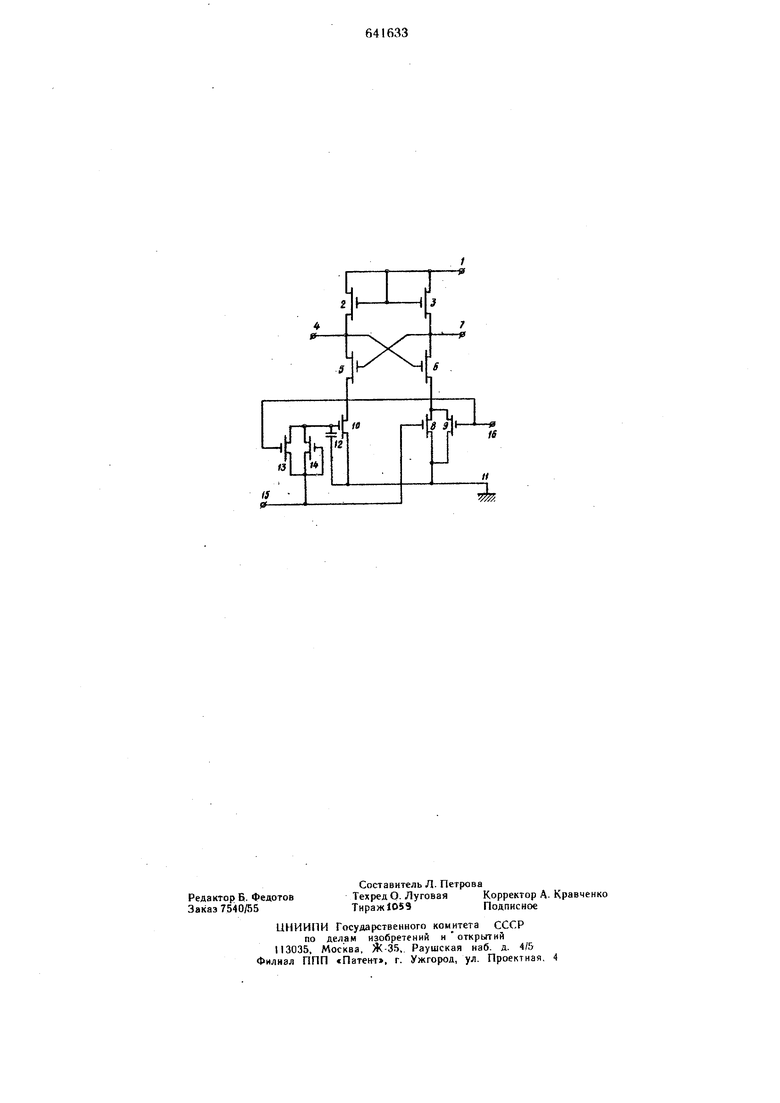

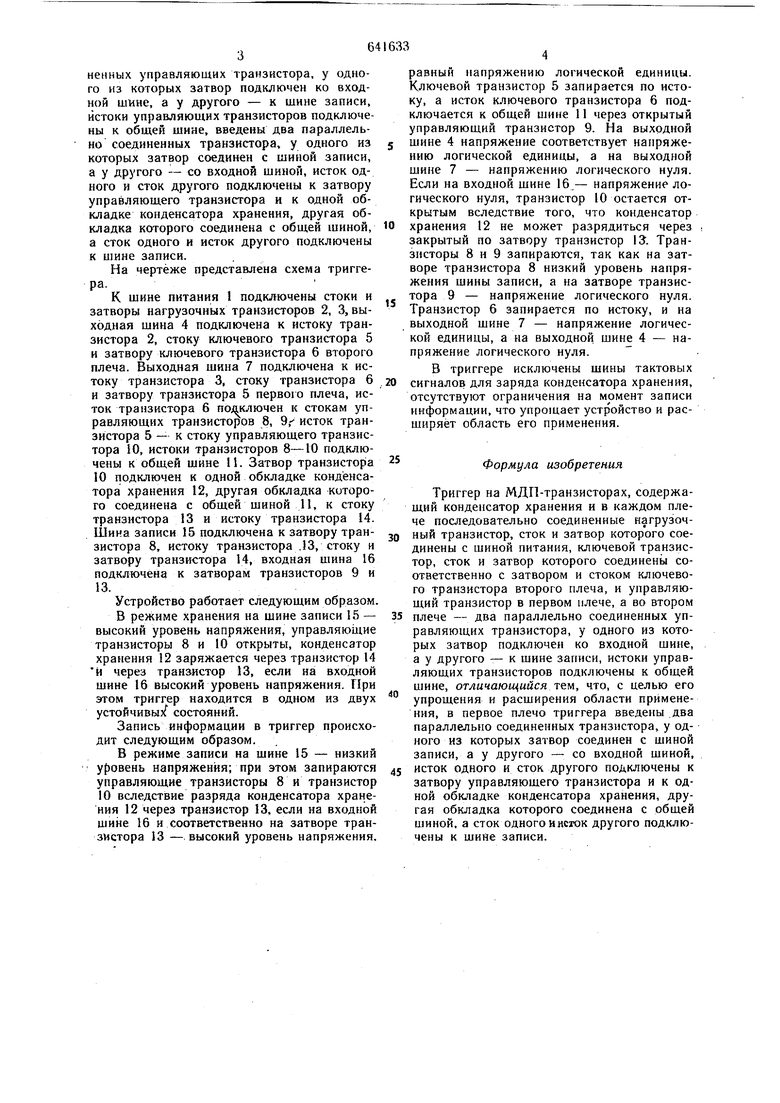

Для достижения поставленной цели в первое плечо триггера на МДП-транзисторах, содержащего конденсатор хранения и в каждом плече последовательно соединенные нагрузочный транзистор, сток и затвор которого соединены с шиной питания, ключевой транзистор, сток н затвор которого соединены соответственно с затвором н стоком ключевого транзистора второго плеча, и управляющий транзистор в нервом плече, а во втором плече - два параллельно соеднненных управляющих транзистора, у одного из которых затвор подключен ко входной шине, а у другого - к шине записи, истоки управляющих транзисторов подключены к общей шине, введены два параллельно соединенных транзистора, у одного из которых затвор соединен с шиной записи, а у другого - со входной щинон, исток одного и сток другого подключены к затвору управляющего транзистора и к одной обкладке конденсатора хранения, другая обкладка которого соединена с общей шиной, а сток одного и исток другого подключены к шине записи. На чертеже представлена схема триггера. К шине питания 1 подключены стоки и затворы нагрузочных транзисторов 2, 3, выходная щина 4 подключена к истоку транзистора 2, стоку ключевого транзистора 5 и затвору ключевого транзистора 6 второго плеча. Выходная щина 7 подключена к истоку транзистора 3, стоку транзистора 6 и затвору транзистора 5 первою плеча, исток транзистора 6 подключен к стокам управляющих транзисторов 8, 9,- исток транзистора 5 - к стоку управляющего транзистора iO, истоки транзисторов 8-10 подключены к общей шине 11. Затвор транзистора 10 подключен к одной обкладке конденсатора хранения 12, другая обкладка которого соединена с общей шиной И, к стоку транзистора 13 и истоку транзистора 14. Шина записи 15 подключена к затвору транзистора 8, истоку транзистора .13, стоку и затвору транзистора 14, входная шина 16 подключена к затворам транзисторов 9 и 13. Устройство работает следующим образом. В режиме хранения на шине записи 15 - высокий уровень напряжения, управляющие транзисторы 8 и 10 открыты, конденсатор хранения 12 заряжается через транзистор 14 И через транзистор 13, если на входной шине 16 высокий уровень напряжения. При этом триггер находится в одном из двух устойчивы) состояний. Запись информации в триггер происходит следующим образом. В режиме записи на шине 15 - низкий у)овень напряжения; при этом запираются управляющие транзисторы 8 и транзистор 10 вследствие разряда конденсатора хранения 12 через транзистор 13, если иа входной шине 16 и соответственно на затворе транзистора 13 - высокий уровень напряжения. равный напряжению логической единицы. Ключевой транзистор 5 запирается по истоку, а исток ключевого транзистора 6 подключается к общей шине 11 через открытый управляющий транзистор 9. На выходной шине 4 напряжение соответствует напряжению логической единицы, а на выходной шине 7 - напряжению логического нуля. Если на входной щине 16,- напряжение логического нуля, транзистор 10 остается открытым вследствие того, что конденсатор хранения 12 не может разрядиться через закрытый по затвору транзистор 13. Транзисторы 8 и 9 запираются, так как на затворе транзистора 8 низкий уровень напряжения щины записи, а на затворе транзистора 9 - напряжение логического нуля. Транзистор 6 запирается по истоку, и на выходной шине 7 - напряжение логической единицы, а на выходной шине 4 - напряжение логического нуля. В триггере исключены шины тактовых сигналов для заряда конденсатора хранения, отсутствуют ограничения на момент записи информации, что упрощает устройство и расширяет область его применения. Формула изобретения Триггер на МДП-транзисторах, содержащий конденсатор хранения и в каждом плече последовательно соединенные нагрузочный транзистор, сток и затвор которого соединены с шииой питания, ключевой транзистор, сток и затвор которого соединены соответственно с затвором и стоком ключевого транзистора второго плеча, и управляющий транзистор в первом плече, а во втором плече - два параллельно соединенных управляющих транзистора, у одного из которых затвор подключен ко входной шине, а у другого - к шине записи, истоки управляющих транзисторов подключены к общей шине, отличающийся тем, что, с целью его упрощения и расширения области применения, в первое плечо триггера введены .два параллельно соединенных транзистора, у одного из которых затвор соединен с шиной записи, а у другого - со входной щиной, исток одного и сток другого подключены к затвору управляющего транзистора и к одной обкладке конденсатора хранения, другая обкладка которого соединена с общей шиной, а сток одного и исток другого подключены к щине записи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер с раздельными входами | 1978 |

|

SU746874A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1348908A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Формирователь сигнала напряжения смещения подложки для интегральных схем | 1983 |

|

SU1149311A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Ячейка памяти для регистра сдвига | 1972 |

|

SU503295A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

Авторы

Даты

1979-01-05—Публикация

1977-02-18—Подача