1

Изобретение относится к области телеграфной связи, а именно к запоминающим устройствам аппаратуры передачи данных с автоматическим запросом ошибок.

Из1вестно запоминающее устройство, содержащее накопитель координатного типа с двумя формирователями управляющих сигналов, ВЫХОДЫ координат которого соответственно соединены с последовательно соединенными сборками, дещифраторами и счетчиками.

Цель изобретения - уменьшение количества требуемых адресов.

Для .этого в предлагаемое запоминающее устройство введен дополнительный формирователь управляющих сигналов, причем ко входу одного из формирователей управляющих сигналов и ко входу дополнительного формирователя управляющих сигналов подключены выходы лереключателя, к соответствующим входам которого .подключены выходы каждого дешифратора, а между выходами координат накопителя и соответствующими сборками включены ключевые схемы.

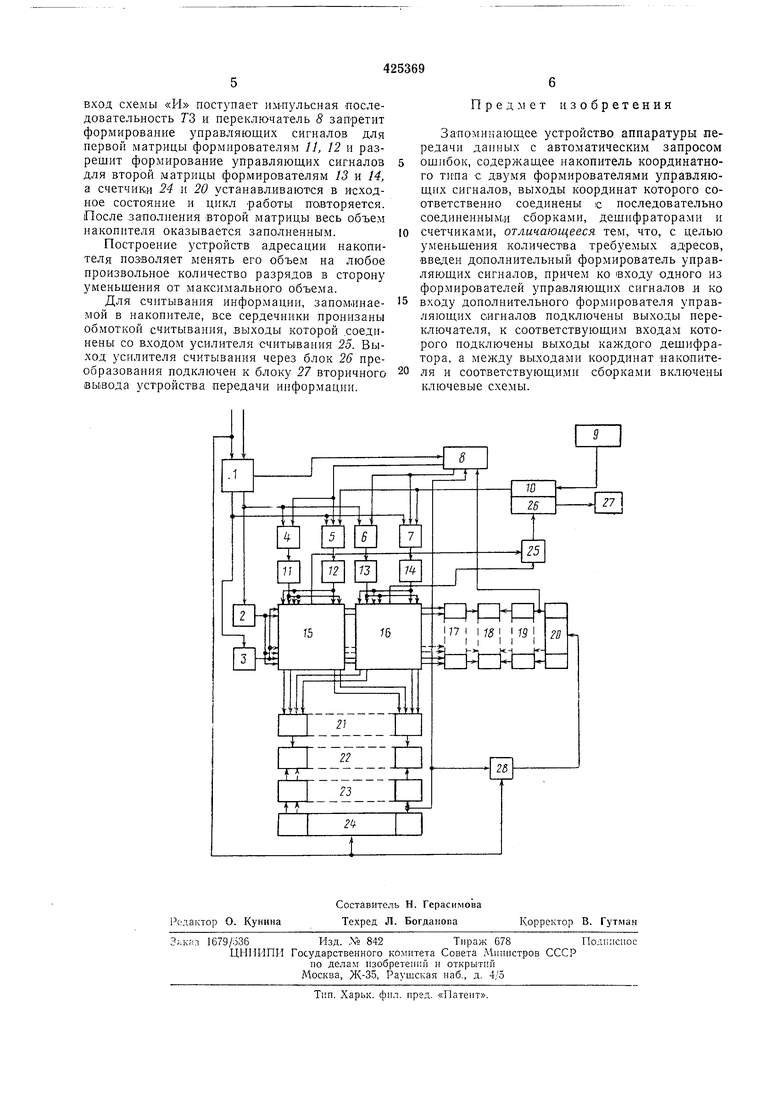

На чертеже при1ведена функциональная схема запоминающего устройства.

Выходы распределителя / подключены к формирователям 2 и 5 управляющих сигналов по оси У, к схемам «И 4-7 и ко входу переключателя 8. Выходы переключателя 8 подключены ко второму входу схем «И 4-7.

Третий вход схем «И 5 и 7 связан с, источником 9 кодовых комбинаций через -схелгу / ввода. Выходы схем «И 4-7 соединены с формирователями //-14 управляющих сигналов по оси Л . Формирователи 2 и 3 подключены к горизонтальным (ось f) шинам заИиси и матриц 15 и М, соединенным последовательно (на чертеже условно показаны первая, .вторая и последняя группа, ши))) с накопителем координатного типа. .Выходы шин соединены со сборками «ИЛИ П на два ахода каждая, выходы которых поступают на ключевые схемы «И IS.

На второй вход ключевой схемы «И поступают сигналы с дешифратора /9 состояний счетЧИка 20. Выходы вертикальных шин матриц /5 II /5 соединены со сборками «ИЛИ 21 на четыре входа, выходы которых подключены к ключевым схемам «И 22, v.z второй вход ключевых схем «И поступают сигналы с дешифратора 23 состояний счетчика 24. Обмотка считывания матриц подключена к усилителю считывания 25, выход которого соединен с блоком 26 преобразования. Выход блока преобразования подключен к блоку 27 вторичного вывода. Счетчики 24 и 20 соединены последовательно через схему «И 2S.

Тактовые импульсы высокой частоты и низкой частоты поступают на распределитель /, на выходе которого формируются импульсные последовательности Tl, Г2, 73, сдвинутые друг относительно друга на семь мксек.

Тактовые импульсы низ-кой частоты, кроме того, поступают на четырехразрядный счетчик 24 адресов.

iBecb объем накопителя координатного типа разделен на две матрицы 15 и 16 для упрощения схемы ,и уменьпления количества активных элементов. По оси Y шины чтения и записи матр,иц соединены последовательно. На вход форм.ирователя 2 поступает импульсная последовательность 71 с выхода распределителя /. Сформированный управляющий сигнал с выхода формирователя 2 .поступает параллельно на все шины чтения по оси Y.

На вход формирователя 3 поступает имлульсная последовательность Г2 с выхода распределнтеля /. Сформированный управляющий сигнал с выхода формирователя 3 поступает параллельно на все шины запнси по осн Y.

Д,ля формирования управляющего сигнала «Чтение XI для первой матрицы импульсная последовательность Г1 поступает на вход схемы «И 4, на другой вход которой поступает сигнЗиТ «Разрешение из переключателя 8.

С выхода схемы «И 4 сигнал поступает на вход формирователя // управляющего сигнала «Чтение Х. С выхода формирователя сигнал поступает параллельно на все .шины чтения первой матрицы.

Для формирования управляющего сигнала «Чтение Х2 .для второй матрицы им пульсная последовательность 71 поступает на вход схемы «iH 6, на другой вход которой поступает сигнал «Разрешение из переключателя 8. С выхода схемы «И 6 снгнал поступает на вход формирователя 13 управляющего сигнала «Чтение Х2.

С выхода формирователя сигнал .поступает на все шины чтения второй матрицы.

Для формирования сигнала «Запись XI для первой матрицы импульсная последовательность 72 с выхода распределителя поступает на вход схемы «И 5. На второй вход схемы «И 5 поступает сигнал «Разрешение из переключателя 8. На третий вход схемы «И 5 (Поступает скг.нал «Информация из источника 9 кодовых комбинаций через схему 10 ввода информации. С выхода схемы «И 5 сигнал поступает на в.ход формирователя /2, с выхода которого сфор.мированный снгнал «Запись XI поступает параллельно на все шины записи первой матрицы 15.

Для формирования сигнала «Запись Л2 для второй матрицы импульсная по-следовательность 72 с выхода распределнтеля / поступает на вход схемы «И 7. На второй вход схемы «И nocTjqiaeT сигнал «Разргшенне из переключателя и. На третий вход схемы «PI 7 .поступает сигнал «Информация из лсточника 9 кодовых комбинаций через схему W ввода информации. С выхода схемы «И 7 сигнал посту.пает па вход формирователя 14, с выхода которого сформированный сигнал «Запись

Х2 поступает параллельно на все шины записи второй матрицы 16.

Такое построение устройств формирования управляющих сигналов иозволяет отказаться

от использования обмоток компенсацин в матрицах, что значительно улучшает помехоустойчивость и снижает требования к схеме усилителя воспроизведения, а также .позволяет значительно упростить устройство адресации.

Для формирования адресов Л первой и второй матриц тактовые импульсы иизкой частоты .поступают .на вход -счетчика 24. Выходы разрядов счетчика 24 поступают в дешифратор 23. Сигналы с выходов дещифраторов 23 поступают на ключевые схемы «И 22. Количество разрядов счетчика, схем «И в дешифраторе и ключевых схем определяется количеством столбцов X одной матрицы.

Шины «Заиись и «Чтение XI первого столбца матр.ицы 15 соедииены со сборкой «ИЛИ 21, на четыре входа для каждого столбца X. На другие два входа поступают шины «Запись и «Чтение XQ первого столбца матрицы 16. Объединенный сигнал с выхода сборки «ИЛИ 21 поступает на ключевые схемы «И 22. При наличии сигнала с дешифратора 23 ключевая схема открывается и создается цепь для прохождения сигналов

Q «Записи .и Чтевия по столбцу X в первую или вторую матр.ицу в зависимости от того, работают формирователи // и 12 или 13 и 14.

Аналогичным образом формируются адреса на оси У. Счетчик 20 адресов У соединен

с последовательио со счетчиком X через схему «И 28. На один вход схемы «,И 28 поступает последнее состояние счетчика 24 с дешифратора 23. На другой вход - тактовые импульсы низкой частоты. Таким образом после

Q заполнения счетчика 24 (т. е. отработки всех столбцов X) идет сигиал на переключение счетчика У. Выходы разрядов счетчика 20 поступают в дешифратор 19 счетчика. Сигналы с выходов дешнфратора 19 поступают на ключевые схемы «И 18. Количество разрядов счетчика, схем «И IB .дешифраторе и ключевых схем определяются количеством строк Y в матрице. Шины «Запись и «Чтение У матр.ицы 16 соединены со сборкой «ИЛИ /7 на

50 два входа для каждой из строк У. Объединенный сигнал с вывода сборки «ИЛИ 17 .поступает на ключевую схему «И 18. При налнчии сигнала с дешифратора 19 ключевая схема открывается и создается цепь для прохождения сигналов «Чтения и Записп по строке У.

Из всего количества сердечников только для одного произойдет суммирование управляющих сигналов. С приходом следуюшего такта низкой частоты счетчик переключится

60 и будет работать следующий сердечник. Носле To.ro, как полностью отработает первая матрица 15, т. е. досчитают до заполнения счетчики 24 и 20 на схему «И, расположенную в переключателе 8, поступают сигналы 65 переполнения счетч-иков 24 и 20, на третий

вход схемы «И поступает им-пульсная последовательность ГЗ и переключатель 8 запретит формирование управляющих сигналов для нервой матрицы формирователям }}, 12 и разрешит формирование управляющих сигналов для второй матрицы формирователям 13 и 14, а счетчики 24 и 20 устанавливаются в исходное состояние и цикл работы павторяется. После .заполнения второй матрицы весь объем накопителя оказывается заполненным.

Построение устройств адресации накопителя позволяет менять его объем на любое произвольное количество разрядов в сторону уменьшения от максимального объема.

Для считывания информации, запоминаемой в накопителе, все сердечники пронизаны обмоткой считывания, выходы которой соединены со в,ходом усилителя считывания 25. Выход усилителя считывания через блок 26 преобразования подключен к блоку 27 вторичного вывода устройства передачи информации.

Предмет изобретения

За-поминающее устройство аппаратуры передачи данных с автоматическим запросом ошибок, содержащее накопитель координатного типа с двумя формирователями управляющих сигналов, выходы координат которого соответственно соединены с последовательно соединенным и сборками, дешифраторами и счетчиками, отличающееся тем, что, с целью уменьшения количества требуемых адресов, введен дополнительный формирователь управляющих сигналов, причем ко входу одного из формирователей управляющих сигналов и ко входу дополнительного формирователя управляющих сигналов подключены выходы переключателя, к соответствующим входам которого подключены выходы каждого дешифратора, а между выходами координат накопителя и соответствующими сборками включены ключевые схемы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Буферное динамическое оперативное запоминающее устройство | 1989 |

|

SU1695388A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для отображения графической информации на экране газоразрядной индикаторной панели | 1987 |

|

SU1509986A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Устройство управления накопителями на магнитных дисках | 1982 |

|

SU1053143A1 |

| Запоминающее устройство с последовательным доступом | 1981 |

|

SU982084A1 |

Авторы

Даты

1974-04-25—Публикация

1971-12-23—Подача