I

Изобретение относится к вычислительной тех)ике ,и может быть использовано прн конструировании цифровых вычислительных устройств и систем .

Известно устройство управления цнф;ровой вычислительной машшны, .соде1рл аш,ее счетч.ик команд, регистр команд, регистр адреса, дешифраторы адресов X и Y, адресные .ключи, формирователи, блок памяти, ириемный регистр, узел формирования заииси, бло.к памяти .и регистр серил команд.

Для повышения быстродействия и со.кращения оборудования предлагаемое устройство содержит блок формирования последуюП1ей команды, входы которого соединены соответственно с выходом регистра серии команд и вторым л третьим входами устройства, а его выходы подключены соответственно к пер:вому и второму входам регистра ко.манд.

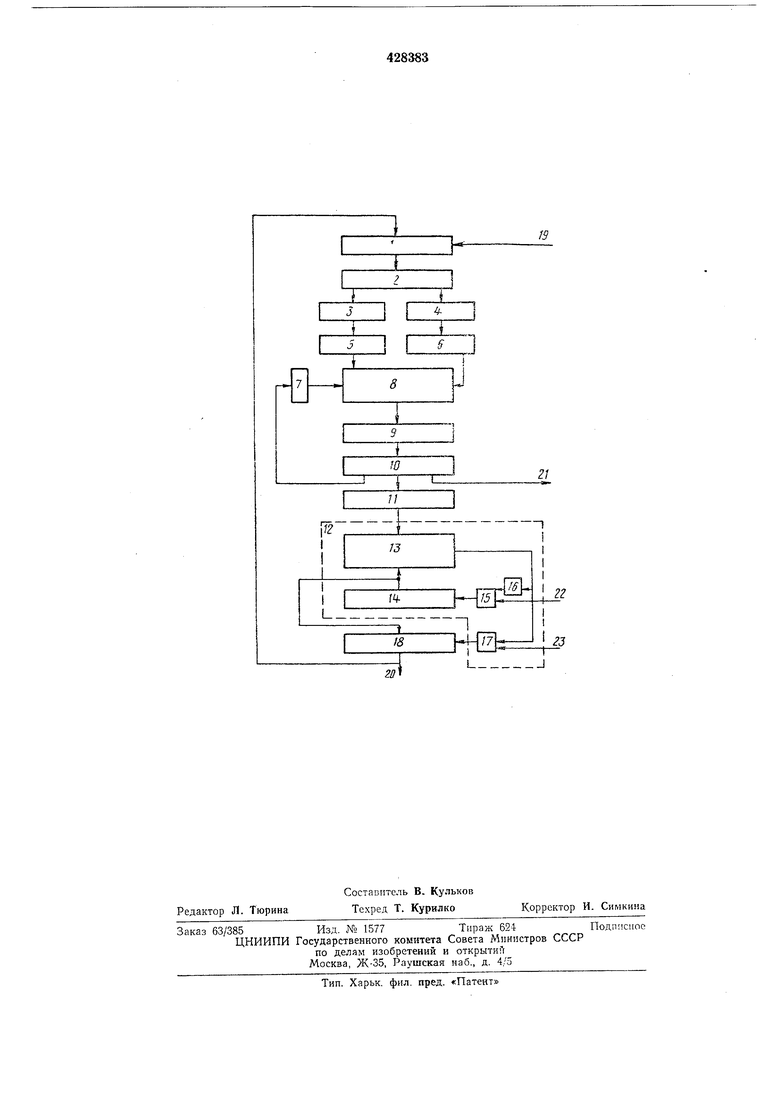

Схема предлагаемого устройства приведена на чертеже.

В состав устройства входят счетчик } команд, регистр 2 адреса, дешифратор 3 адреса X, дешифратор 4 адреса К, адресные ключи 5, адресные фор1мировател,и 6, узел 7 формирования загаиюи, блок 8 , усилители 9 считывания, прием ный регистр 10, регистр 11 серии команд, блок 12 форм ироваиия последлюи ей колтанды, состоящий из схемы 13

поразряд;гого сравнения, сдв|И1гаюи1его регистра/-#, схемы /5 совиадения, схемы 16 «НЕ, схемы/7совнаден1ия, регистр 18 каманд. Первый 1вход устройства 19 соединен со входом счетчнка / команд для подачи сигнала сумд1ирова-ния «I к записанному s счетчике коду. Первый выход Обустройства подключен к выходу регистра 18 команд, выход приемного регистра 21 является вторым выходом устройства, а входы 22 и 23 схем совпадения 15 и /7 являются вторым 1и третьим входами устройства, на которые поступают сигналы от блока выработки микрокоманд управления.

На каждо.м очередном цикле код предыдущей команды записан в регистре 18. Код номера серии команд с вы.хода счетчлка / команд лодается на вход регистра 2 адреса, а к содержимому счетчнка / ио сигиалу, поступающему на вход устройства /5, прибавляется «единипа. Выходы младших и старших разрядов кода адреса расшифровываются соответственно дешифраторами Л и 4 адреса, определяющими местоположение ячейки иамяти (з координатах х и у) в блоке 8 па.мятп, соответствуюп1ее этому коду. Выходные сигиалы дешифраторов 3 и 4 поступают на ВХОДЫ адресных форм.ирователей 6 и ключей 5, вьфабатываюи1.их ток считывания в выбраииой ячейке блока 8, хранящей код серии команд. Выходиые сигналы блока 8 усиливаютея усилителями 9 считывания и поступают на вход регистра 10. Далее -принятый код регенери.руется в ячейку -блока 8, из которой он подается на вход регистра 11. Предварительно в младший разряд регистра 14 по специальному входу (на чертеже не показан) записывается «единица. Пр.и установ,ке кода в .регистре /./ схема ./5 поразрядного сравнения произ1ВО|Дит сравнение кодов, записанных в {регистрах 11 и .14. При отсутствии «единицы в младшем разряде регистра 11 схема 13 1ВырабатьгВает на выходе сигнал нессинадения, который через схему «НЕ 16 .подается на вход схемы 15 co-Bin а дети я . сигнал разреше1пия микрокоманды поразрядного сдвига (азход 22). OpiJi этом «единица сдвигается в следуюидий разряд регистра 14. Сдеиги происходят до того .момента, по.ка на выходе схемы 13 не появится сигнал совладения, свидетельствующий о том, что сдвигаемая «единица реюистра 14 совиала с «еди-ницей в ближайшем к младшему разряде кода регистра/У. Номер этого разряда, онределяемый положением «единицы в коде регистра 14, является номером разряда кода адреса предыдущей команды, значение которого необходимо инвертировать для получения кода адреса последующей кОМанды. Для этого при }галич1ии сигн.ала, поступающего со входа 23 на вход схемы 17, поступает управляющий сигнал (вход 22), по которому в регистре 18 команд инвертируется значение разряда, поступившего с выхо.да релИСтра 14. На этом оканчивается цикл формирования первой команды. iPa6oTa устройства по форм фовапию следующих команд серии происходит аналогично до тех пор, пока «еднница в periicTpe 14 не -переместится в крайний старший разряд. Нри этом она циклически передается снова в младшнй разряд регистра 14, одновременно являясь сигналом обращения за следующим кодом формирования серии команд и т. д. Предмет изобретения Устройство управления цифровой вычислительной машины, содержащее счетчик команд, первый .вход которого соединен с выходом регистра команд и первым (выходом устройства, второй вход - с первым входом устройства, а выход связан со входом регистра адреса, подключенного через дещифраторы адресов X и Y, адресные ключи и формирователи к адресным входам блока намяти, выход которого через усилители считывания соедине со входом приемного регистра, первый вход которого подключен через узел формирования записи к информациолному входу бло.ка памяти, а второй и третий входы связа}1ы соответственно со вторым выходом устройства входом регистра серии команд, отличающееся тем, что, с целью увеличения быстродействия и сокращения оборудовапия, оио содержит блок формирования последующей команды, входы которого соединены соответственно с выходом регистра серии команд и вторым и третьнм входами устройства, а его выходы подключены соответственно к первому и второму входам регистра кома«д.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления цифровой вычислительной машины | 1975 |

|

SU598076A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267413A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Микропрограммное устройство управления | 1982 |

|

SU1019449A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство для сопряжения процессора с абонентами | 1987 |

|

SU1539787A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

Даты

1974-05-15—Публикация

1972-09-01—Подача