01

00 to

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах обработки информации.

Известно устройство, которое содержит дешифратор адреса, входы которого соединены с регистром адреса, накопитель, нервая группа входов записи которого соединена с первой группой выходов регистра регенерации, блок усилителей считывания, первая группа выходов которого соединена с первой группой входов регистра регенерации и адреса слова, соединенный с первыми входами блока управления, обладающая избытком оборудования 1.

Недостатком этого устройства является сложность.

Наиболее близким техническим решением к изобретению является запоминаюплее устройство, содержащее дешифратор адреса, входы которого соединены с регистром адреса, накопитель, первая группа входов записи которого соединена с первой группой регистра регенерации, блок усилителей считывания, первая группа выходов которого соединена с информационными входами блока ключей коммутации, выходы которого соединены с первой группой входов регистра регенерации и регистр адреса слова, вторая группа входов регистра регенерации соединена с выходом регистра адреса слова, вторая группа выходов блока усилителей считывания соединена со вторыми входами блока управления, выходы которого подключены к управляющим входам блока ключей коммутации, а вторая группа выходов регистра регенерации соединена со второй группой входов записи накопителя 2.

Недостатком известного устройства является избыток оборудования, обусловленный необходимостью хранить в накопителе указатель положения информации в ячейке памяти, и отсутствие возможности менять информацию отдельного элементарного слова без предварительной обработки информации вне запоминающего устройства.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство, содержащее накопитель, адресные входы которого соединены с выходом дешифратора адреса, входы которого подключены к выходам первого регистра адреса, усилители считывания, входы которых соединены с разрядными выходами накопителя, а выходы - с одними из входов коммутатора и информационными входами регистра регенерации, выходы которого подключены к входам записи накопителя, блок управления, входы которого соединены с выходами второго регистра адреса, а выходы - с управляющими входами коммутатора, выходы которого являются выходами устройства, введены дешифратор номера корректируемого слова, триггер записи единиц, триггер записи нулей, триггер режима коррекции и триггеры номера корректируемого слова,

выходы которых подключены к информационным входам дешифратора номера корректируемого слова, управляющий вход которого соединен с выходом триггера режима коррекции, причем выходы триггера записи

единиц, триггера записи нулей и дешифратора номера корректируемого слова подключены соответственно к управляющим входам регистра регенерации, входы коррекции которого соединены с выходами коммутатора, другие входы которого являются

информационными входами устройства, управляющими входами которого являются входы триггеров записи единиц, записи нулей, режима коррекции и номера корректируемого слова.

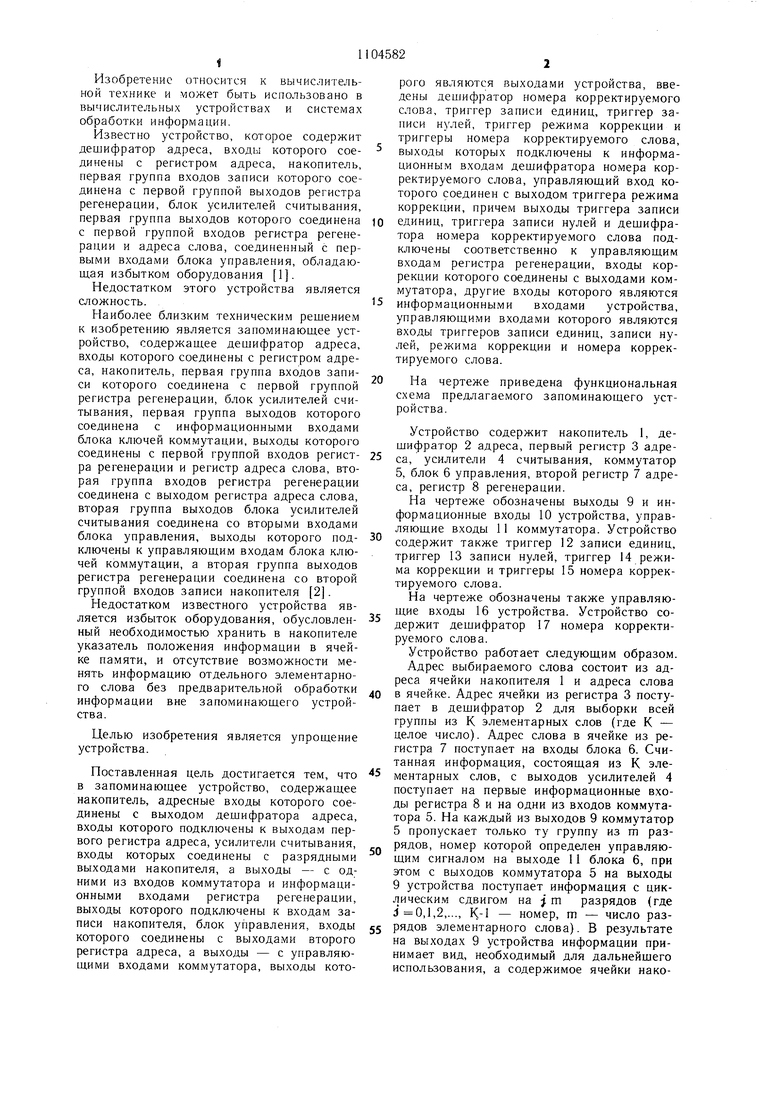

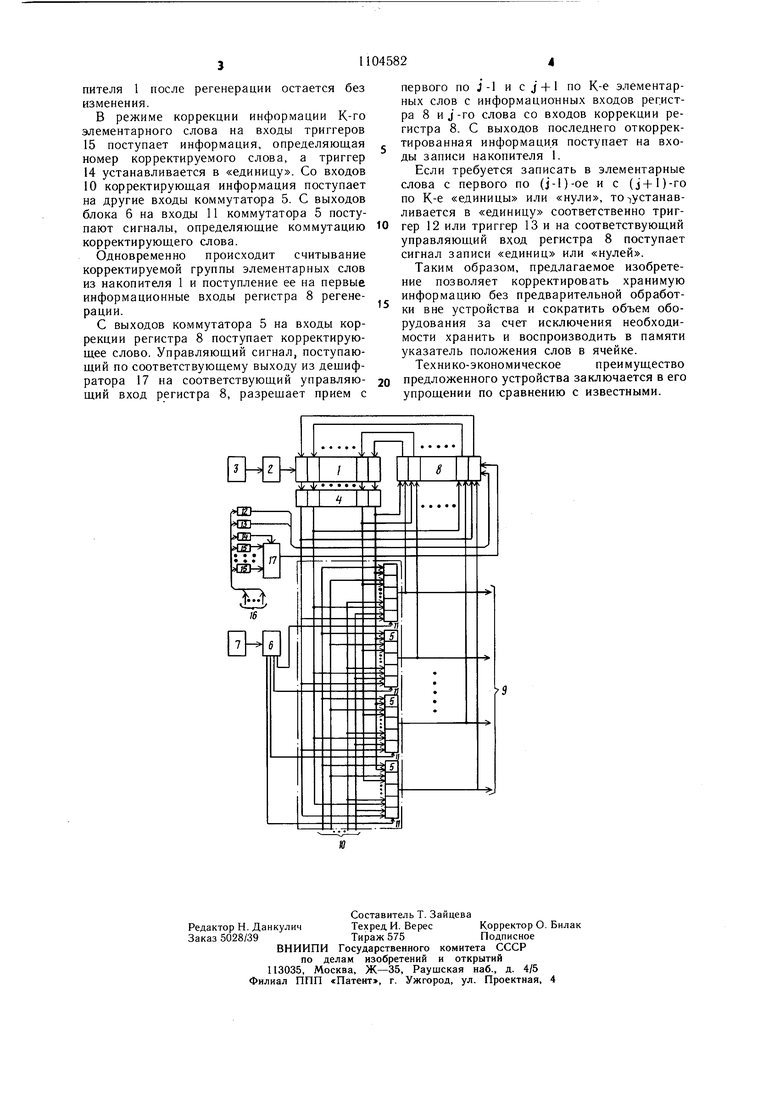

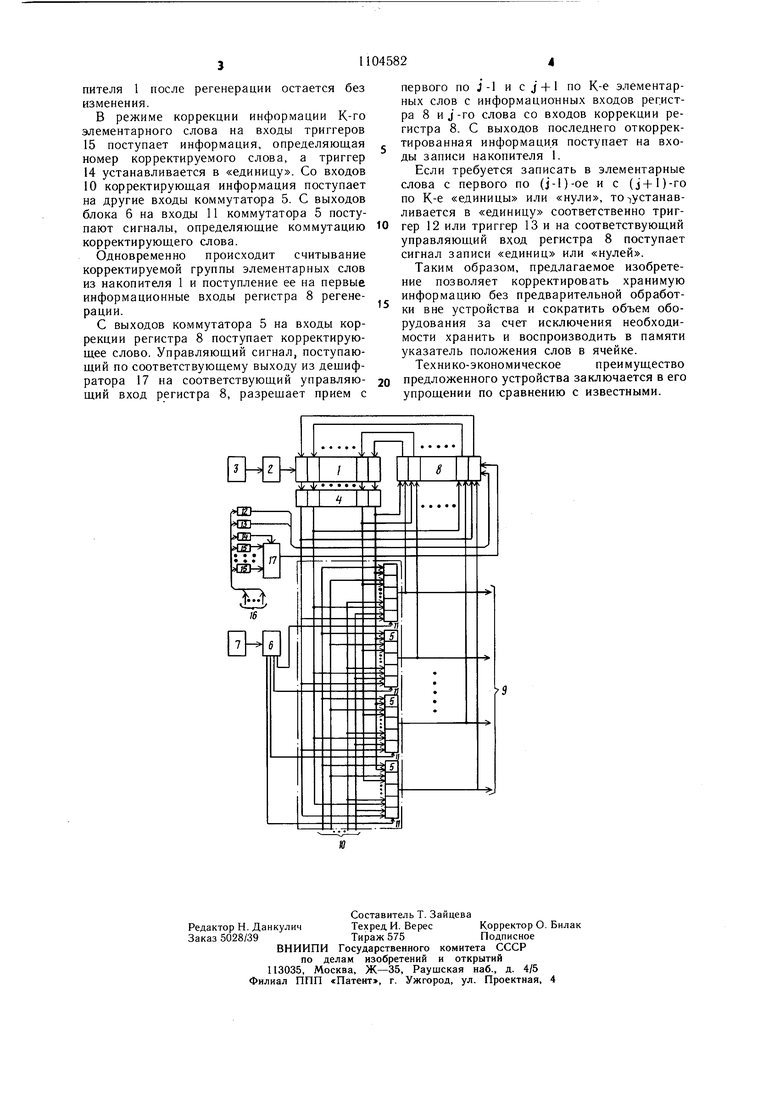

0 На чертеже приведена функциональная схема предлагаемого запоминающего устройства.

Устройство содержит накопитель 1, дешифратор 2 адреса, первый регистр 3 адре5 са, усилители 4 считывания, коммутатор 5, блок 6 управления, второй регистр 7 адреса, регистр 8 регенерации.

На чертеже обозначены выходы 9 и информационные входы 10 устройства, управляющие входы 11 коммутатора. Устройство

содержит также триггер 12 записи единиц, триггер 13 записи нулей, триггер 14 режима коррекции и триггеры 15 номера корректируемого слова.

На чертеже обозначены также управляющие входы 16 устройства. Устройство содержит дешифратор 17 номера корректируемого слова.

Устройство работает следующим образом. Адрес выбираемого слова состоит из адреса ячейки накопителя 1 и адреса слова

0 в ячейке. Адрес ячейки из регистра 3 поступает в дешифратор 2 для выборки всей группы из К элементарных слов (где К - целое число). Адрес слова в ячейке из регистра 7 поступает на входы блока 6. Считанная информация, состоящая из К эле5 ментарных слов, с выходов усилителей 4 поступает на первые информационные входы регистра 8 и на одни из входов коммутатора 5. На каждый из выходов 9 коммутатор 5 пропускает только ту группу из гп раз.. рядов, номер которой определен управляющим сигналом на выходе 11 блока 6, при этом с выходов ком.мутатора 5 на выходы 9 устройства поступает информация с циклическим сдвигом на j m разрядов (где i 0,1,2,..., К,-1 - номер, m - число раз5 рядов элементарного слова). В результате на выходах 9 устройства информации принимает вид, необходимый для дальнейшего использования, а содержимое ячейки нако

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Устройство для обмена информацией | 1979 |

|

SU849193A1 |

| Запоминающее устройство | 1978 |

|

SU769622A1 |

| Запоминающее устройство | 1975 |

|

SU583475A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопитель, адресные входы которого соединены с выходом дешифратора адреса, входы которого подключены к выходам первого регистра адреса, усилители считывания, входы которых соединены с разрядными выходами накопителя, а выходы - с одними из входов коммутатора и информационными входами регистра регенерации, выходы которого подключены к входам записи накопителя, блок управления, входы которого соединены с выходами второго регистра адреса, а выходы- с управляющими входами коммутатора, выходы которого являются выходами устройства, отличающееся тем, что, с целью упрощения устройства, в него введены дещифратор номера корректируемого слова, триггер записи единиц, триггер записи нулей, триггер режима коррекции и триггеры номера корректируемого слова, выходы которых подключены к информационным входам дешифратора номера корректируемого слова, управляющий вход которого соединен с выходом триггера режима коррекции, причем выходы триггера записи единиц, триггера записи нулей и дешифратора номера корректируемого слова подключены соответственно к управляющим входам регистра регенерации, входы коррекции ко§ торого соединены с выходами коммутатора, другие входы которого являются инфорся мационными входами устройства, управляющими входами которого являются входы триггеров записи единиц, записи нулей, режима коррекции и номера корректируемого слова.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ВОДКА "ЗИМУШКА" | 1997 |

|

RU2123040C1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство | 1975 |

|

SU583475A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-07-23—Публикация

1983-02-28—Подача