1

Изобретение может быть использовано в вычислительной технике и устройствах автоматики.

Известна матрица для заноминаюндего устройства, содержащая МДП-транзисторы с изменяемым порогом включения, которые по строкам затворами подключены к управляющи М шИНам, а по столбцам объединены между собой двумя или более шинами. Последнее обстоятельство приводит к усложнению конструкции матрицы и требует для ее управления источников положительных и отрицательных сигналов.

Цель изобретения - упрощение конструкции матрицы.

Это достигается тем, что в каждом столбце сток предыдущего транзистора соединен с истоком последующего, при этом исток первого транзистора каждого столбца подключен к щнне питания, а сток последнего - к щине считывания.

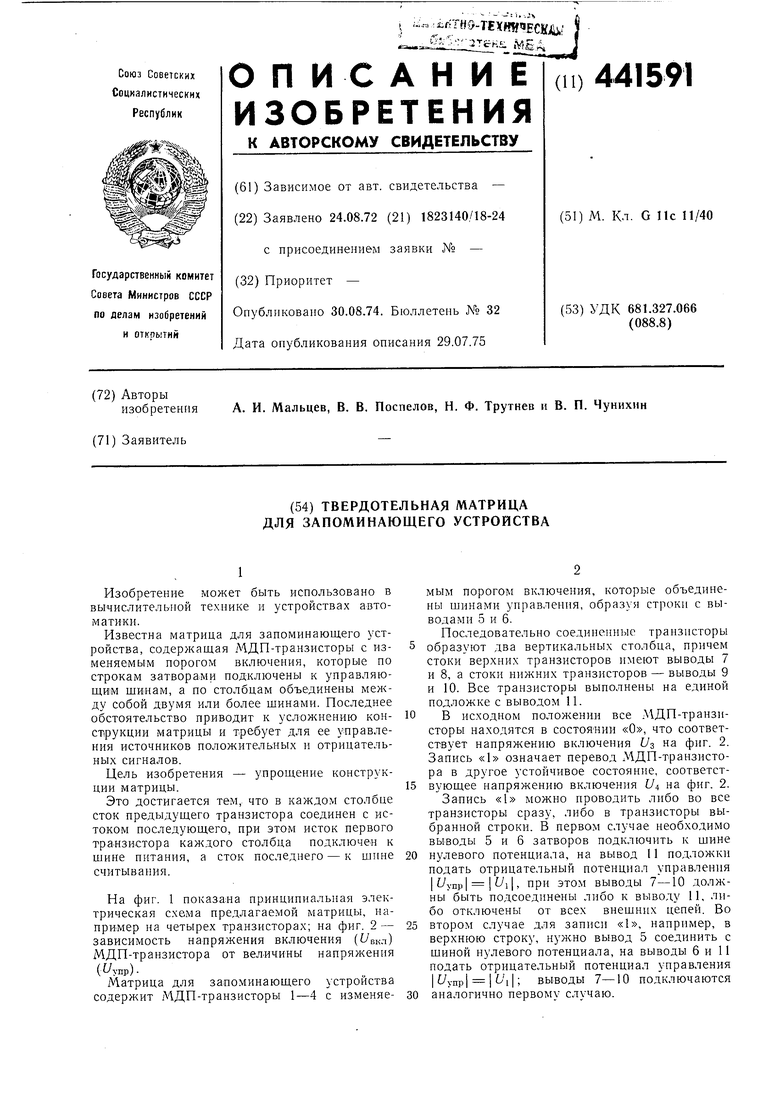

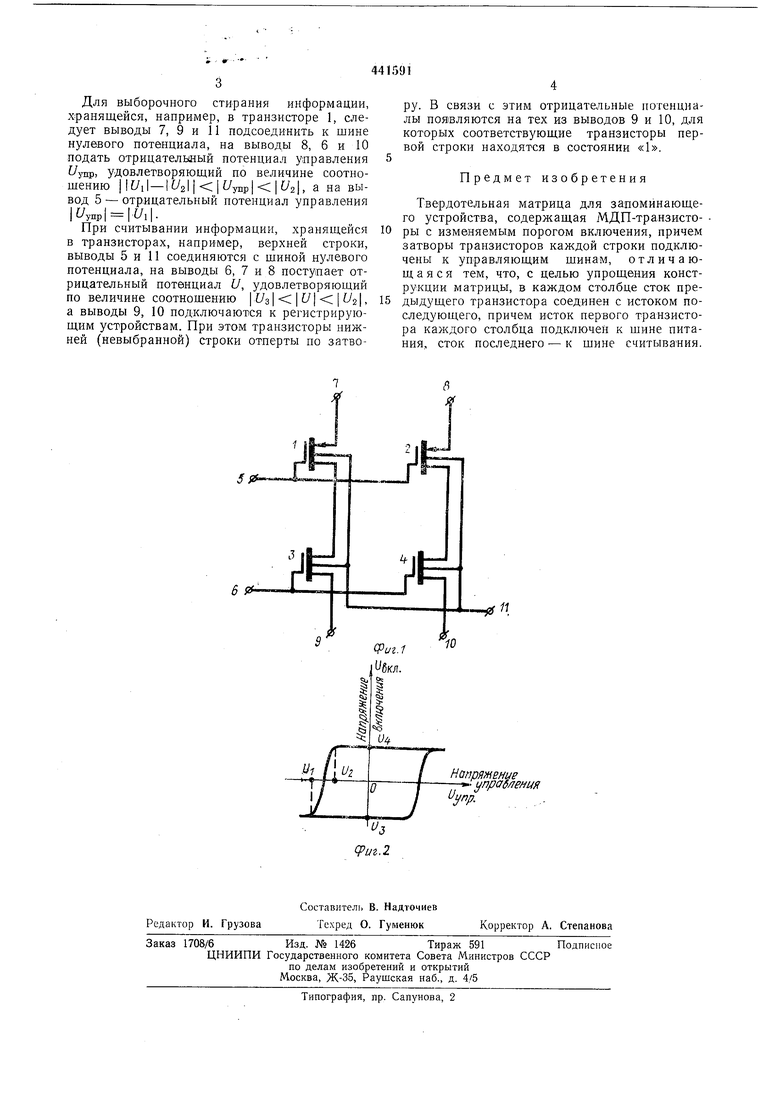

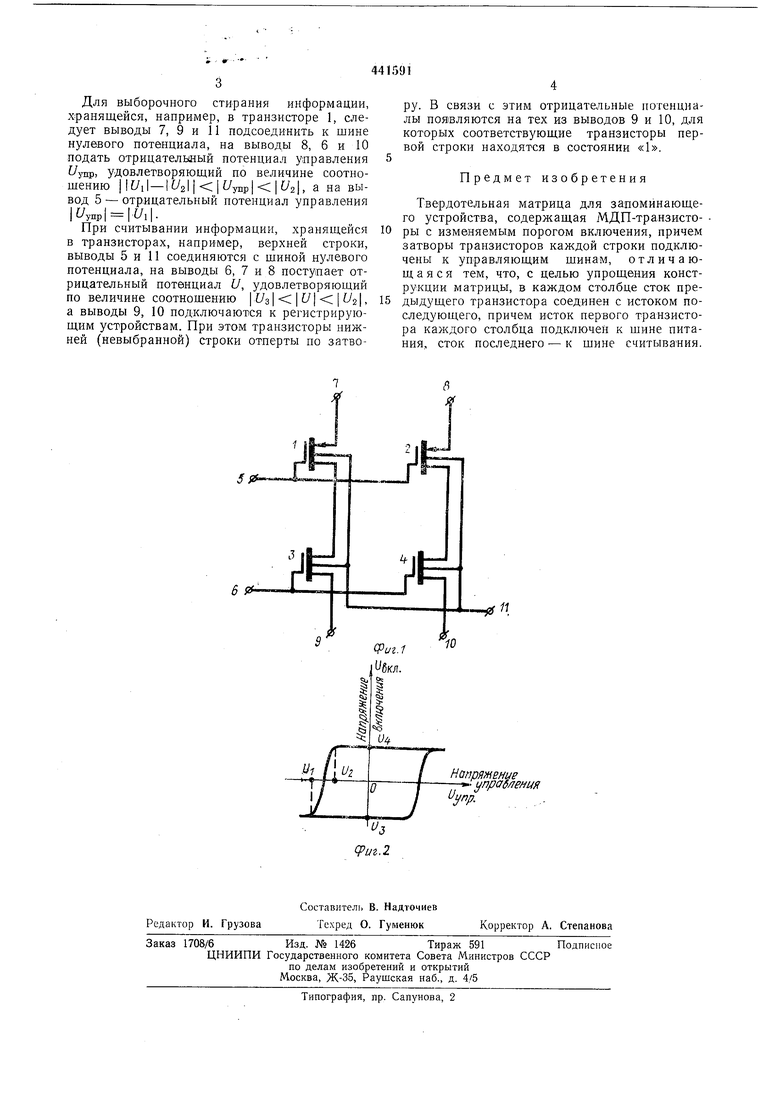

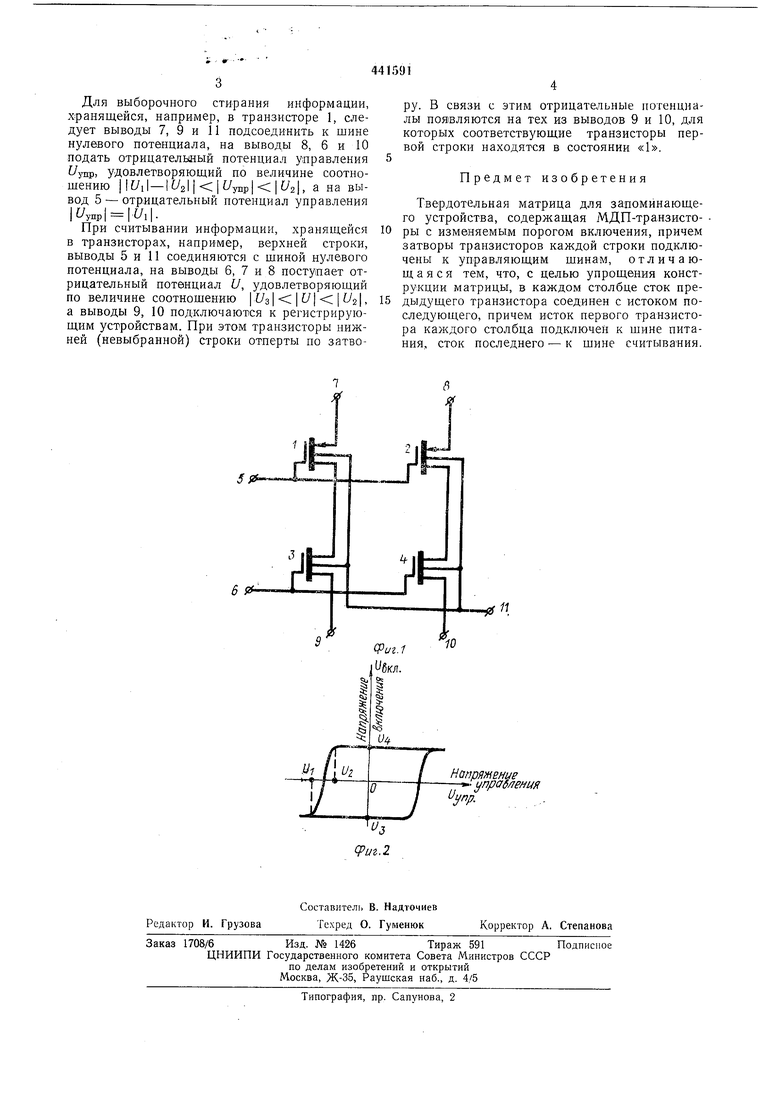

На фиг. 1 показала пр.инципиальная электрическая схема предлагаемой матрицы, например на четырех транзисторах; на фиг. 2 - зависимость напряжения включения (.-i) МДП-транзистора от вел-ичины напряжения

().

Матрица для запоминающего устройства содержит МДП-транзисторы 1-4 с изменяемым порогом включения, которые объединенЕз1 шинами управления, образуя строки с выводами 5 и 6. Последовательно соединенные транзисторы

образуют два вертикальных столбца, причем стоки верхних транзисторов имеют выводы 7 и 8, а стоки нижних транзисторов - выводы 9 и 10. Все транзисторы выполнены на единой подложке с выводом 11.

В исходном пололсении все МДП-транзисторы находятся в состоянии «О, что соответствует напряжению включения (Уз на фнг. 2. Запись «1 означает перевод МДП-транзистора в другое устойчивое состояние, соответствующее напряжению включения f/4 на фиг. 2. Запись «1 можно нроводить либо во все транзисторы сразу, либо в транзисторы выбранной строки. В первом случае необходимо выводы 5 и 6 затворов подключить к шине

нулевого потенциала, на вывод 11 подложки подать отрицательный потенциал управления I Уупр| I fVi I, при этом выводы 7-10 должны быть подсоединены либо к выводу 11, либо отключены от всех внешних цепей. Во

втором случае для записи «1, например, в верхнюю строку, нужно вывод 5 соединить с шиной нулевого потенциала, на выводы 6 и 11 подать отрицательный потенциал управления I Lynpl I 6i I; выводы 7-10 подключаются

аналогично первому случаю. Для выборочного стирания информации, хранящейся, нанример, в транзисторе 1, следует выводы 7, 9 и 11 подсоединить к шине нулевого потенциала, на выводы 8, 6 и 10 подать отрицательный потенциал управления Uynf, удовлетворяющий по величине соотношению I It/11 - 1V2l| |t yDp| |t/2|, а на вывод 5 - отрицательный потенциал уцравления l ynp|-|f/l|. При считывании информации, хранящейся в транзисторах, например, верхней строки, выводы 5 и 11 соединяются с шиной нулевого потенциала, на выводы 6, 7 и 8 поступает отрицательный потенциал U, удовлетворяющий по величине соотношению | f/з | | f/1 | Lg |, а выводы 9, 10 подключаются к регистрирующим устройствам. При этом транзисторы нижней (невыбранной) строки отперты по затвору. В связи с этим отрицательные потенциалы появляются на тех из выводов 9 и 10, для которых соответствующие транзисторы первой строки находятся в состоянии «1. Предмет изобретения Твердотельная матрица для запоминающего устройства, содержащая МДП-транзисторы с изменяемым порогом включения, причем затворы транзисторов каждой строки подключены к управляющим шинам, отличающаяся тем, что, с целью упрощения конструкции матрицы, в каждом столбце сток предыдущего транзистора соединен с истоком последующего, причем исток первого транзистора каждого столбца подключей к шине питания, сток последнего - к шине считывания.

в

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство для считывания информации из матричного накопителя | 1978 |

|

SU767834A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Программируемое постоянное за-пОМиНАющЕЕ уСТРОйСТВО | 1978 |

|

SU809378A1 |

| Интегральное запоминающее устройство | 1974 |

|

SU523455A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Спектральный преобразователь электрических сигналов | 1976 |

|

SU690402A1 |

| Устройство для считывания информации из матричного накопителя | 1979 |

|

SU938315A2 |

| Интегральное запоминающее устройство на мдп транзисторах | 1973 |

|

SU458036A1 |

Напря НЕнш - упраб/i

ления

Авторы

Даты

1974-08-30—Публикация

1972-08-24—Подача