Изобретение относится к вычислительной технике -и может быть использовано при построении интегральных постоянных запоминающих устройств. Известно устройство для считывания информации из матричного накопителя, содержащее транзисторы выборки и дешифраторы 1. При считывании информации ток, протекающий через запоминающий элемент, перезаряжает парайитные емкости, подключенные как к стоку/ так и к истоку открытого транзистора выборки, 4fo ограничивает быстродействие данного запоминакяцего устро ства. Известно устройство для считывания информации, содержащее два дешиф ратора, транзисторы выборки, а также запоминающие-элементы, органйзованные в виде.матрицы {2. При считывании информации, хранимой в некоторбм запоминающемэлементе, ток, протекающий через этот элемент/перезаряжает паразитные емкости подключенные как к стоку,так и к ист ку открытого транзистора выборки,что ограничивает быстродействие запомин ющего устройства. . Из известных устройств наиболее близким по технической сущности является устройство для с 1итывания . ; информации из матричного накопите- ля, используемое в интегральном запоминающем устройстве 3. Указанное запоминающее устройство содер) информационные транзисторы, организованные в матрицу, а также транзисторы, соединяющие информационные транзисторы с выходом разрядной шины и выполняющие функции ключей, На затворы .информационных транзисторов сигнсшы подаются с выходов первого дешифратора. Затворы ключей транзисторов подключены к выходам второго дешифратора. При считывании информации, хранимой в некотором запоминающем элементе, ёсли этому элементу соответствует информационный транзистор (записана Ч),ток, протекающий через этот транзистор, заряжает паразитные емкости, подключенные как кстоку: так и к истоку ключевого транзисто1ра, что уменьшает быстродействие этого запоминающего устройства. Цельй изобретения является увеличение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для считывания информации из матричного нако-пителя, содержащее ключевые транзисторы, стоки которых подключены.к шине считывания, истоки - к соотРветствующим разрядным шинам накопителя, а затворы - к соответствующим управляющим шинам, шины выборки и нулевого потёндиала, введены элемент задержки и шунтирующий транзистор, сток которог6 подктпочен к шине считывания, исток - к шине нулевого потенциала, а зйтвор через элемент задержки к шине выборки.

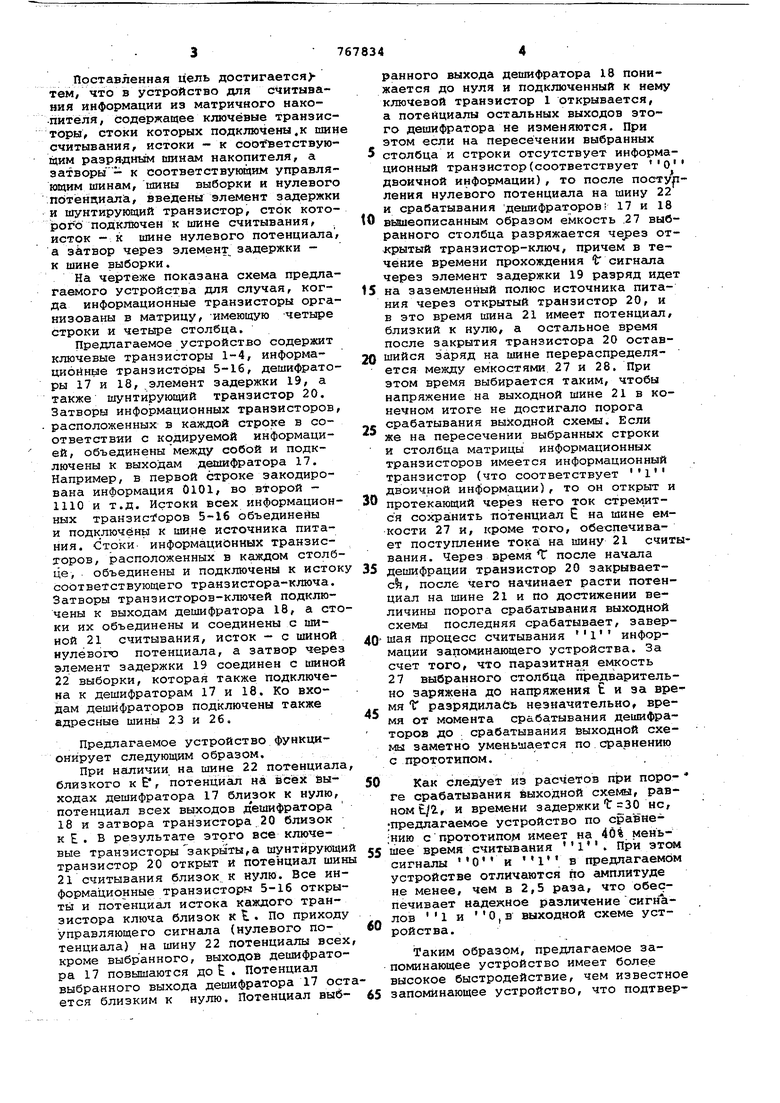

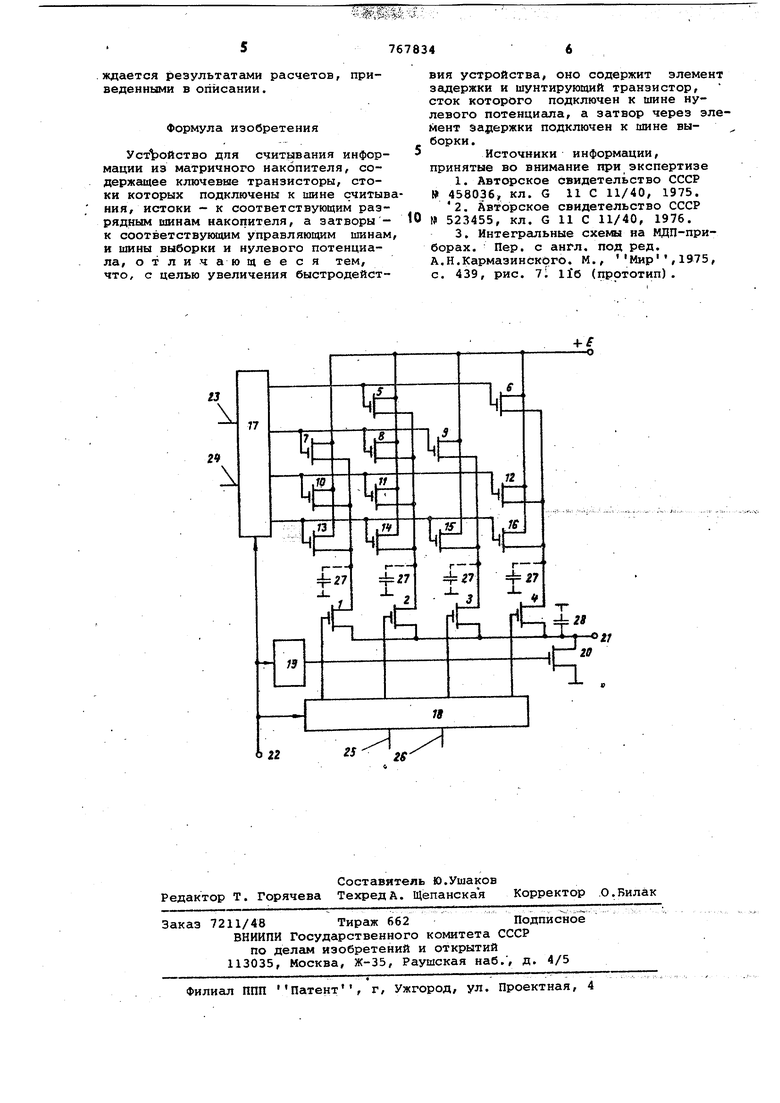

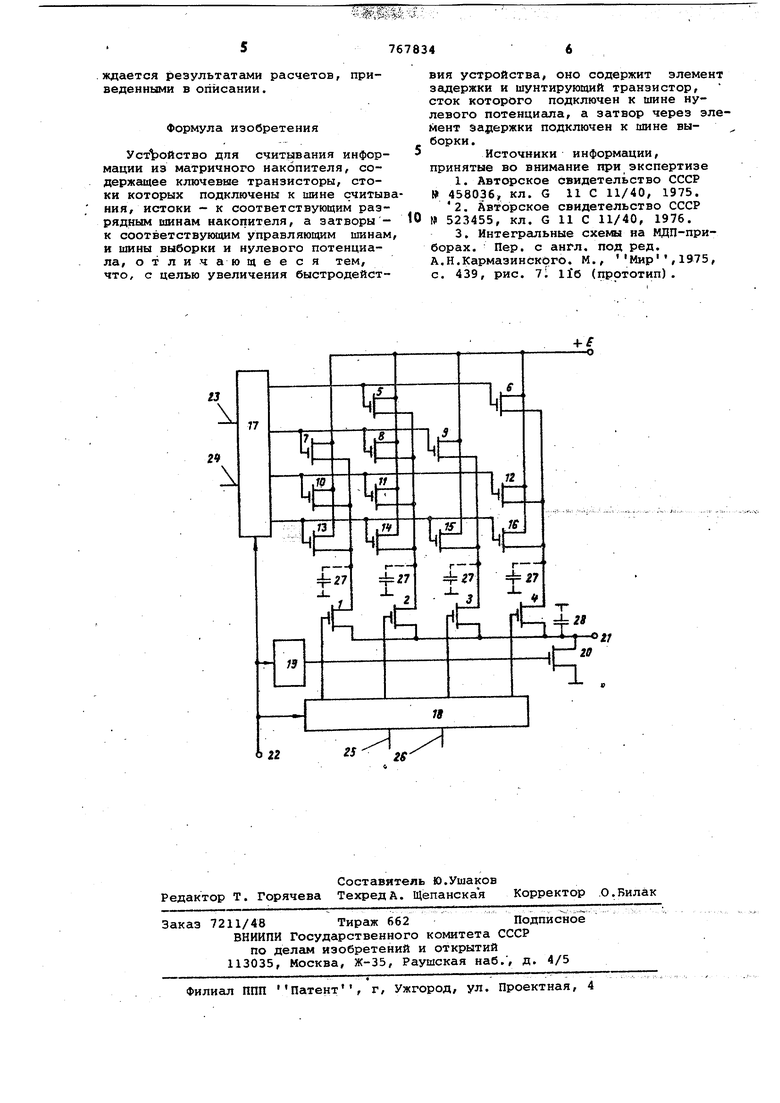

На чертеже показана схема предлагаемого устройства для случая, когда информационные транзисторы организованы в матрицу, Имеющую -четыре строки и четыре столбца.

Предлагаемое устройство содержит ключевые транзисторы 1-4, информационные транзисторы 5-16, дешифраторы 17 и 18, элемент задержки 19, а также шунтирующий транзистор 20. Затворы информационных транзисторов, расположенных в каждой строке в соответствии с кодируемой информацией, объединены между собой и подключены к выходам дешифратора 17. Например, в первой строке закодирована информация 0101, во второй 1110 и т.д. Истоки всех информационных транзисторов 5-16 объединейы и подключены к шине источника питания. Стоки- информационных транзисторов, расположенных в каждом столбце, объединены и подключены к истоку соответствующего транзистора-ключа. Затворы транзисторов-ключей подключены к выходам дешифратора 18, а стоки их объединены и соединены с шиной 21 считывания, исток - с шиной нулевого потенциала, а затвор через элемент задержки 19 соединен с шиной 22 выборки, которая также подключена к дешифраторам 17 и 18. Ко входам дешифраторов подключены также адресные шины 23 и 26.

Предлагаемое устройство функционирует следующим образом.

При нашичии. на шине 22 потенциала, близкого к Ё, потенцисш на всех выходах дешифратора 17 близок к нулю, потенциал всех выходов дешифратора 18 и затвора транзистора 20 близок к Е. В результате этого все ключевые транзисторызакрыты,а шунтйрунзщий транзистор 20 открыт и потенциал шины 21 считывания близок к нулю. Все информационные транзистора 5-16 открыты и потенциал истока каждого транзистора ключа близок к t. По приходу управляющего сигнала (нулевого потенциала) на шину 22 потенциалы всех, кроме выбранного, выходов дешифратоа 17 повышаются доЕ . Потенциал выбранного выхода дешифратора 17 остается близким к нулю. Потенциал выбранного выхода дешифратора 18 понижается до нуля и подключенный к нему ключевой транзистор 1 открывается, а потенциалы остальных выходов это го дешифратора не изменяются. При этом если на пересечении выбранных столбца и строки отсутствует информационный транзистор(соответствует О двоичной информации) , то после поступления нулевого потенциеша на шину 22 и срабатывания дешифраторов 17 и 18 виаеописанным образом емкость .27 выбранного столбца разряжается через открытый транзистор-ключ, причем в течение времени прохождения 1Г сигнгша через элемент задержки 19 разряд идет на заземленный полюс источника питания через открытый транзистор 20, и в это время шина 21 имеет потенциал, близкий к нулю, а остальное время после закрытия транзистора 20 оставшийся заряд на шине перераспределяется между емкостями 27 и 28. При этом время выбирается таким, чтобы напряжение на выходной шине 21 в конечном итоге не достигало порога срабатывания выходной схемы. Если же на пересечении выбранных строки и столбца матрицы информационных транзисторов имеется информационный транзистор (что соответствует i двоичной информации), то он открыт и протекающий через него ток стремится сохра;нить потенциал Е на шине емкости 27 и, кроме того, обеспечивает поступление тока на шину 21 считывания. Через время Т после начала дешифрации транзистор 20 закрываетcfe, после чего начинает расти потенциал на шине 21 и по достижении величины порога срабатывания выходной схемы последняя срабатывает, заверинфор40 шая процесс считывания

мации запоминающего устройства. За счет того, что паразитная емкость 27 выбранного столбца предварительно заряжена до напряжения Е и за время f разрядилась незначительно, время от момента срабатывания дешифраторов до срабатывания выходной схемы заметно уменьшается по сравнению с прототипом.

50 Как следует из расчетов при пороГе срабатывания выходной схемы, равном 2., и времени задержки t 30 не, ;предлагаемое устройство по сравне;нию с прототипом имеет на 46% меньшее время считывания . При этом

в предлагаемом

сигналы

устройстве отличаются по амплитуде не менее, чем в 2,5 раза, что обеспечивает надежное различение сигИаff. лов 1 и о, в выходной схеме устройства.

Таким образом, предлагаемое запоминающее устройство имеет более высокое быстродействие, чем известное 65 запоминающее устройство, что подтверждается результатами расчетов, приведенными в описании.

Формула изобретения

Устройство дпя считьавания информации из матричного накопителя, содержащее ключевые транзисторы, стоки которых подключены к шине считыва ния, истоки - к соответствующим разрядным шинам накопителя, а затворы к соответствукицим управляющим шинам, и шины выборки и нулевого потенциала, отличающееся тем, что, с целью увеличения быстродействия устройства, оно содержит элемент задержки и шунтирующий транзистор, сток которого подключен к шине нулевого потенциала, а затвор через элемент эацержки подключен к шине выборки. Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 458036, кл. G 11 С 11/40, 1975. 2. Авторское свидетельство СССР 523455, кл. G 11 С 11/40, 1976.

3. Интегральные схеюл на МДП-приборах. Пер. с англ, под ред. А.Н.Кармазинскйго. М., Мир,1975, с. 439, рис. 71 Иб (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из матричного накопителя | 1979 |

|

SU938315A2 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| НАКОПИТЕЛЬ ЭЛЕКТРИЧЕСКИ ПРОГРАММИРУЕМОГО ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1991 |

|

RU2028676C1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

гз

.

29

622

а

2S

Авторы

Даты

1980-09-30—Публикация

1978-01-24—Подача