(54) УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИНФОРМАЦИИ ИЗ МATВ1 МНОГО НАКОПИТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания информации из матричного накопителя | 1978 |

|

SU767834A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Устройство записи и считывания информации для динамического накопителя на однотранзисторных запоминающих элементах | 1976 |

|

SU727023A1 |

| Усилитель считывания на кмдп-транзисторах | 1978 |

|

SU771716A1 |

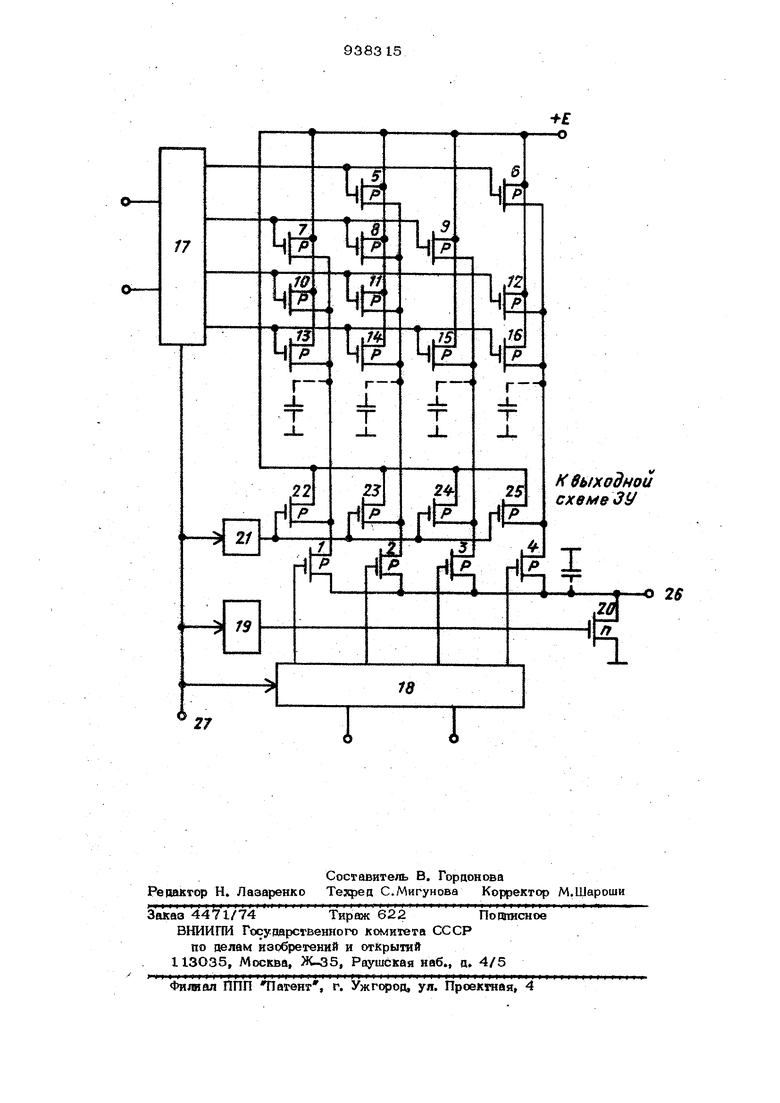

Изобретение относится к вычислитель ной тетшике и можег быть нспо/шаовано при построении интегральных постоянных запоминающих устройств.. Известно устройство аля считывания информации, соаеркашее цва оешифратора, транздсторы выборки, а также запоминаюише элементы, организованные в вице матрицы tl. OwaKo это устройство отличается не высоким быстроаействием. Известно устройство для считывания информации из матричного накопителя, со цержашее информадис тые транзисторы, (ганизованные в матрицу, а также гран зисторы, соеоиняюшие информационные транзисторы с выхоаом разряоной шины выполняющие (функции ключей 23, Недостатком устройства является невысокое быстродействие. По основному авт. св. № 767834 известно устройство сооержащеа информационные транзисторы, (|ешифрато- ры строк и столбцов, ключевые транзисторы, элемент эаоерокки н шунткрук ший транзистор, гцрп этом затворы янфо ьмацишных травзистороь, располоисенвых ь каждой строке, обьефневы межпу собой и пооключевы к выходам неокфротора строк, истоки всех {шформапионвых трав- aicTopcm обьешвены и пооключевы к пи-, не источника ( стокн ивформацяо ных трввзисторов, распояокенвых в каждом столбце, обьешгаены н пооключевы к истоку соответствукяцего ключевого траяоистсфа, затворы юпочевых травансторсв соедавевы с выходам пешифратора стоя&дсю, а стокв обьедяневы в поцклю ювы к шине считывания, сток шувтвр)пашего транзистора также подключав к шнве сч тываввя, истек - к швве вулееого погево ця&гл, а затвор - через алемевт аадердк ки к швве выборки Сз. Потевоиад всех строк с пошслючеввы к ввм затвораьо квформапяоввых травяоторов взмбнявтся от О до Е (Е - вапря- , жевве всточвика пятавяя) в обратно с Toty же частотой,, с шисой {фоисхоавг обраще. 393 ние к ЗУ, что привооит к опрецеленным потерям мсщносги, затрачиваемой на перезаряц емкостей строк в каждом цикле обращения. Кроме того, по окончании считьшання информации перец тем, как осуществить новое обращение к ЗУ, ненеобходамо повысить потенциал стоков всех информационных транзисторов, что осуществляется через открываемые оля этого информационные транзисторы. Максимальное время, необходимое для попзаряда стоков информациежных транзисторов, имеет место в сдучае, когда в столб це находится лишь один транзистор. Размеры информационных транзисторов ограничены по известным причинам. Поэтому для заряда стоков этих транзисторов по окончании считывания информации требует ся значительное время, что удлиняет цикл работы ЗУ, уменьшая тем самым ег быстродействие. Цель изобретения - уменьшение потреб.яяемой мощности и увеличение быстродействия. Поставленная цель достигается тем, что в устройство для считывания информадии из матричного накопителя введены инвертор и элементы подзаряда на дополнительных транзисторах, истоки которых подключены к шине питания, затворы -к выходу инвертора, вход которого подключен к шине выборки, а сток каждого дополнительного транзистора - к истоку со ответствующего ключевого транзистора. На чертеже приведена схема предлага емого устройства. Устройство содержит ключевые транзисторы 1-4, информационные транзисторы 5-16, дешифраторы 17 и 18, элемен 19 заЕ(ержки, шунтирующий транзистор 20, а также инвертор 21 и элементы по заряда на дополнительных транзисторах 22-25. Инфсрмационные транзисторы организованы в матращу 4x4. Например, в пер вой строке закодирована информация ОЮ1, во второй - то и т.д. Предлагаемое устройство работает следующим образом. П{ж наличии на шине 27 потенциала, 6jBi3Koro к -Е потенциалы всех выходов дашифраторов 17 и 18 и затвора щунтир(ующего транзистора 2О близки к -Е, потенциал затворов дополнительных тран зисторов 22-25 близок к О.В результат этого все информационные и ключевые трш{ зв{сторы закрыты. Шунтирующий тра зистор 2О открыт, и потенциал шины 26 считывания близок к О. Все заряжающие 5 транаисторы открыты, поддерживая тем самым потеншюлы истоков ключевых транзисторов близкими к -Е. При обращении к запоминающему устройству нулевой потенциал подается на шину 27. По приходу нулевого потенциала на шину выборки потешшалы выбранных выходов дешифраторов 17 и 18 понижаются до О, а потенциалы остальных выходов дешифраторов не изменяются. В результате этого ключевой транзистоо. подключенный к выбранному выходу дешифратора 18, открывается. Вместе с тем потенциал затворов аопол}1ительных транзисторов повышается до -i-E, закрывая их. При этом, если на пересечении выбранньос стооки и столбца отсутствует информационный транзистор (что Соответствует нулю двоичной информации), то емкость выбранного столбца разряжается через открытый ключевой транзистор, причем в течение времени один разряд идет на шину нулевого потенциала через открытый транзистор 2О, и в это время шина 26 имеет потенциал, близкий к О, а в остальное время после закрывания транзистора 2О оставшийся на шине заряд перераспределяется меж емкост5рми. Время выбирается таким, чтобы напряжение на шине 26 в Конечном счете не достигало порога срабатывания выходной схемы. Если же на пересечении выбранных строки и столбца матрицы имеется информационный транзистор (что соответствует единице двоичной информации), то. он открыт и протекающий через него ток стремится сохранить потенциал Е на емкости. Кроме того, транздстор обеспечивает поступление тока на шину 26 считывания. Через время Т после начала обращения к ЗУ транзистор 2О закрывается, после начинает повышаться потенциал на шине 26 и по достижении величины порога срабатывания выходной схемы последняя срабатывает, завершая процесс считывания информации из запоминающего устройства. После этого на шину 27 подается потенциал , что приводит к открыванию заряжающих транзисторов2225 и шунтирующего транзистооа 2О, а также к повышению потенциалов двух выходов дешифраторов, бывших выбранными в рассмотренном цикле считывания. Через открытые заряжающие и шунтирующий транзисторы соответственно потешшал um- ны понижается до О, а потенциал стоков заряжакшшх транзисторов повышаются до +Е. Анализ работы устройства показывает, что выборки информации ( от мо593

мента срабатьшания аеишфрагоров цо cpt багывания выхооной схемы) осталось тенким же, как и в известном устройстве. Время от окончат1я считывания информации цо момента, когца можно вновь обратиться к цанному ЗУ, определяется главным образом временем, в течение которого потенциал стоков всех информационных транзисторе станет близким к fE и значительно уменьшено по сравне1ШЮ с известным устройством за счет того, что в предлагаемом ЗУ заряа емкостей столбце после считывания осуществляется посредством дополнительных транзисторов 22-25, которых много мень ще, чем информационных и которые поэтому могут иметь большую крутизну, чем информахшонные транзисторы. Это позволяет значительно сократить время востановления ЗУ, а значит и цикл его работы. Кроме того, при одном этом обращении к предлагаемому устройству потенциал лишь одной строки матрицы и одной строки дополнительных транзисторов изменяется в пределах от +Е д о О и o6paTно, в то время как в известном устройстве в каждом цикле в указанных пределах изменяются потеюшалы всех строк матрицы, кроме одной, срабатывают все, кроме одного, каскады дешифратора строк.

Таким образом, при расчете мощности Б известном устройстве необходимо учитывать потери мощности, вызванные протеканием сквозных токов во всех, кроме выбранного, выходных каскадных дешиф

156

раторах строк, так как каскады ати пе реключаются дважды при каждом обращении к ЗУ. В сфедлагаемом же устройстве при каждом обращении срабатывает .лишь опии выходной каскад оешифрагора строк.

Таким , мощность рассеивания в предлагаемом устройстве существенно меньше, чем в известном.

Формула изобретения

Устройство ОЛЯ считывания информации из матричного накопителя по авг. св. N 767834, отлич ающеес я тем, что, с целью повышения бысг1 рае ствия и уменьшения потребляемой мощности, в него введены инвертор и элементы подзаряда на пополнительных rpai зисторах, истоки которых подключены к шине питания, затворы к &ыкоау инвертора, вход подключен к шине выборки, а сток каждого дополнительного транзистора -. к истоку соответствующего ключевого транзистора.

Источники информации, принятые во внимание щяя экспертизе

27

Авторы

Даты

1982-06-23—Публикация

1979-04-27—Подача