Изобретение относится к области запоминающих устройств.

Известно эапоьганающее устройство с автоновшым контролем, содержащее накопитель, подсоединенный к регистрам кодового слова, регистр о сшш корректирущего кода, блок кодирования, блок декодирования, подключенный к блоку управления, схему сравнения, блок схем И и блоки схем ШШ.

Недостатком известного устройства является то, что повышение его устойчивости к отказам в ячейках накопителя ведет к уменьшению эффективной емкости устройства (в результате увеличения информационной избыточности). Наоборот, увеличение эффективной емкости устройства вызывает снижение его устойчивости к отказам в ячейках накопителя (в результате уменьшения информационной избыточности).

Ош&снваецое устройство отличает ся от известного тем, что содержит

дополнительную схему сравнения, один вход которой подсоединен к регистру силы корректирущего кода, схему определения кратности отказов выход которой подсоединен к другим входам схем сравнения, а вход - к информационному входу блока схем И и к выходу введенной в устройство схемы определенвя отказавших разрядов, входы которой подключены к выходам регистров кодового слова, Выход блока генерации корректирующих слов подсоединен к одному из входов введенного в устройство распределительного блока, другой вход которого подключен к выходу блока схем И, а выход - к одному входу блока схем ИЖ, другой вход которого подсоединен к одному из регистров кодового слова, подключенному к выходу блока схем И, а выход - к блоку декодирования.

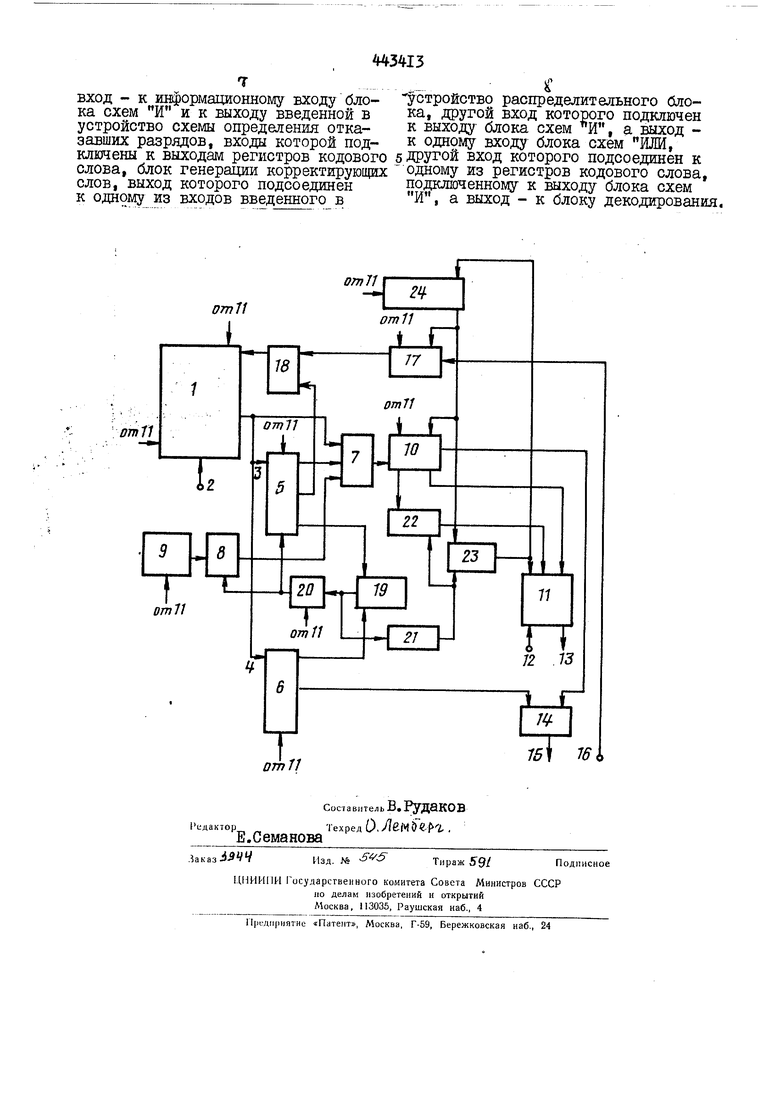

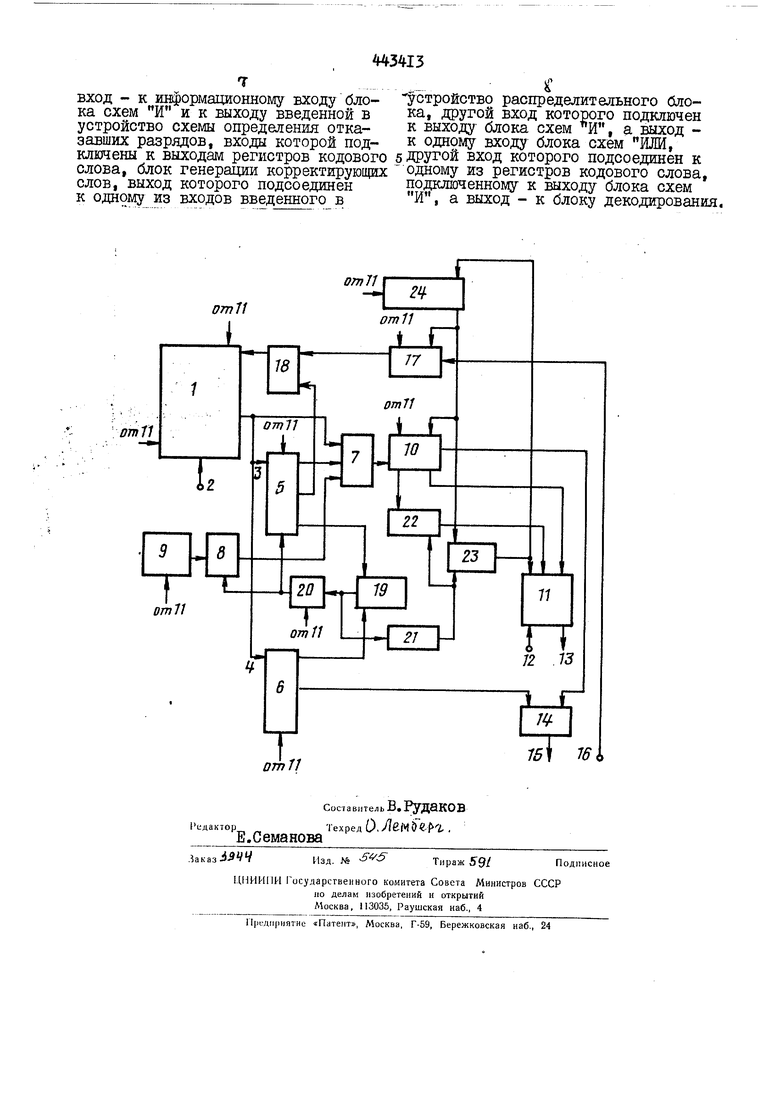

Указанные отличия позволяют увеличить эффективную емкость уст ройства и повысить надежность его работы. 3 На чертеже изображена блок схема предложенного запошшшощего устройства, Устройство содержит накопи- . тель I, имеющий информационный вход 2, Выход накопителя соединен с ко довыми входами 3 и 4 регистров 5 и 6 кодового слова и с одним входом блока 7 схем ИЖ. Кодовый вход . регистра 5 связан с другим входом блока 7 с третьим входом которого чеюез тэаспределительный блок 8 соеSSeH выход блока 9 генерации корректирующих слов, а выход блока 7 связан С кодовым входом блока 10 декодирования. Один управляющий выход блока 10 соединен с блоком II управления, имеющим вход 12 и выход 13, Информационный выход блока IU связан с одним входом блока 14 схем ИЛИ, с другим входом которого соединен инверсный информационный выход регистра 6, а выход блока м связан с информационным выходом io устройства, Шформационныи вход 1ь устройства соединен с информационным входом блока 17 кодирования, Кодовый выход блока 17 связан с одним входом блока 18 схем ИЛИ , с другим входом которого соединен инверсный кодовый выход регистра &, а выход блока 18 связан с кодовым входом накопителя I, Кодовые выходы регистров 5 и 6 соединены со входами схемы 19 определения отказавших разрядов. Выход этой схеш через блок 20 схем И связан с управляющими входагли регистра b и блока 8 и непосредственно соединен со входом схемы 21 определения крат ности отказов. Выход схеглы 21 связан с одним входом cxeivH 22 сравнения, с другим входом которой соединен другой управляющий выход блока 10, а выход схемы 22 связан с блоком II, Выход схемы 21 соединен так же с одншл входом дополнительной схеглы 23 сравнения, с друпш входом которой, а также с управляющшуШ вхо дами блоков 10 и 17, связан выход регистра 24 силы корректирующего кода, а выход схемы 23 соединен с блоком II и входом регистра 4,Накопит ель I, регистры 5,6 и 24 и бло ки 9,10,17 и 20 связаны с блоком 11 Запоглинающее устройство работает следующим образом. 4 4задз Регистр 24, управляющий блоками 10 и 17, настраивается на код, сила которого определяется максимальной кратностью имеющих место в 5 ячейках накопителя I отказов (под силой л корректирующего кода подразумевается его способность обнаруживать ошибки кратностью от I до ц включительно). Так, например, ю если максимальная кратность имеющих место в ячейках накопителя I отказов равна R , то сила корректирующего кода равна ( k+s ), где S кратность возникамцего отказа (имею щие место в ячейках накопителя I отказы являются результатом накопления в этих ячейках возникащих в разные моменты времени отказов кратности), При обнаружении в какой ни(удь ячейке накопителя I отказа краткости (k-«-S ), что возможно, когда в ячейке, содержащей k кратg g отказ, происходит отказ кратное S , регистр 24 и блоки 10 и 17 25перестраиваются на код с силой (R + 2s ),затем при обнаружении кратности (R ч- 2S )- на код с силой (И-нЗ )и т.д. Перестройка регистра 24 и блоков 10 и 17 происзоходит всякий раз, когда в кшсойиибудь ячейке накопителя I обнаруживается отказ, кратность которого равна силе используемого кода, для обращения к ячейке накопизбтеля I адрес её необходимо подать на вход 2„ При записи информационное слово до входу 16 поступает в блок 17, с выхода которого кодовое слово через облрк 18 записывается в накопитель I. При считывании кодовое слово из накопителя поступает в регистр 5, а с его выхода через блок 7 - в блок jg О целью повышения быстродействия tspTO же слово поступает из накопите- ля I в блоки 10 и 7, шшуя регистр 5, Блок 10 определяет наличие ошиб и в считанном .слове, - , Если сигнал .ошибки из блока 10 зоотсутствует, информационное слово с :его выхода через блок 14 выдается на выход 15, Если сигнал ошибки имеет место, - выдачи инсЬормационного слова на вы, ход 15 не происходит. Обратный код содержимого регистра 5 поступает через блок 18 в ту же ячейку накопителя I, а затем считывается из накопителя I в регистр 6, Схема 19 определяет отказавшие разряды ячейки по совпадению содержи мого одноименных разрядов регистров 5 и 6. Схема 21 определяет кратность имеющего место отказа, котораясравнивается схемой 22 с кратностью ошибки, определяемой блоком 10, а схемой 23-с содер 1симым регистра 24, определяюпщм силу используемого кода. В случае равенства кратности ошибки и кратности тлеющего место отказа обратный код информационной части кодового слова, записанного регистре 6, выдается через блок 14 на выход 15 (при использовании систематических кодов выделение информационной части кодового слова не представляет затруднений). При этом на выходе 15 получается правильное информационное слово. Если в ячейку накопителя I записывается кодовое слово OIOOIOI0 (шоготочием обозначены контрольные разряды),то в результате тлеющего место в ней, напршлер, тройного отказа получается кодовое слово ИШОЮ (в подчеркнутых разрядах произошло искажение информации, вызвавшее возншшовение трой ной ошибки). После записи в ту же ячейку накопителя I обратного кода считанного слова и его считывания информационная часть кодового слова представляет собой 10П0101, что после инвертирования в регистре 6 даёт праы-тльное информационное слово OIOOIOIO. В случае, если кратность ошибки не равна (меньше) кратности тлею щего место отказа, обратный код информационной части кодового слова на выход 15 не поступает. Схема 19 через блок 20 запрещает выдачу с регистра 5 через блок 7 в блок 10 содер 1шмого отказавших разрядов. Вместо этих разрядов к блоку 7 подключаются через блок 8 разряды блока 9 (в качестве блока 9 может быть использован, например, счетчик). Блок 9 начинает последовательно вырабатывать возможные комбинации нулей и единиц (корректирующие елова), число разрядов в которых равно числу отказавших разрядов в ячейке накопителя I Работа блока 9 прекращается, как только из блока 10 в блок II поступает сигнал отсутствия ошибки. После исправления искаженного кодового слова информационное слово из блока 10 поступает через блок 14 на выход 15. Указанную коррекцию искаженного кодового слова можно было бы производить в случае равенства кратности ошибки и кратности Имеющего место отказа, однако с целью повышения- быстродействия использована выдача обратного кода информационной части кодового слова, записанного в регистр 6, через блок 14 на выход 15. По окончании считывания, если схема 23 определит равенство кратности имеющего место отказа и силы используемого кода, вся информация из накопителя I выводится, схема 23 обеспечивает перестройку регистра 24 и блоков 10 и 17 на код, сила которого на S единиц выше силы предыдущего кода, далее осуществляется ввод 1шформации в накопитель I. Если кратность отказа не равна (меньше) силе используемого кода, операции: вывод информации из накопителя I, перестройка регистра 24 и блоков 10 и 17 и ввод информации в накопитель I не производятся, и устройство продолжает использовать прежний код. ПРЩЛЕТ ИЗОБРЕТЕНИЯ Запогушнающее устройство с автономшЛЛ контролем,содержащее накопитель, подсоединенный к регистрам кодового слова, регистр силы корректирущего кода, один из выходов которого подключен к блоку кодирования и блоку декодирования, схему сравнения, один вход которой подсоединен к выходу блока декодироания, а выход - к блоку управлеия, блок схем И и блоки схем ИЛИ, отличающееся ем, что, с целью увеличения эффекивной егужости устройства и повыше ия надежности его работы, оно соержит дополнительную схему сравения, один вход которой подсоедиен к регистру силы корректирующего ода, схему определения кратности тказов, выход которой подсоединен друп™ входагл схем сравнения, а

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1972 |

|

SU448480A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО:1 Т 5•..:' 'Уу | 1973 |

|

SU436388A1 |

| Запоминающее устройство с автономным контролем | 1973 |

|

SU452037A1 |

| Запоминающее устройство с автономным контролем | 1973 |

|

SU444250A1 |

| Запоминающее устройство | 1972 |

|

SU470866A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с самоконтролем | 1975 |

|

SU608202A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

Авторы

Даты

1974-09-15—Публикация

1972-12-14—Подача