Изобретение относится к области запоминающих устройств.

Известно запоминающее устройство, содержащее накопитель, подключенный через адресные формирователи и вентили к регистру адреса и через разрядные формирователи и вентили-к выходам блока кодирования и входам блока декодирования, подсоединенного к блоку управления и выходному регистру, входной регистр, подключенный к информационным входам устройства, и блок схем «ИЛИ.

Недостатком известного устройства является невысокая эффективная емкость устройства.

Предложенное запоминающее устройство отличается от известного тем, что оно содержит схему поразрядного сравнения, входы которой подсоединены к выходам входного н выходного регистров, а выходы - к одним из входов блока схем «ИЛИ, другие входы которого подсоединены к выходам выходного регистра, а выходы - к информационным выходам устройства. Кроме того, другие входы блока схем «ИЛИ подсоединены к выходам введенного в устройство блока схем «И, информационные входы которого соединены с выходами блока декодирования и одними из входов входного регистра.

Указанные отличия позволяют повысить эффективную емкость и надежность работы yci ройства.

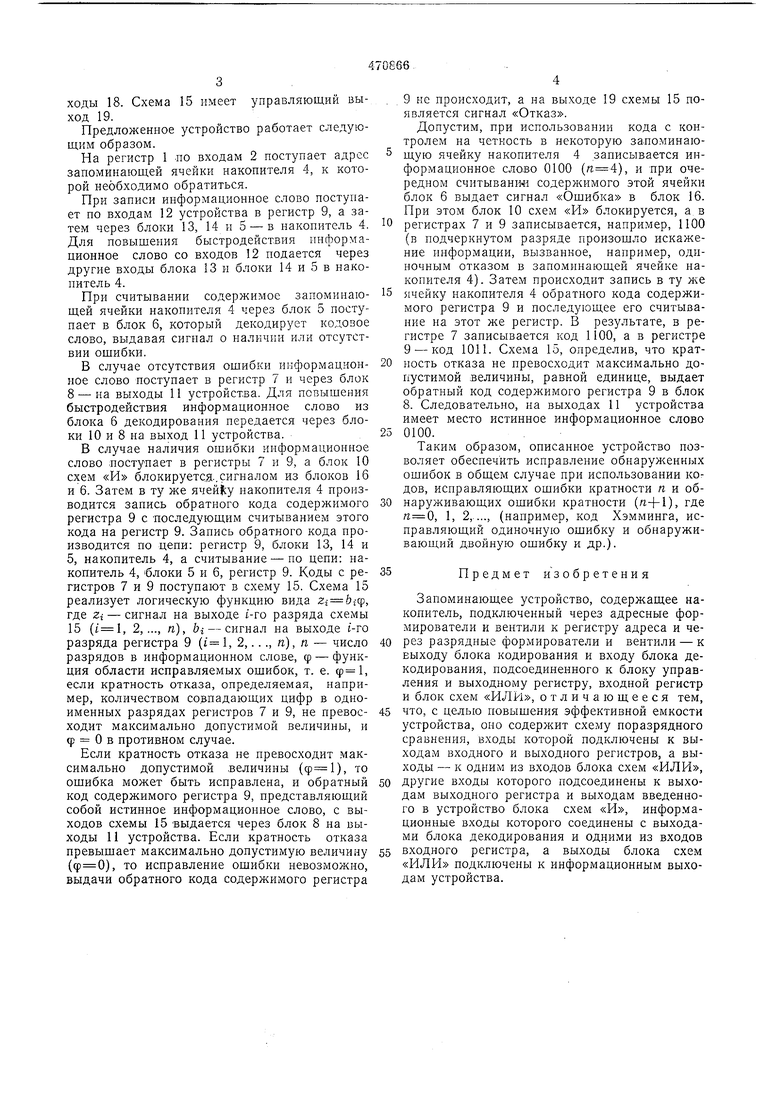

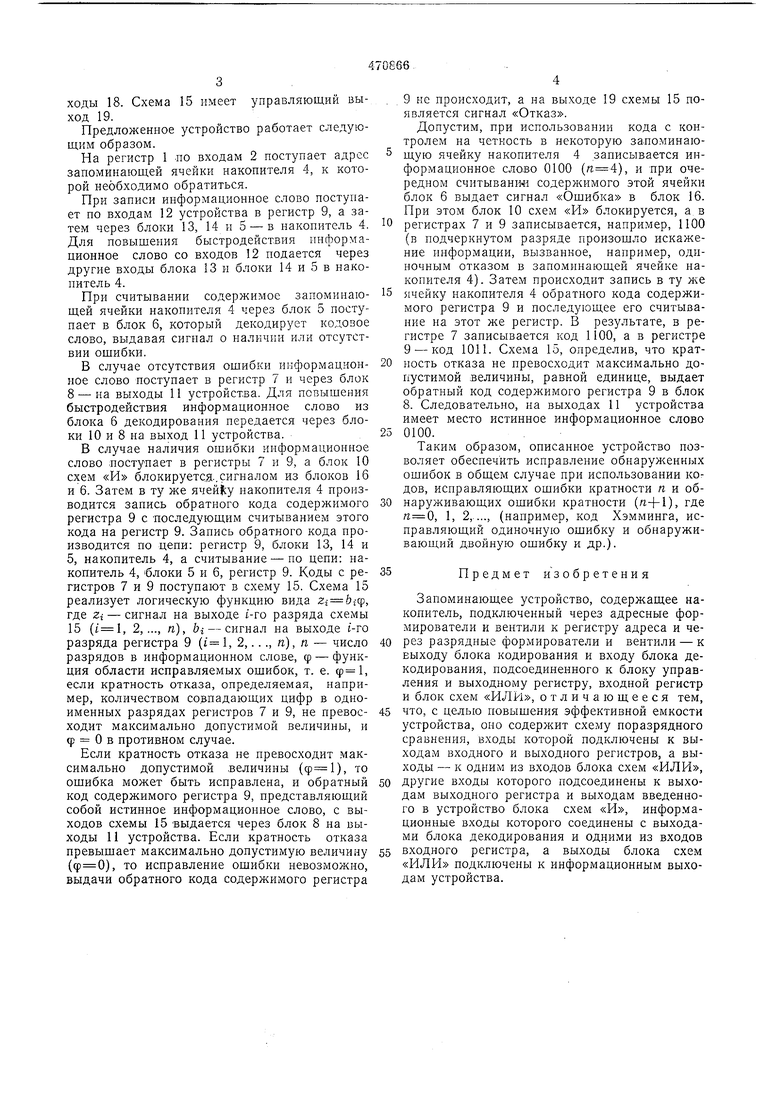

На чертеже изображена блок-схема предлагаемого запоминающего устройства. Устройство содержит регистр 1 адреса с информационными входами 2. Выходы регистра 1 связаны через адресные формирователи и вентили (см. чертеж, блок 3) с накопителем 4. Информационные выходы накопителя через

разрядные формирователи и вентили (см. чертеж, блок 5) соединены со входами блока 6 декодирования. Блок 6 подключен ко входам выходного регистра 7, выходы которого связаны с одним из входов блока 8 схем «ИЛИ,

ко входам входного регистра 9 и через блок 10 схем «И - к другим входам блока 8, выходы которого соединены с информационными выходами 11 устройства. Информационные входы 12 устройства связаны со входами регистра 9 и с одним из входов блока 13 схем «Или, с другими входами которого соединены выходы регистра 9, а выходы блока 13 подключены к блоку 14 кодирования. Выходы блока 14 через блок 5 связаны с информационными входами накопителя 4. Выходы регистров 7 и 9 соединены со .входами схемы 5 поразрядного сравнения, выходы которой подключены к третьим входам блока 8. Регистры 1, 7 и 9, блоки 3, 5, 6 и 10 соединены с блоком

16 управления, который имеет входы 17 и выходы 18. Схема 15 имеет управляющий выход 19.

Предложенное устройство работает следующим образом.

На регистр 1 ло входам 2 поступает адрес запоминающей ячейки накопителя 4, к которой необходимо обратиться.

При записи информационное слово поступает по входам 12 устройства в регистр 9, а затем через блоки 13, 14 и 5 - в накопитель 4. Для повыщения быстродействия информационное слово со входов 12 подается через другие входы блока 13 и блоки 14 и 5 в накопитель 4.

При считывании содержимое запоминающей ячейки накопителя 4 через блок 5 поступает в блок 6, который декодирует кодовое слово, выдавая сигнал о наличии или отсутствии ощибки.

В случае отсутствия ощибки информационное слово поступает в регистр 7 и через блок 8 - на выходы 11 устройства. Для повыщения быстродействия информационное слово из блока 6 декодирования передается через блоки 10 и 8 на выход 11 устройства.

В случае наличия ошибки информационное слово поступает в регистры 7 и 9, а блок 10 схем «И блокируется..сигналом из блоков 16 и 6. Затем в ту же ячейку накопителя 4 производится запись обратного кода содержимого регистра 9 с последующим считыванием этого кода на регистр 9. Занись обратного кода производится по цепи: регистр 9, блоки 13, 14 и 5, накопитель 4, а считывание - по цепи: накопитель 4, «блоки 5 и 6, регистр 9. Коды с регистров 7 и 9 поступают в схему 15. Схема 15 реализует логическую функцию вида 2, bicp, где Zi - сигнал на выходе i-ro разряда схемы 15 (, 2,..., п), Ьг - сигнал на выходе с-го разряда регистра 9 (i 1, 2,.. ., п), п - число разрядов в информационном слове, ф - функция области исправляемых ощибок, т. е. , если кратность отказа, определяемая, например, количеством совпадающих цифр в одноименных разрядах регистров 7 и 9, не превосходит максимально допустимой величины, и Ф О в противном случае.

Если кратность отказа не превосходит .максимально допустимой величины (), то ощибка может быть исправлена, и обратный код содержимого регистра 9, представляющий собой истинное информационное слово, с выходов схемы 15 выдается через блок 8 на выходы 11 устройства. Если кратность отказа превыщает максимально допустимую величину (), то исправление ощибки невозможно, выдачи обратного кода содержимого регистра

9 не происходит, а на выходе 19 схемы 15 появляется сигнал «Отказ.

Допустим, при использовании кода с контролем на четкость в некоторую запоминающую ячейку накопителя 4 записывается информационное слово 0100 (), и при очередном считываний содержимого этой ячейки блок 6 выдает сигнал «Ощибка в блок 16. При этом блок 10 схем «И блокируется, а в

регистрах 7 и 9 записывается, например, 1100 (в подчеркнутом разряде произошло искажение информации, вызванное, например, одиночным отказом в запоминающей ячейке накопителя 4). Затем происходит запись в ту же

ячейку накопителя 4 обратного кода содержимого регистра 9 и последующее его считывание на этот же регистр. В результате, в регистре 7 записывается код 1100, а в регистре 9 - код 1011. Схема 15, определив, что кратность отказа не превосходит максимально допустимой величины, равной единице, выдает обратный код содержимого регистра 9 в блок 8. Следовательно, на выходах 11 устройства имеет место истинное информационное слово

0100.

Таким образом, описанное устройство позволяет обеспечить исправление обнаруженных ощибок в общем случае при использовании кодов, исправляющих ощибки кратности п и обнаруживающих ощибки кратности (п+1), где , 1, 2,...., (например, код Хэ.мминга, исправляющий одиночную ощибку и обнаруживающий двойную ошибку и др.).

Предмет изобретения

Запоминающее устройство, содержащее накопитель, подключенный через адресные формирователи и вентили к регистру адреса и через разрядные формирователи и вентили - к выходу блока кодирования и входу блока декодирования, подсоединеииого к блоку управления и выходному регистру, входной регистр и блок схем «ИЛИ, отличающееся тем,

что, с целью новыщения эффективной емкости устройства, оно содержит схему поразрядного сравнения, входы которой подключены к выходам входного и выходного регистров, а выходы - к одним из входов блока схем «ИЛИ,

другие входы которого подсоединены к вы.ходам выходного регистра и выходам введенного в устройство блока схем «И, инфор.мационные входы которого соединены с выходами блока декодирования и одними из входов

входного регистра, а выходы блока схем «ИЛИ цодключены к информационным выходам устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1973 |

|

SU452037A1 |

| Запоминающее устройство с самоконтролем | 1975 |

|

SU608202A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО:1 Т 5•..:' 'Уу | 1973 |

|

SU436388A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU903990A1 |

| Запоминающее устройство с самоконтролем | 1979 |

|

SU855730A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1081669A1 |

| Запоминающее устройство с автономным контролем | 1978 |

|

SU780049A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с коррекцией ошибок | 1978 |

|

SU744740A1 |

Авторы

Даты

1975-05-15—Публикация

1972-03-21—Подача