1

Известно буферное запоминающее устройство, содержащее накопители, входы которых подключены к дешифратору адреса, а выходы- к одним входам схем выделения сигналов, коммутатор, выходы которого подсоединены к входам дешифратора адреса, а первые входы - к одному из датчиков адреса, делители частоты, схемы формирования контрольных символов, ключевые схемы, входы которых соединены с шинами обращения, схемы выделения сигналов.

Цель изобретения - увеличение эффективности емкости устройства.

Предлагаемое буферное запоминающее устройство отличается от известного тем, что в него введены инверторы по количеству выходов датчика адреса, входы которых подключены к выходам другого датчика адреса, а выходы- ко вторым входам коммутатора, схемы «ИЛИ, одни входы которых подсоединены соответственно к выходам ключевых схем и к входным щинам устройства, другие входы - к выходам делителей частоты и схем формирования контрольных символов, а выходы - к входам датчиков адреса и накопителей, выходы делителей частоты подключены соответственно к входам схем формирования контрольных символов и к входам схем выделения сигналов, выходы которых подсоединены к выходным шинам устройства.

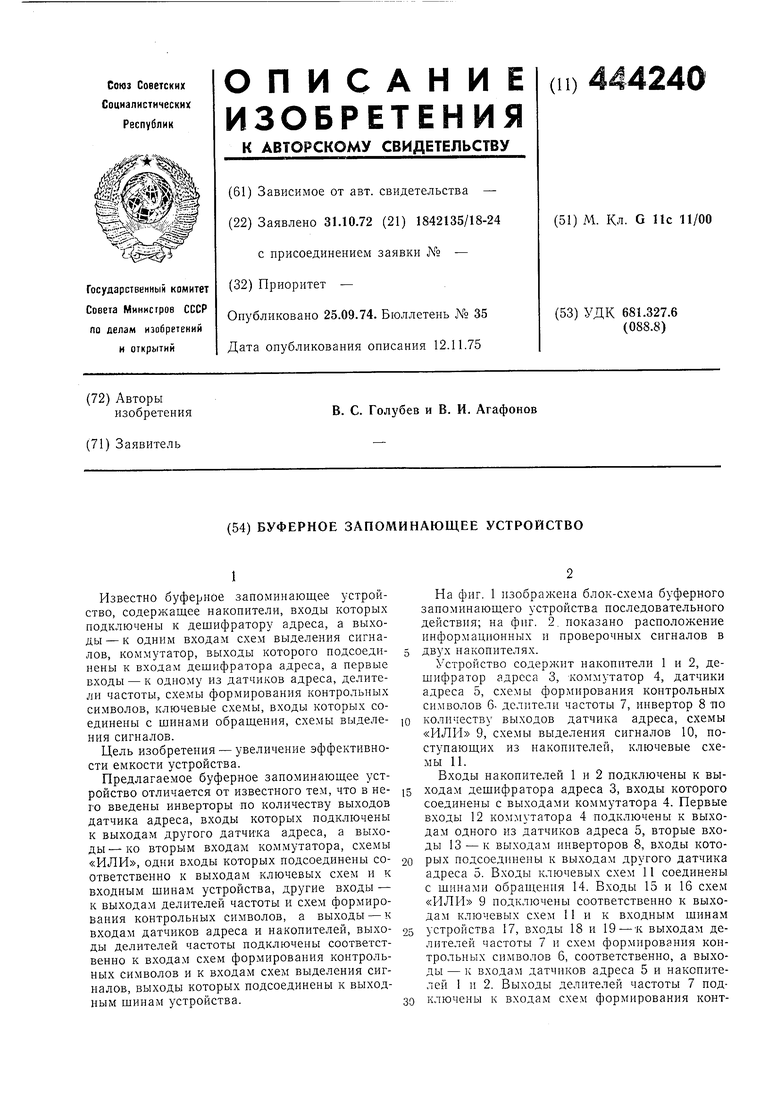

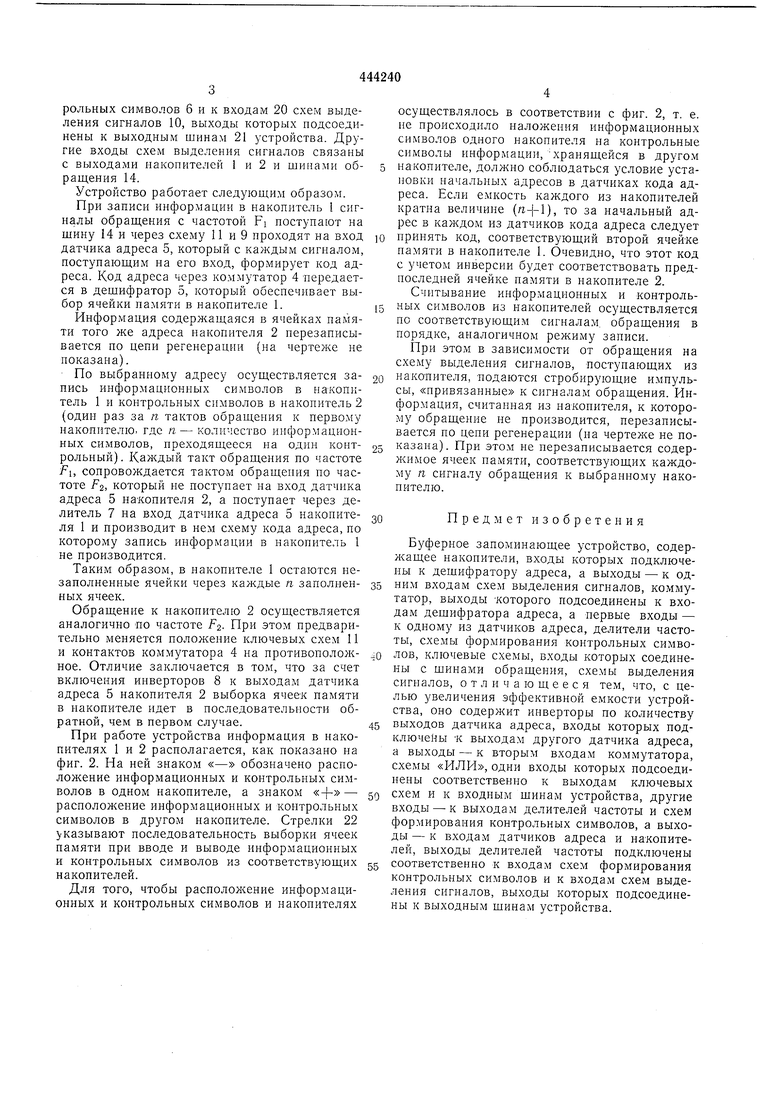

На фиг. 1 изображена блок-схема буферного запоминающего устройства последовательного действия; на фиг. 2, показано расположение информационных и проверочных сигналов в

двух накопителях.

Устройство содерлчит накопители 1 и 2, дешифратор адреса 3, коммутатор 4, датчики адреса 5, схемы формирования контрольных символов 6 делители частоты 7, инвертор 8 -по

количеству выходов датчика адреса, схемы «ИЛИ 9, схемы выделения сигналов 10, поступающих из накопителей, ключевые схемы 11. Входы накопителей 1 и 2 подключены к выходам дешифратора адреса 3, входы которого соединены с выходами коммутатора 4. Первые входы 12 коммутатора 4 подключены к выходам одного из датчиков адреса 5, вторые входы 13 - к выходам инверторов 8, входы которых подсоединены к выходам другого датчика адреса 5. Входы ключевых схем 11 соединены с шинами обран;ення 14. Входы 15 и 16 схем «ИЛИ 9 подключены соответственно к выходам ключевых схем 11 и к входным шинам

устройства 17, входы 18 и 19-к выходам делителей частоты 7 и схем формирования контрольных символов 6, соответственно, а выходы - к входам датчиков адреса 5 и накопителей 1 и 2. Выходы делителей частоты 7 подключены к входам схем формирования контрольных символов 6 и к входам 20 схем выделения сигналов 10, выходы которых подсоединены к выходным шинам 21 устройства. Другие входы схем выделения сигналов связаны с выходами накопителей 1 и 2 и шинами обращения 14.

Устройство работает следуюидим образом.

При записи информации в накопитель 1 сигналы обращения с частотой FI поступают на щину 14 и через схему 11 и 9 проходят на вход датчика адреса 5, который с каждым сигналом, поступающим на его вход, формирует код адреса. Код адреса через коммутатор 4 передается в дешифратор 5, который обеспечивает выбор ячейки па.мяти в накопителе 1.

Информация содержащаяся в ячейках памяти того же адреса накопителя 2 перезаписывается по цепи регенерации (на чертеже не показана).

По выбранному адресу осуществляется запись информационных символов в накопитель 1 и контрольных символов в накопитель 2 (один раз за п тактов обращения к первому накопителю, где п - количество информационных символов, преходящееся на один контрольный). Каждый такт обращения по частоте F, сопровождается тактом обращепия по частоте F, который не поступает на вход датчика адреса 5 накопителя 2, а поступает через делитель 7 на вход датчика адреса 5 накопителя 1 и производит в нем схему кода адреса, по которому запись информации в накопитель 1 не производится.

Таким образом, в накопителе 1 остаются незаполненные ячейки через каждые п заполненных ячеек.

Обращение к накопителю 2 осуществляется аналогично по частоте РЧ. При этом предварительно меняется положение ключевых схем 11 и контактов коммутатора 4 на противоположное. Отличие заключается в том, что за счет включения инверторов 8 к выходам датчика адреса 5 накопителя 2 выборка ячееК памяти в пакопителе идет в поеледовательности обратной, чем в первом случае.

При работе устройства информация в накопителях 1 и 2 располагается, как показано на фиг. 2. На ней знаком «- обозначено расположение информационных и контрольных символов в одном накопителе, а знаком «-|- - расположение информационных и контрольных символов в другом накопителе. Стрелки 22 указывают последовательность выборки ячеек памяти при вводе и выводе информационных

и контрольных символов из соответствующих

накопителей.

Для того, чтобы расположение информационных и контрольных символов и накопителях

осуществлялось в соответствии с фиг. 2, т. е. не проиеходило наложения информационных символов одного накопителя на контрольные символы информации,хранящейся в другом накопителе, должно соблюдаться условие установки начальных адресов в датчиках кода адреса. Если емкость каждого из накопителей кратна величине (), то за начальный адрес в каждом из датчиков кода адреса следует принять код, соответствующий второй ячейКе памяти в накопителе 1. Очевидно, что этот код с учетом инверсии будет соответствовать предпоследней ячейке намяти в накопителе 2.

Считывание информационных и контрольных еимволов из накопителей осуществляется по соответствующим сигналам, обращения в порядке, аналогичном режиму записи.

При этом в зависимости от обращения на схему выделения сигналов, поступающих из накопителя, подаются стробирующие импульсы, «привязанные к сигналам обращения. Информация, считанная из накопителя, к которому обращение не производится, перезаписывается по цепи регенерации (на чертеже не показана). При этом не перезаписывается содержимое ячеек намяти, соответствующих каждому п сигналу обращения к выбранному накопителю.

Предмет изобретения

Буферное запоминающее устройство, содержащее накопители, входы которых подключены к дешифратору адреса, а выходы - к одним входам схем выделения сигналов, коммутатор, выходы Которого подсоединены к входам дещифратора адреса, а первые входы - к одному из датчиков адреса, делители частоты, схемы формирования контрольных символов, ключевые схемы, входы которых соединены с шинами обращения, схемы выделения сигналов, отличающееся тем, что, с целью увеличения эффективной емкости устройства, оно содержит инверторы по количеству выходов датчика адреса, входы которых подключены К выходам другого датчика адреса, а выходы - к вторым входам коммутатора, схемы «ИЛИ, одни входы которых подсоединены соответственно к выходам ключевых схем и к входным шинам устройства, другие входы - к выходам делителей частоты и схем формирования контрольных символов, а выходы - к входам датчиков адреса и накопителей, выходы делителей частоты подключены соответственно к входам схем формирования контрольных символов и к входам схем выделения сигналов, выходы которых подсоединены к выходным шинам устройства.

21

21

Фиг1

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1977 |

|

SU733017A1 |

| Запоминающее устройство | 1978 |

|

SU743031A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКОВ ДИСКРЕТНЫХ СИГНАЛОВ | 1992 |

|

RU2040118C1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство для отображения информации | 1982 |

|

SU1042069A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| УПРАВЛЯЮЩАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2520350C2 |

| Запоминающее устройство | 1981 |

|

SU1010653A1 |

| Устройство для программного контроля электронных устройств | 1979 |

|

SU868775A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1107173A1 |

4--I--(-+- -h-l---- + + + - -I--f 4-- -h i-+

Фиг 2

22

Авторы

Даты

1974-09-25—Публикация

1972-10-31—Подача